Hey guys,

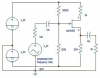

Ive been tring (over the past week) to try and get a p-channel amp just work to bias on properly. I can get a n-type to work properly but every time i try the p-type i get no gain on my output.

The text book and my class notes say "the same equations apply" blah blah but i cant get any results in simulation and its giving me headaches.

The equations i have are:

Id = K((Vgs-Vtr)^2)

then you solve for Id and choose the suitable current.

Then check the fet isn't in triode region.

I just cant get any combination to work with the p-type.

Can you guys offer any help. Should the output be on the drain or the source for the p-type?

Cheers

Ive been tring (over the past week) to try and get a p-channel amp just work to bias on properly. I can get a n-type to work properly but every time i try the p-type i get no gain on my output.

The text book and my class notes say "the same equations apply" blah blah but i cant get any results in simulation and its giving me headaches.

The equations i have are:

Id = K((Vgs-Vtr)^2)

then you solve for Id and choose the suitable current.

Then check the fet isn't in triode region.

I just cant get any combination to work with the p-type.

Can you guys offer any help. Should the output be on the drain or the source for the p-type?

Cheers