fadlianturu6

New Member

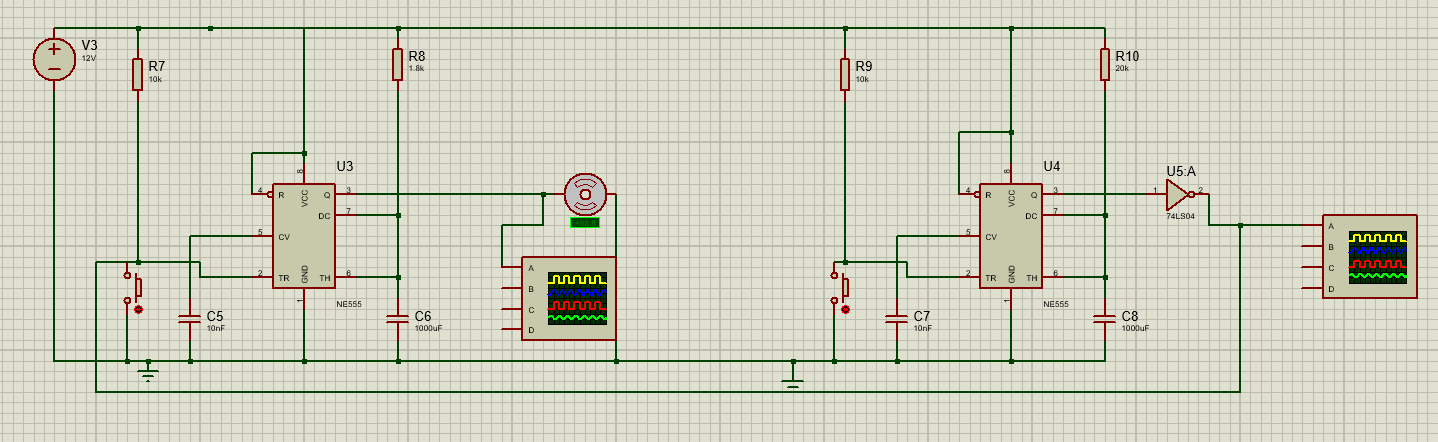

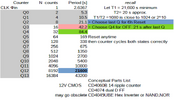

I am new and want to make a compact circuit without a microcontroller. The idea is when you push the button/switch, it will delay the timer for at least 6 hours. After that, it will activate the motor for 20 seconds and loop forever. I am thinking of using a 555 timer with a 1000uF capacitor here, but it fails miserably. Any ideas?