Roff

Well-Known Member

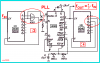

There is one error (on the divide by 4), and one improvement that I would recommend (on the divide by 3). On the divide by 3, the pulse from the AND gate is generated by propagation delays and is therefore narrow. I couldn't find a minimum pulse width spec for the CD4046, so I think the modification I made will be safer.Goldsphere said:Hey that's really awesome! Thanks heaps em2006.

I will try it out as soon as I can.

In the divide by 4, it was a divide by 2, again with a sliver as the pulse to the 4046. I changed it to divide by 4, and fed back a 50% duty cycle to the 4046.

I can't vouch for the correctness of the rest of the circuit.