Logic-wise, yes.

However, that again is an over-simplified diagram and not a real world one.

So - voltage-wise and in practice; no!

If a CMOS input is near mid supply, both the upper and lower transistor it feeds can turn on at the same time. That can cause excess current or possibly oscillation.

Most logic ICs have signal buffers before splitting the signal to different points internally.

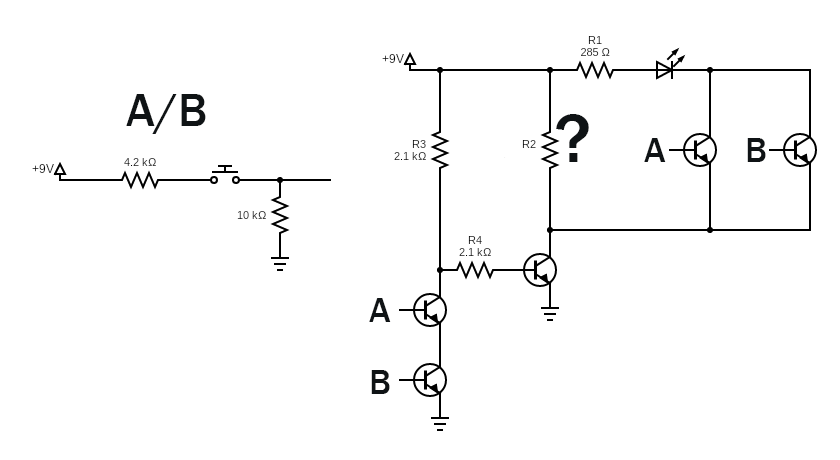

eg. The real internal arrangement of a 4081B AND gate is detailed below; each input directly drives a Complementary pair of MOSFETS.

[The CMOS name comes from the Complementary MOS construction]

The minimum "high" and maximum "low" voltage levels are given in datasheets. Leaving an input in between these levels, near mid supply, is a "real bad thing".. Another application of the "Nothing floating" rule.

The exception is with devices that have schmitt trigger inputs - they can have any voltage within the supply range, but only "switch" when it's above the high threshold or below the low threshold.

Good for debounce, timing circuits, oscillators etc.

See eg. 40106 and 4093 for CMOS examples of those.