kalemaxon89

New Member

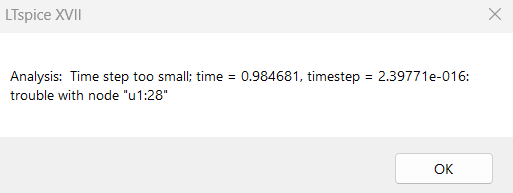

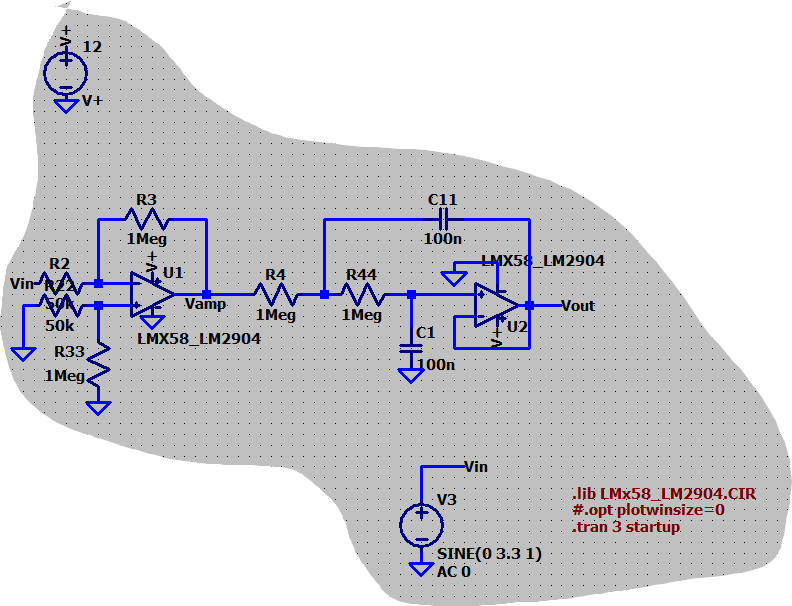

I want to simulate the attached circuit but the following error occurs:

(the wheatstone bridge is unplugged and I don't use it)

Where do I change in the settings the timestep?

I searched but I don't know where it is. I went to the simulation control panel and there are so many parameters: Gmin, Abstol, Reltol etc. does anyone know how to fix it?

I tried putting ESR to each capacitor, but same error.

I am attaching the .asc file.

(the wheatstone bridge is unplugged and I don't use it)

Where do I change in the settings the timestep?

I searched but I don't know where it is. I went to the simulation control panel and there are so many parameters: Gmin, Abstol, Reltol etc. does anyone know how to fix it?

I tried putting ESR to each capacitor, but same error.

I am attaching the .asc file.