AtomSoft

Well-Known Member

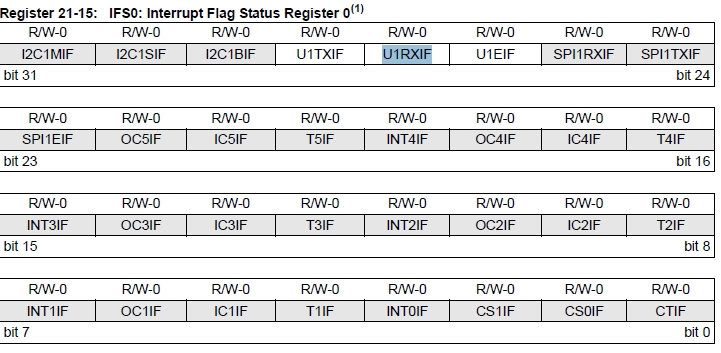

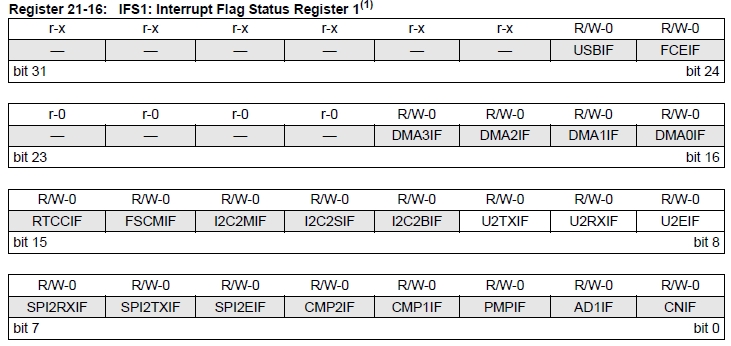

Hey im using the PIC32MX250F128D processor and noticed IFSx are switched:

IFS0bits are supposed to be in IFS1 or at least thats what my datasheet states.

For instance : U1RXIF is in IFS1 when its supposed to be in IFS0

Or is this a DATASHEET MISTAKE?

Which is CORRECT?

How do i tell Microchip about this?

Why hasnt anyone else noticed this? (im sure im not the only guy using this MCU)

Im using XC32 1.31

Code:

extern volatile unsigned int IFS0 __attribute__((section("sfrs")));

typedef union {

struct {

unsigned CTIF:1;

unsigned CS0IF:1;

unsigned CS1IF:1;

unsigned INT0IF:1;

unsigned T1IF:1;

unsigned IC1EIF:1;

unsigned IC1IF:1;

unsigned OC1IF:1;

unsigned INT1IF:1;

unsigned T2IF:1;

unsigned IC2EIF:1;

unsigned IC2IF:1;

unsigned OC2IF:1;

unsigned INT2IF:1;

unsigned T3IF:1;

unsigned IC3EIF:1;

unsigned IC3IF:1;

unsigned OC3IF:1;

unsigned INT3IF:1;

unsigned T4IF:1;

unsigned IC4EIF:1;

unsigned IC4IF:1;

unsigned OC4IF:1;

unsigned INT4IF:1;

unsigned T5IF:1;

unsigned IC5EIF:1;

unsigned IC5IF:1;

unsigned OC5IF:1;

unsigned AD1IF:1;

unsigned FSCMIF:1;

unsigned RTCCIF:1;

unsigned FCEIF:1;

};

struct {

unsigned w:32;

};

} __IFS0bits_t;

extern volatile __IFS0bits_t IFS0bits __asm__ ("IFS0") __attribute__((section("sfrs")));

extern volatile unsigned int IFS0CLR __attribute__((section("sfrs")));

extern volatile unsigned int IFS0SET __attribute__((section("sfrs")));

extern volatile unsigned int IFS0INV __attribute__((section("sfrs")));

extern volatile unsigned int IFS1 __attribute__((section("sfrs")));

typedef union {

struct {

unsigned CMP1IF:1;

unsigned CMP2IF:1;

unsigned CMP3IF:1;

unsigned USBIF:1;

unsigned SPI1EIF:1;

unsigned SPI1RXIF:1;

unsigned SPI1TXIF:1;

unsigned U1EIF:1;

unsigned U1RXIF:1;

unsigned U1TXIF:1;

unsigned I2C1BIF:1;

unsigned I2C1SIF:1;

unsigned I2C1MIF:1;

unsigned CNAIF:1;

unsigned CNBIF:1;

unsigned CNCIF:1;

unsigned PMPIF:1;

unsigned PMPEIF:1;

unsigned SPI2EIF:1;

unsigned SPI2RXIF:1;

unsigned SPI2TXIF:1;

unsigned U2EIF:1;

unsigned U2RXIF:1;

unsigned U2TXIF:1;

unsigned I2C2BIF:1;

unsigned I2C2SIF:1;

unsigned I2C2MIF:1;

unsigned CTMUIF:1;

unsigned DMA0IF:1;

unsigned DMA1IF:1;

unsigned DMA2IF:1;

unsigned DMA3IF:1;

};

struct {

unsigned w:32;

};

} __IFS1bits_t;

extern volatile __IFS1bits_t IFS1bits __asm__ ("IFS1") __attribute__((section("sfrs")));

extern volatile unsigned int IFS1CLR __attribute__((section("sfrs")));

extern volatile unsigned int IFS1SET __attribute__((section("sfrs")));

extern volatile unsigned int IFS1INV __attribute__((section("sfrs")));IFS0bits are supposed to be in IFS1 or at least thats what my datasheet states.

For instance : U1RXIF is in IFS1 when its supposed to be in IFS0

Or is this a DATASHEET MISTAKE?

Which is CORRECT?

How do i tell Microchip about this?

Why hasnt anyone else noticed this? (im sure im not the only guy using this MCU)

Im using XC32 1.31