DerStrom8

Super Moderator

Hi all,

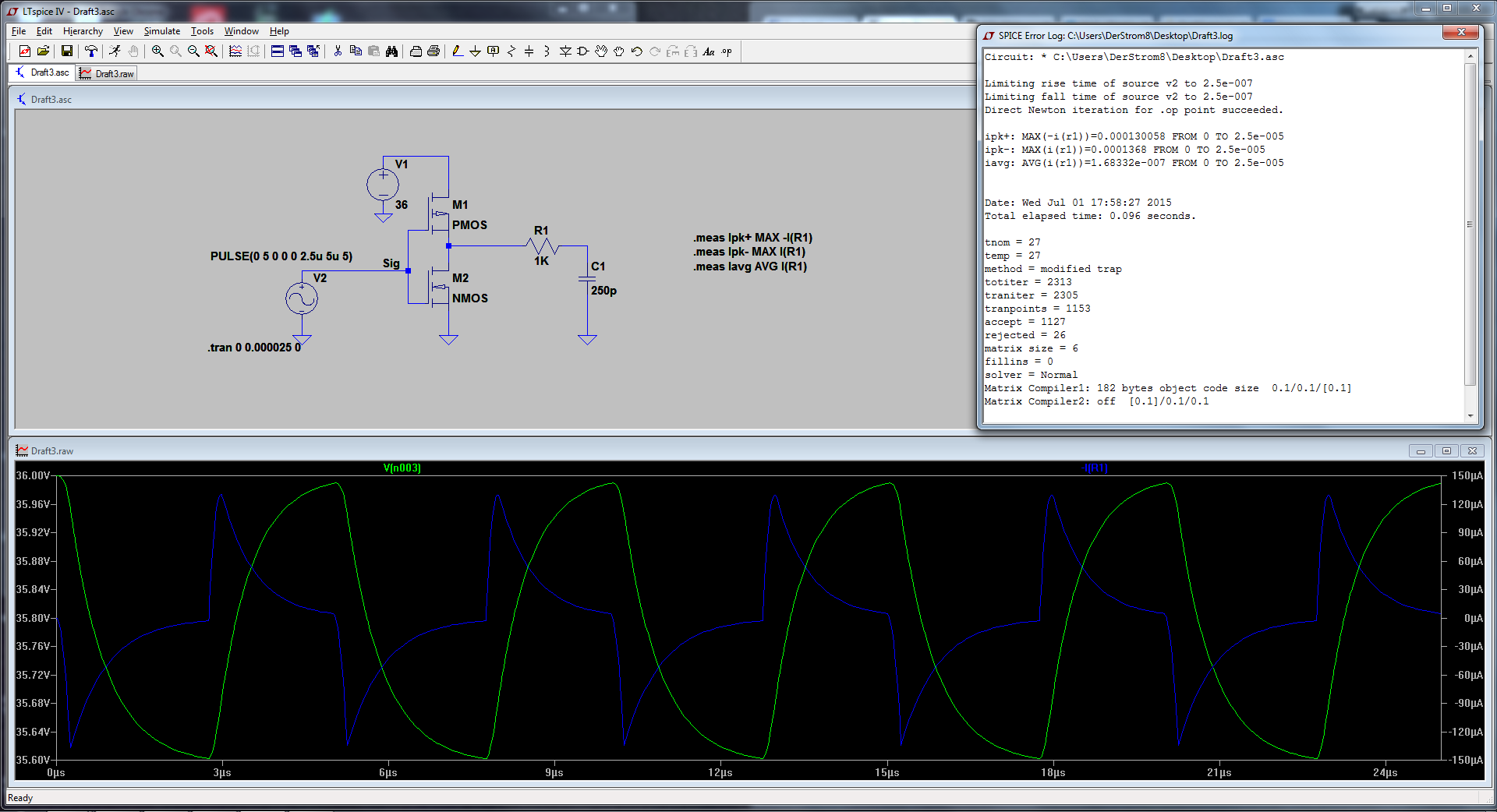

First of all I'm going to mention that I very rarely use LTSpice. Usually I use Multisim or Proteus.

I have the following project that was handed to me by another engineer at work. He was having trouble with it so he wanted me to give it a try.

(I am attaching the .asc file as well, for those of you who have LTSpice installed)

I am uncertain about the values I'm getting for Ipk (both + and -). I would expect Iavg to be close to zero (which it is).

Effectively I need to determine the peak current through R1 and calculate the power being dissipated by it so that we can decide which size to use in the new board design. I can't really go into detail on what it is, but you'll have to trust me that the circuit is correct.

V1 is a 36V DC power supply.

V2 is a 200kHz square wave with a 5V amplitude. I do not have any information about the rise/fall times, so I am assuming a perfect square wave.

The two MOSFETs are representing the output stage of a Microchip HV574 (**broken link removed**). I have left out the freewheel diodes.

Can anyone spot any mistakes? The values I'm looking for are:

Ipk(+)(R1)

Ipk(-)(R1)

Iavg(R1)

P(r1)

Thanks folks!

Matt

First of all I'm going to mention that I very rarely use LTSpice. Usually I use Multisim or Proteus.

I have the following project that was handed to me by another engineer at work. He was having trouble with it so he wanted me to give it a try.

(I am attaching the .asc file as well, for those of you who have LTSpice installed)

I am uncertain about the values I'm getting for Ipk (both + and -). I would expect Iavg to be close to zero (which it is).

Effectively I need to determine the peak current through R1 and calculate the power being dissipated by it so that we can decide which size to use in the new board design. I can't really go into detail on what it is, but you'll have to trust me that the circuit is correct.

V1 is a 36V DC power supply.

V2 is a 200kHz square wave with a 5V amplitude. I do not have any information about the rise/fall times, so I am assuming a perfect square wave.

The two MOSFETs are representing the output stage of a Microchip HV574 (**broken link removed**). I have left out the freewheel diodes.

Can anyone spot any mistakes? The values I'm looking for are:

Ipk(+)(R1)

Ipk(-)(R1)

Iavg(R1)

P(r1)

Thanks folks!

Matt

.

.