Hi frnds,

am doing project , variable frequency of 3 phase iinduction motor.

succesfully i generated 3 spwm frequency which is 120 deg phase each other.by arduino uno (atmega328 uc) using 3 phase DDS(sine look uptable,timer,interrupt)

SPWM freq is 33khz (carrier frequency).

in order to verify the output of spwm pulses.

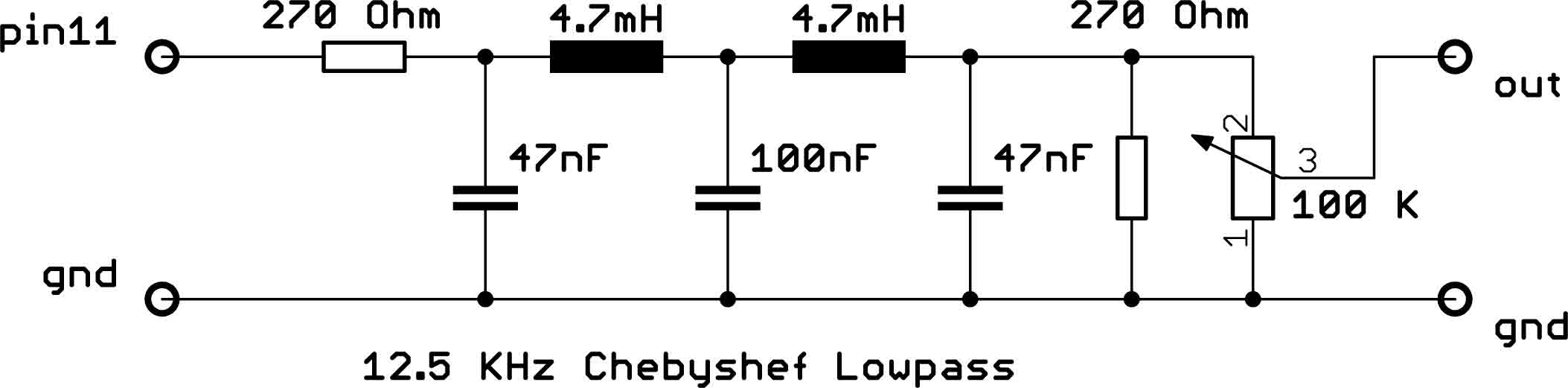

output of spwm pulses is fed into 12.5khz low pass chebsyc filter.

filter circuit given below

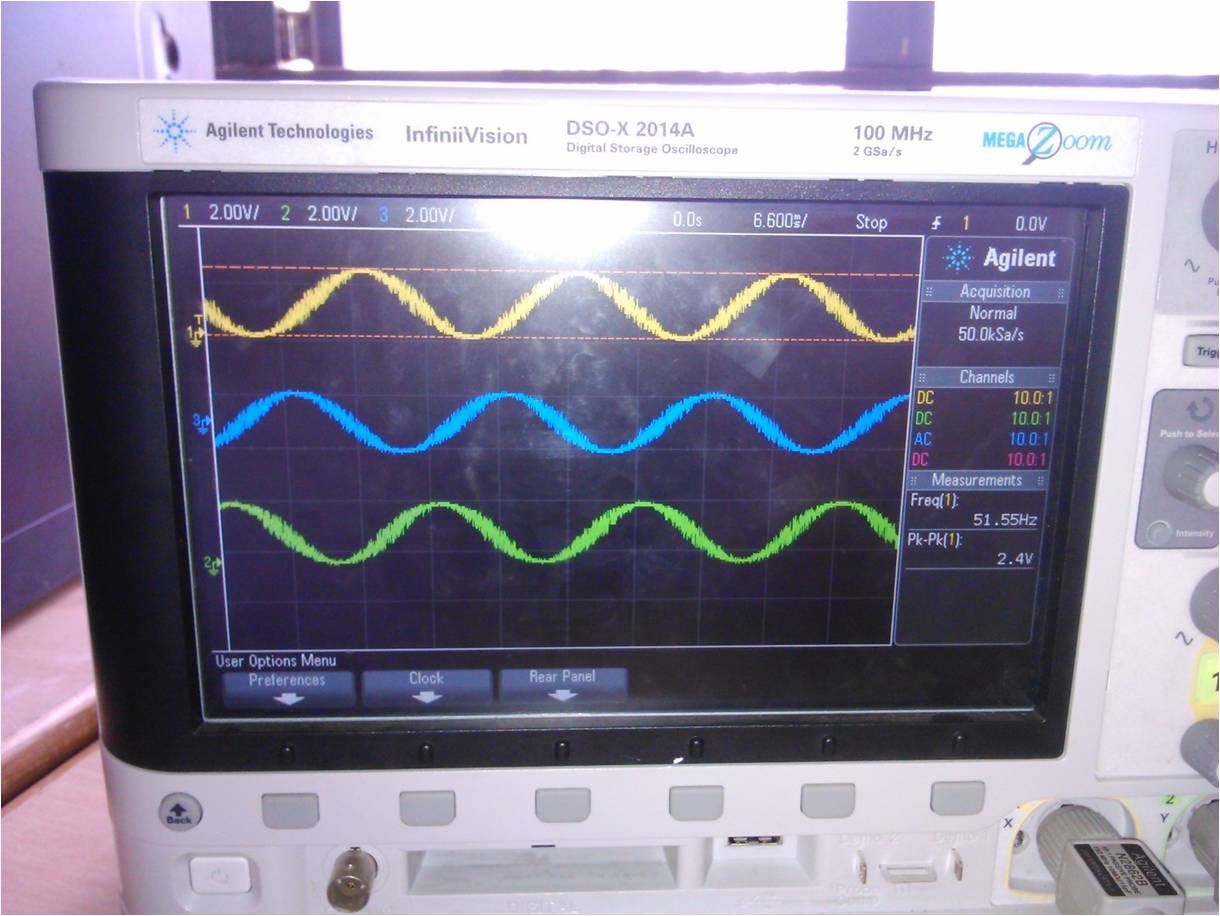

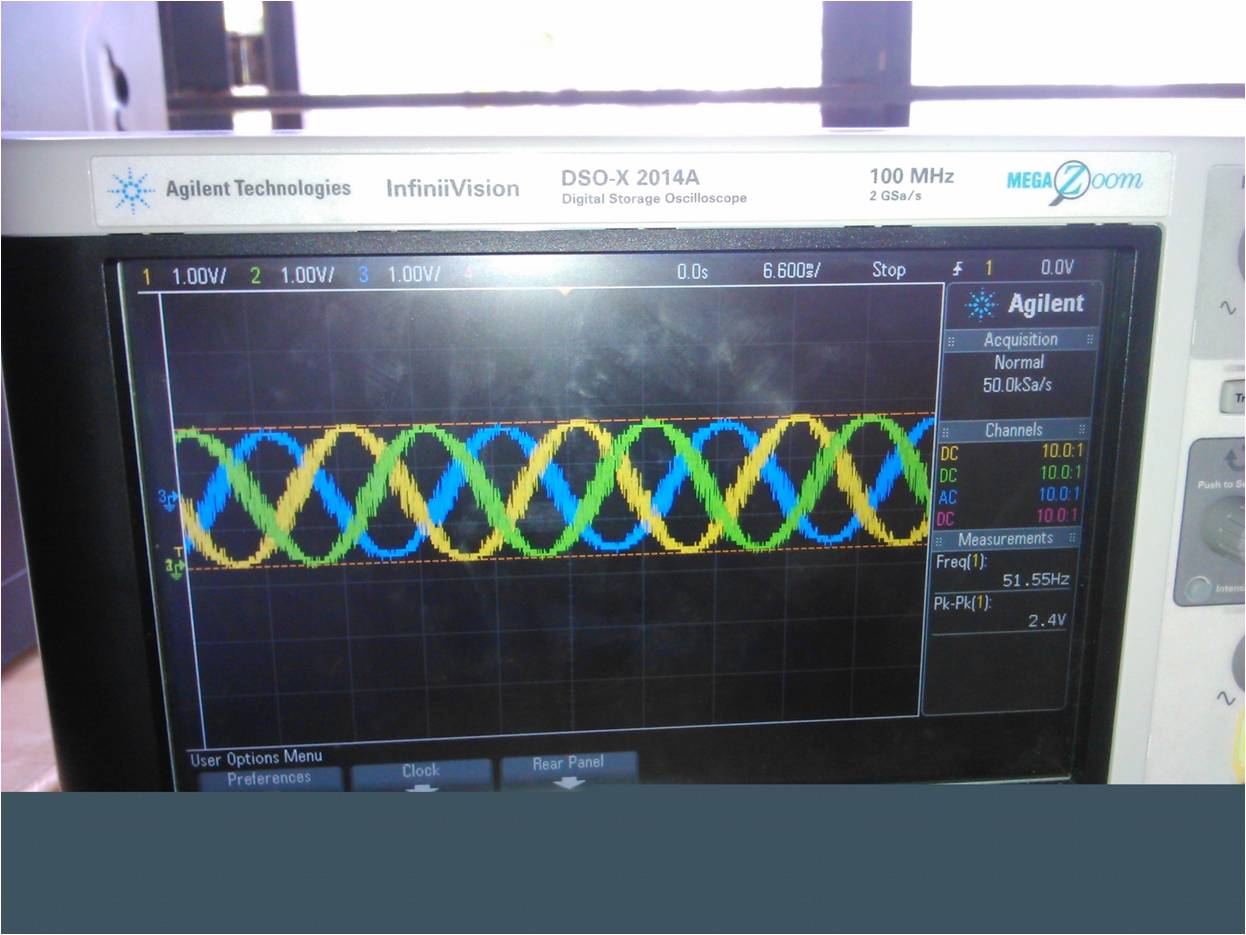

output of filter in dso is

also the freq can vary from 0 -1023hz.

nw i wan to make dead time ckt and invert of 3pulses, so total 6 pulses to 3 phase inverter (6 igbt).

dead time required is 1 or 2us

i wana to make circuit using NOT gate to invert 3 pulses , then R C to provide time constant, then logic gate and schmit trigger

pls help me

am doing project , variable frequency of 3 phase iinduction motor.

succesfully i generated 3 spwm frequency which is 120 deg phase each other.by arduino uno (atmega328 uc) using 3 phase DDS(sine look uptable,timer,interrupt)

SPWM freq is 33khz (carrier frequency).

in order to verify the output of spwm pulses.

output of spwm pulses is fed into 12.5khz low pass chebsyc filter.

filter circuit given below

output of filter in dso is

also the freq can vary from 0 -1023hz.

nw i wan to make dead time ckt and invert of 3pulses, so total 6 pulses to 3 phase inverter (6 igbt).

dead time required is 1 or 2us

i wana to make circuit using NOT gate to invert 3 pulses , then R C to provide time constant, then logic gate and schmit trigger

pls help me