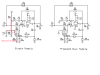

I would like to convert the single supply AGC circuit on the left, to a dual supply circuit. The right is my proposed circuit. I would appreciate your thoughts about the dual supply circuit.

I removed the R1,R5 voltage divider and grounded. I also added the negative supply.

Thank you

I removed the R1,R5 voltage divider and grounded. I also added the negative supply.

Thank you