URGENT HELP PLEASE!!!

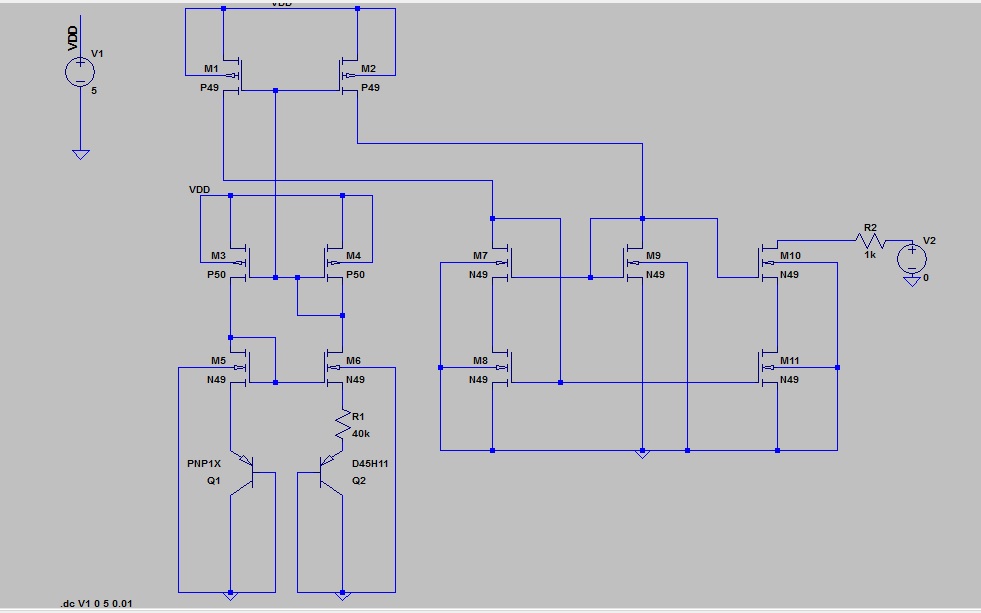

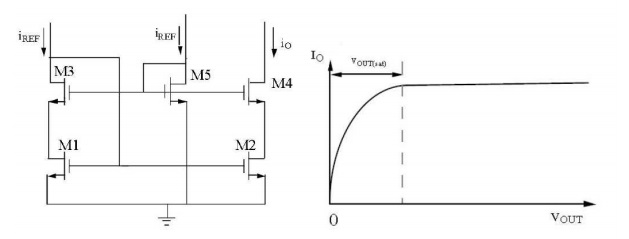

I want to design a wide swing cascode current mirror (question-left) and in order to apply Iref, I have designed a PTAT and applied it to M7 and M9 (design). Iref must be 50uA and the diagram of output should be like the diagram in picture (question-right).

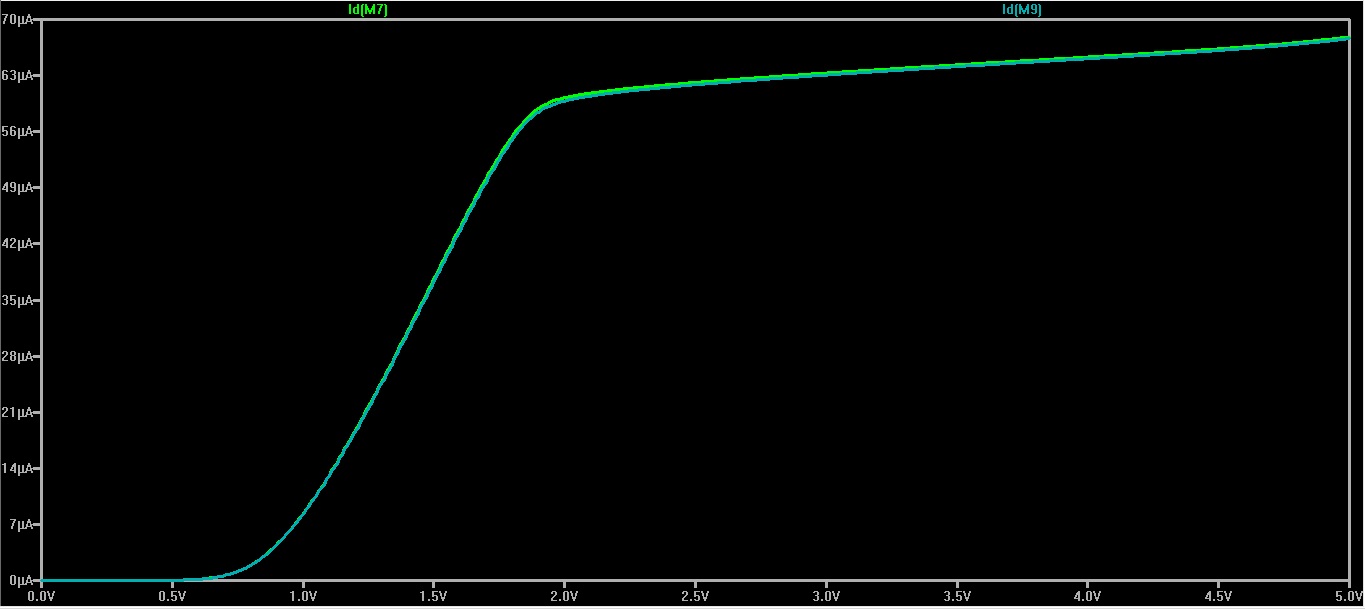

The problem is that, When I do simulation, I have I=0 for V<0.6 and it gradually increases (pic3), while it shouldn't be like this. I don't know in which part I'm designing wrong and I don't know how to solve it. would you please help me urgently????

Thanks in advance.

I want to design a wide swing cascode current mirror (question-left) and in order to apply Iref, I have designed a PTAT and applied it to M7 and M9 (design). Iref must be 50uA and the diagram of output should be like the diagram in picture (question-right).

The problem is that, When I do simulation, I have I=0 for V<0.6 and it gradually increases (pic3), while it shouldn't be like this. I don't know in which part I'm designing wrong and I don't know how to solve it. would you please help me urgently????

Thanks in advance.

Last edited: