Hi all,

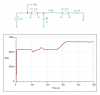

I'm trying to simulate a TDR based on the figure below, and one of the scenarios is a short circuit. The simulation should last for 140ns.

The parameters are

ZA = 50 Ω

TA = 5 ns

ZB = 75 Ω

TB = 10 ns

Rise time of source signal τr = 0.1 ns

I took this website as reference to come up with the schematic below:

As nothing about the voltage source was given other than the rise time, I didn't really know what to put as its parameters, so I took most of the parameters given in the reference website.

I then probed the wire between R2 and TL-A to get the graph.

First of all, is my simulation even correct? This is the first time I'm using LTSpice, and I'm completely new to this electronics topic.

Second, as I've only seen TDR with one transmission line, I'm not sure how to interpret the graph.

a) I thought this circuit is similar to 3 resistors in series - R2 (50 Ω), ZA (50 Ω) and ZB (75 Ω). So shouldn't the incident voltage at the point between R2 and TL-A be 50/(50+50+75)=0.571V?

b) I understand that the time taken for the signal to come back to the probe point is twice the transmission delay. Isn't this the case be it 1 or 2 transmission lines?

At the probe point, I thought it takes 2(5ns + 10ns) = 30ns for the reflected signal to first reach the probe point, meaning the voltage level at that point is constant until 30ns? Why is the voltage level changing at 10ns already, and for it to actually increase?

c) Why are the next voltage level changes at time intervals of 20ns? Why not at multiples of 30ns?

Thank you.

I'm trying to simulate a TDR based on the figure below, and one of the scenarios is a short circuit. The simulation should last for 140ns.

The parameters are

ZA = 50 Ω

TA = 5 ns

ZB = 75 Ω

TB = 10 ns

Rise time of source signal τr = 0.1 ns

I took this website as reference to come up with the schematic below:

As nothing about the voltage source was given other than the rise time, I didn't really know what to put as its parameters, so I took most of the parameters given in the reference website.

I then probed the wire between R2 and TL-A to get the graph.

First of all, is my simulation even correct? This is the first time I'm using LTSpice, and I'm completely new to this electronics topic.

Second, as I've only seen TDR with one transmission line, I'm not sure how to interpret the graph.

a) I thought this circuit is similar to 3 resistors in series - R2 (50 Ω), ZA (50 Ω) and ZB (75 Ω). So shouldn't the incident voltage at the point between R2 and TL-A be 50/(50+50+75)=0.571V?

b) I understand that the time taken for the signal to come back to the probe point is twice the transmission delay. Isn't this the case be it 1 or 2 transmission lines?

At the probe point, I thought it takes 2(5ns + 10ns) = 30ns for the reflected signal to first reach the probe point, meaning the voltage level at that point is constant until 30ns? Why is the voltage level changing at 10ns already, and for it to actually increase?

c) Why are the next voltage level changes at time intervals of 20ns? Why not at multiples of 30ns?

Thank you.