Hello,

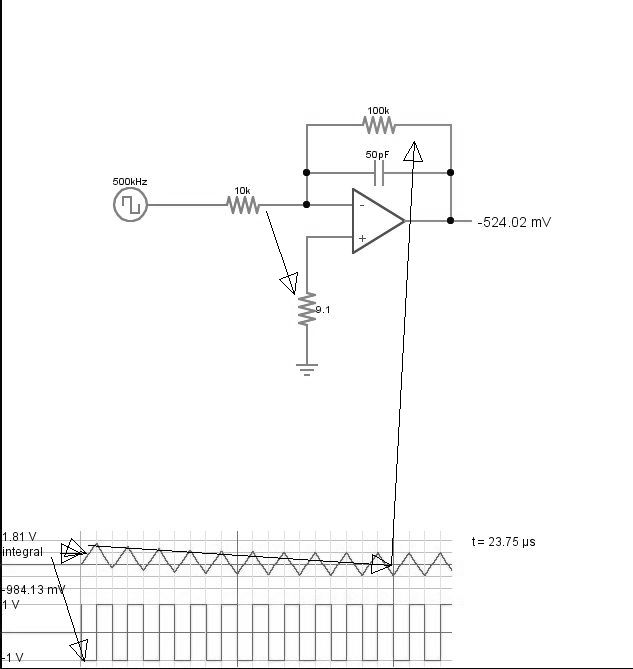

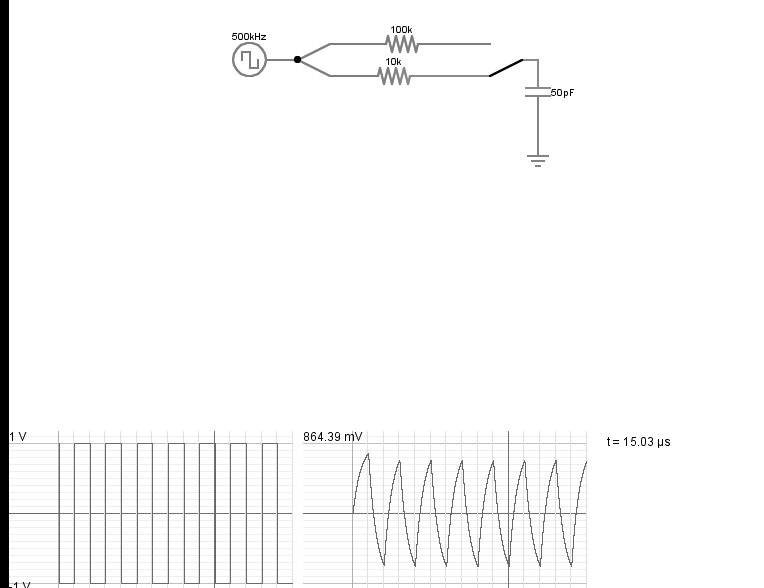

I'm very new to analog design and I'm trying to design an integrator. The integrator should be able to integrate a 10MHz signal and it should have very low noise. I was looking at a couple of opamps and I came across AD8066. It has very low input bias current, low noise, high 3dB BW and slew rate. I also considered OPA2355 (Probably better than AD8066?). I settled on AD8066 because I couldn't run transient simulations on OPA2355. (Don't know why, but kept failing) I used LTSpice to run the simulations. The integrator seems to work but I'm a little confused by the transient response. I have attached a .asc file.

Could anyone please help me with the design? Are there general set of design rules that can be followed for any integrator design?

I'm very new to analog design and I'm trying to design an integrator. The integrator should be able to integrate a 10MHz signal and it should have very low noise. I was looking at a couple of opamps and I came across AD8066. It has very low input bias current, low noise, high 3dB BW and slew rate. I also considered OPA2355 (Probably better than AD8066?). I settled on AD8066 because I couldn't run transient simulations on OPA2355. (Don't know why, but kept failing) I used LTSpice to run the simulations. The integrator seems to work but I'm a little confused by the transient response. I have attached a .asc file.

Could anyone please help me with the design? Are there general set of design rules that can be followed for any integrator design?