hello!

I was wondering if anyone could take a look at my circuit for my second version of my "precision" current sensor, specifically the analog section. (TL/DR Last Paragraph). my first version, discussed , was a overall failure, although I did learn quite Abit from that so it wasn't a total loss, and my professor seemed to agree since I did end up getting an good grade on it.

I have obviously not given up, and have since designed a second version. It is for my final project for an advanced digital systems class, so features more of a digital system than my previous attempt. it is not part of the assignment to design my own board or circuit, but where's the fun in that : )

the "goal" of the project is accurate measurement of currents ranging from 1uA to 1A, with a burden of 10uV/mA and 10uV/uA, using a 10R and a 0.01R shunt. the "application" is to measure sleep currents of microcontrollers, but obviously this can be accomplished more simply, I would want my device to offer features for other "precision" current measurements. (the theoretical value for 10uV/mA is likely to have a slightly higher burden, maybe 15uV/mA)

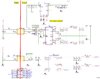

it works by using two shunts, which are amplified by a differential op amp, and then again by a PGA, and then fed into a dual channel (multiplexed) 24 bit ADC. both shunts can be measured (almost) at the same time, as each has their own amplification path, and the 10R can be shorted with a relay. No I don't expect to get 24 bits of usable data on this prototype, but the more usable bits the better.

analog side is isolated from digital using a pair of dc/dc isolation modules and an spi isolator. analog side is controlled by an ICE-40 fpga, and digital from a ATSAM arm mcu. the fpga does all the signal processing tasks, the mcu handles the 240x320 color tft lcd, pc communication, and other tasks. the device is battery powered from 1s lipo, although it is not designed for maximum battery life, as its intended to be plugged into USB for most applications. also of note the pictured 10R shunt is likely to change to a lower wattage rated one.

that's the brief summary, If anyone wants more information I would be more than happy to elaborate. Attached and pictured below are images of the case, analog amplification, analog power supplies, and PCB layout. also attached is a full pdf schematic. PCB layout has inner power/GND layers hidden. I don't expect anyone to fully or even partially review my design, but if anyone has any input on my analog section/ layout, my full design, or has a suggestion for an entirely new way to approach the shunt measurement problem, I would appreciate it, as I'd like this ~300$ prototype to at least somewhat work (lol), as I probably couldn't do a new version for awhile if this one fails catastrophically . Thanks.

Here is the analog "section":

View attachment Analog Section.jpg

I was wondering if anyone could take a look at my circuit for my second version of my "precision" current sensor, specifically the analog section. (TL/DR Last Paragraph). my first version, discussed , was a overall failure, although I did learn quite Abit from that so it wasn't a total loss, and my professor seemed to agree since I did end up getting an good grade on it.

I have obviously not given up, and have since designed a second version. It is for my final project for an advanced digital systems class, so features more of a digital system than my previous attempt. it is not part of the assignment to design my own board or circuit, but where's the fun in that : )

the "goal" of the project is accurate measurement of currents ranging from 1uA to 1A, with a burden of 10uV/mA and 10uV/uA, using a 10R and a 0.01R shunt. the "application" is to measure sleep currents of microcontrollers, but obviously this can be accomplished more simply, I would want my device to offer features for other "precision" current measurements. (the theoretical value for 10uV/mA is likely to have a slightly higher burden, maybe 15uV/mA)

it works by using two shunts, which are amplified by a differential op amp, and then again by a PGA, and then fed into a dual channel (multiplexed) 24 bit ADC. both shunts can be measured (almost) at the same time, as each has their own amplification path, and the 10R can be shorted with a relay. No I don't expect to get 24 bits of usable data on this prototype, but the more usable bits the better.

analog side is isolated from digital using a pair of dc/dc isolation modules and an spi isolator. analog side is controlled by an ICE-40 fpga, and digital from a ATSAM arm mcu. the fpga does all the signal processing tasks, the mcu handles the 240x320 color tft lcd, pc communication, and other tasks. the device is battery powered from 1s lipo, although it is not designed for maximum battery life, as its intended to be plugged into USB for most applications. also of note the pictured 10R shunt is likely to change to a lower wattage rated one.

that's the brief summary, If anyone wants more information I would be more than happy to elaborate. Attached and pictured below are images of the case, analog amplification, analog power supplies, and PCB layout. also attached is a full pdf schematic. PCB layout has inner power/GND layers hidden. I don't expect anyone to fully or even partially review my design, but if anyone has any input on my analog section/ layout, my full design, or has a suggestion for an entirely new way to approach the shunt measurement problem, I would appreciate it, as I'd like this ~300$ prototype to at least somewhat work (lol), as I probably couldn't do a new version for awhile if this one fails catastrophically . Thanks.

Here is the analog "section":

View attachment Analog Section.jpg