Melfior_Ra

New Member

Hi all.

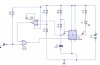

I am trying to build a logic tester. Nothing special. There are tons of diagrams ver the internet but i chose to create one by myself.

The problem is : When "1" or pulse is applied on the input the circuit acts as expected. But when "0" is applied the output of 555 is switching high and low. Now in this case i cant see the difference beetween 0 logic and pulse. What is wrong?

Thank you in advance.

I am trying to build a logic tester. Nothing special. There are tons of diagrams ver the internet but i chose to create one by myself.

The problem is : When "1" or pulse is applied on the input the circuit acts as expected. But when "0" is applied the output of 555 is switching high and low. Now in this case i cant see the difference beetween 0 logic and pulse. What is wrong?

Thank you in advance.