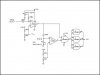

For a digitaly PWM modulator the maxium dutycycle may not be more than about 50% of the switching time. How can i simle made this with a LM393 comparator.

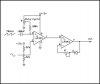

Here i have only one of the the comparators in use.

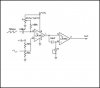

Or with the use with a Nand gate 4093.

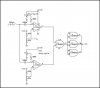

The PWM signal is used in a PWM audio-modulator what modulate a AM transmitter.

Here i have only one of the the comparators in use.

Or with the use with a Nand gate 4093.

The PWM signal is used in a PWM audio-modulator what modulate a AM transmitter.