Hi everyone!

Does anyone know to help me with non overlapping clock generator?

I need to draw how non-overelapping clcks are made?

I tried that but I can't get non-overlapping clocks.

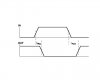

I need to draw signals at the output of each logic gate in this circuit

Actually I need timing diagrams for Vin,V1,V2,V3,V4,V5,V6,V7?

Logic gates are realised in CMOS technology and all logic gates have some delay.

Does anyone know to help me with non overlapping clock generator?

I need to draw how non-overelapping clcks are made?

I tried that but I can't get non-overlapping clocks.

I need to draw signals at the output of each logic gate in this circuit

Actually I need timing diagrams for Vin,V1,V2,V3,V4,V5,V6,V7?

Logic gates are realised in CMOS technology and all logic gates have some delay.

Attachments

Last edited: