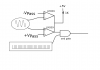

Let me start off by saying that I am not an EE I'm a chemist of sorts, more of an instrument person. We have a source of +5V TTL pulses coming at 80 MHz and we only want to pass ones when a sine sync voltage is below a certain level or above a certain level and we need to be able to switch between the two, hopefully programatically (or with a control voltage from a DAQ or whatever). Also we need the voltage pass level to be adjustable. I apologize if this is a bit confusing but the attached figure should give an idea of what I need. If someone could point me in the right direction or if they gave me a design I could throw 20 bucks their way as it would save me a lot of hassle.

I don't work for a company, I'm at a large research university (Emory).

Thanks

I don't work for a company, I'm at a large research university (Emory).

Thanks