Maverickmax

New Member

Hi

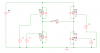

I have been using a SIMetrix simulation for conducting investigation on a simple full bridge inverter. I expect the waveform to be bipolar but I keep getting the unipolar waveform as shown below. I am aware that voltage waveform should be bipolar but it is not happening on my simulation. Please tell where did I go wrong?

Regards

MM

I have been using a SIMetrix simulation for conducting investigation on a simple full bridge inverter. I expect the waveform to be bipolar but I keep getting the unipolar waveform as shown below. I am aware that voltage waveform should be bipolar but it is not happening on my simulation. Please tell where did I go wrong?

Regards

MM

Attachments

Last edited: