oliverb

Member

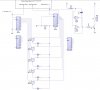

I have built a digital clock seehttps://www.electro-tech-online.com/threads/walters-or-no-walters.19324/

and want to design a cct to chime the hours using an old Grandfather clock bell. I plan to use a solenoid or hammer attached to a relay armature to strike the bell.

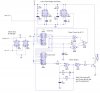

I have come up with the cct below but have got stuck. I need a cct to stop pulsing when IC1 is reset (pin0 logic1) but to start pulsing when an hourly pulse is received.

I have 1 second and faster pulses available from the clock or some sort of timer or astable could be used to drive the chime pulse as long as it is stopped and started as above.

The cct should work as folows every hour IC2 steps on 1 driven by the hour pulse. The hour pulse starts the Chime Pulse and continues to chime untill the O/P pins of IC1 matches the count of IC2 when it is reset via the relevant 12 AND gates. This in turn stops the Chime pulse.

IC1 and 2 would be linked to 2nd counters to enable the chime to count 12 then the hourly count would be reset.

Can anyone spot an easy solution or is there a better cct in existance already?

PS. I have never used PICs but would like to start using them so a solution using PICs is not out of the question. It could be a good excuse to go out and buy a book & programmer.

Thanks in advance.

Brett.

and want to design a cct to chime the hours using an old Grandfather clock bell. I plan to use a solenoid or hammer attached to a relay armature to strike the bell.

I have come up with the cct below but have got stuck. I need a cct to stop pulsing when IC1 is reset (pin0 logic1) but to start pulsing when an hourly pulse is received.

I have 1 second and faster pulses available from the clock or some sort of timer or astable could be used to drive the chime pulse as long as it is stopped and started as above.

The cct should work as folows every hour IC2 steps on 1 driven by the hour pulse. The hour pulse starts the Chime Pulse and continues to chime untill the O/P pins of IC1 matches the count of IC2 when it is reset via the relevant 12 AND gates. This in turn stops the Chime pulse.

IC1 and 2 would be linked to 2nd counters to enable the chime to count 12 then the hourly count would be reset.

Can anyone spot an easy solution or is there a better cct in existance already?

PS. I have never used PICs but would like to start using them so a solution using PICs is not out of the question. It could be a good excuse to go out and buy a book & programmer.

Thanks in advance.

Brett.