EvilGenius

Member

Hello

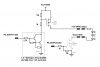

I designed the attached circuit and when I built it, it behaves oddly.

The circuit is to drive a 12V, 3A LED Module (for simplicity). The inputs are from 2 pins of microcontroller (PIC @5V).

One pin controls one channel of NPN darlington transistor array (Darl-NPN) connected to gate of a PMOS to provide 12V Drive output voltage and current to LED module. The second pin drives an NMOS to sink the current to ground from LED module. The specifics of each component is provided.

Issue: It seems like the PMOS is staying on at all times although the bias and pull-up should have turned it off when no voltage (current) is coming from PIC Pin1. My guess is that the darlington array with hfe of 1000 is so powerful in amplification that smallest voltage (leakage) turns it on and keeps it on.

Any help or suggestions is very much appreciated.

Regards, Rom

I designed the attached circuit and when I built it, it behaves oddly.

The circuit is to drive a 12V, 3A LED Module (for simplicity). The inputs are from 2 pins of microcontroller (PIC @5V).

One pin controls one channel of NPN darlington transistor array (Darl-NPN) connected to gate of a PMOS to provide 12V Drive output voltage and current to LED module. The second pin drives an NMOS to sink the current to ground from LED module. The specifics of each component is provided.

Issue: It seems like the PMOS is staying on at all times although the bias and pull-up should have turned it off when no voltage (current) is coming from PIC Pin1. My guess is that the darlington array with hfe of 1000 is so powerful in amplification that smallest voltage (leakage) turns it on and keeps it on.

Any help or suggestions is very much appreciated.

Regards, Rom