## Adaptive Power MOSFET Driver<sup>1</sup>

#### **FEATURES**

- dv/dt and di/dt Control

- Undervoltage Protection

- Short-Circuit Protection

- t<sub>rr</sub> Shoot-Through Current Limiting

- Low Quiescent Current

- CMOS Compatible Inputs

- Compatible with Wide Range of MOSFET Devices

- Bootstrap and Charge Pump Compatible (High-Side Drive)

#### **DESCRIPTION**

The Si9910 Power MOSFET driver provides optimized gate drive signals, protection circuitry and logic level interface. Very low quiescent current is provided by a CMOS buffer and a high-current emitter-follower output stage. This efficiency allows operation in high-voltage bridge applications with "bootstrap" or "charge-pump" floating power supply techniques.

The non-inverting output configuration minimizes current drain for an n-channel "on" state. The logic input is internally diode clamped to allow simple pull-down in high-side drives.

Fault protection circuitry senses an undervoltage or output short-circuit condition and disables the power MOSFET. Addition of one external resistor limits maximum di/dt of the external Power MOSFET. A fast feedback circuit may be used to limit shoot-through current during  $t_{rr}$  (diode reverse recovery time) in a bridge configuration.

The Si9910 is available in both standard and lead (Pb)-free 8-pin plastic DIP and SOIC packages which are specified to operate over the industrial temperature range of -40°C to 85°C.

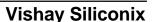

#### **FUNCTIONAL BLOCK DIAGRAM**

1. Patent Number 484116.

## Vishay Siliconix

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> Supply Range         -0.3 V to 18 V         Junction Temperature (T <sub>J</sub> )         150°C |

|------------------------------------------------------------------------------------------------------------------|

|                                                                                                                  |

| Pin 1, 4, 5, 7, 8                                                                                                |

| Pin 2                                                                                                            |

| Input Current                                                                                                    |

| Peak Current (I <sub>pk</sub> )                                                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                  | Symbol            | Test Conditions Unless Otherwise Specified  V <sub>DD</sub> 10.8 V to 16.5 V T <sub>A</sub> = OperatingTemperature Range | Limits                 |      |                        |      |

|--------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|------|

|                                            |                   |                                                                                                                          | Min <sup>c</sup>       | Typb | Max <sup>c</sup>       | Unit |

| Input                                      |                   |                                                                                                                          |                        |      |                        |      |

| High Level Input Voltage                   | V <sub>IH</sub>   |                                                                                                                          | 0.70 x V <sub>DD</sub> | 7.4  |                        |      |

| Low Level Input Voltage                    | V <sub>IL</sub>   |                                                                                                                          |                        | 6.0  | 0.35 x V <sub>DD</sub> | V    |

| Input Voltage Hysteresis                   | V <sub>h</sub>    |                                                                                                                          | 0.90                   | 2.0  | 3.0                    |      |

| High Level Input Current                   | I <sub>IH</sub>   | $V_{IN} = V_{DD}$                                                                                                        |                        |      | ±1                     |      |

| Low Level Input Current                    | I <sub>IL</sub>   | V <sub>IN</sub> = 0 V                                                                                                    |                        |      | ±1                     | μΑ   |

| Output                                     |                   |                                                                                                                          |                        |      |                        |      |

| High Level Output Voltage                  | V <sub>OH</sub>   | I <sub>OH</sub> = -200 mA                                                                                                | V <sub>DD</sub> -3     | 10.7 |                        | V    |

| Low Level Output Voltage                   | V <sub>OL</sub>   | I <sub>OL</sub> = 200 mA                                                                                                 |                        | 1.3  | 3                      |      |

| Undervoltage Lockout                       | V <sub>UVLO</sub> |                                                                                                                          | 8.3                    | 9.2  | 10.6                   |      |

| I <sub>SENSE</sub> Pin Threshold           | V <sub>TH</sub>   | Max I <sub>S</sub> = 2 mA, Input High<br>100 mV Change on Drain                                                          | 0.5                    | 0.66 | 0.8                    |      |

| Voltage Drain-Source Maximum               | V <sub>DS</sub>   | Input High                                                                                                               | 8.3                    | 9.1  | 10.2                   |      |

| Input Current for V <sub>DS</sub> Input    | I <sub>VDS</sub>  |                                                                                                                          |                        | 12   | 20.0                   | μΑ   |

| Peak Output Source Current                 | I <sub>OS+</sub>  |                                                                                                                          |                        | 1    |                        | Α    |

| Peak Output Sink Current                   | I <sub>OS-</sub>  |                                                                                                                          |                        | -1   |                        | 7    |

| Supply                                     |                   |                                                                                                                          |                        |      |                        |      |

| Supply Range                               | V <sub>DD</sub>   |                                                                                                                          | 10.8                   |      | 16.5                   | ٧    |

| Supply Current                             | I <sub>DD1</sub>  | Output High, No Load                                                                                                     |                        | 0.1  | 1                      | _    |

|                                            | I <sub>DD2</sub>  | Output Low, No Load                                                                                                      |                        | 100  | 500                    | μΑ   |

| Dynamic                                    |                   |                                                                                                                          |                        |      |                        |      |

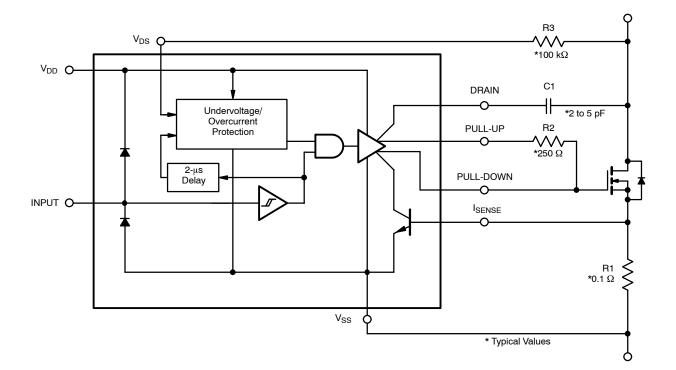

| Propagation Delay Time Low to High Level   | t <sub>PLH</sub>  | C <sub>L</sub> = 2000 pF                                                                                                 |                        | 120  |                        | ns   |

| Propagation Delay Time High to Low Level   | t <sub>PHL</sub>  |                                                                                                                          |                        | 135  |                        |      |

| Rise Time                                  | t <sub>r</sub>    |                                                                                                                          |                        | 50   |                        |      |

| Fall Time                                  | t <sub>f</sub>    |                                                                                                                          |                        | 35   |                        |      |

| Overcurrent Sense Delay (V <sub>DS</sub> ) | t <sub>DS</sub>   |                                                                                                                          |                        | 1    |                        | μS   |

| Input Capacitance                          | C <sub>in</sub>   |                                                                                                                          |                        | 5    |                        | pF   |

- Notes

a. Refer to PROCESS OPTION FLOWCHART for additional information.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

#### **AC TESTING CONDITIONS**

#### PIN CONFIGURATIONS AND ORDERING INFORMATION

| ORDERING INFORMATION |                   |         |  |  |  |

|----------------------|-------------------|---------|--|--|--|

| Part Number          | Temperature Range | Package |  |  |  |

| Si9910DY             |                   |         |  |  |  |

| Si9910DY-T1          |                   | SOIC-8  |  |  |  |

| Si9910DY-T1—E3       | −40 to 85°C       |         |  |  |  |

| Si9910DJ             |                   | PDIP-8  |  |  |  |

| Si9910DJ—E3          | 1                 | PDIP-8  |  |  |  |

### **Vishay Siliconix**

# VISHAY

#### **PIN DESCRIPTION**

Pin 1: V<sub>DS</sub>

Pin 1 or  $V_{DS}$  is a sense input for the maximum source-drain voltage limit. Two microseconds after a high transition on input pin 2, an internal timer enables the  $V_{DS(max)}$  sense circuitry. A catastrophic overcurrent condition, excessive on-resistance, or insufficient gate-drive voltage can be sensed by limiting the maximum voltage drop across the power MOSFET. An external resistor (R3) is required to protect pin 1 from overvoltage during the MOSFET "off" condition. Exceeding  $V_{DS(max)}$  latches the Si9910 "off." Drive is re-enabled on the next positive- going input on pin 2. If pin 1 is not used, it must be connected to pin 6 ( $V_{SS}$ ).

#### Pin 2: INPUT

A non-inverting, Schmidt trigger input controls the state of the MOSFET gate-drive outputs and enables the protection logic. When the input is low ( $\leq$  V $_{IL}$ ), V $_{DD}$  is monitored for an undervoltage condition (insufficiently charged bootstrap capacitor). If an undervoltage ( $\leq$  V $_{DD(min)}$ ) condition exists, the driver will ignore a turn-on input signal. An undervoltage ( $\leq$  V $_{DD(min)}$ ) condition during an "on" state will not be sensed.

#### Pin 3: V<sub>DD</sub>

$V_{DD}$  supplies power for the driver's internal circuitry and charging current for the power MOSFET's gate capacitance. The Si9910 minimizes the internal  $I_{DD}$  in the "on" state (gate-drive outputs high) allowing a "floating" power supply to be provided by charge pump or bootstrap techniques.

#### Pin 4: DRAIN

Drain is an analog input to the internal dv/dt limiting circuitry. An external capacitor (C1) must be used to protect the input from exposure to the high-voltage ("off" state) drain and to set the power MOSFET's maximum rate of dv/dt. If dv/dt feedback is not used, pin 4 must be left open.

#### Pin 5: I<sub>SENSE</sub>

$I_{SENSE}$  in combination with an external resistor (R<sub>1</sub>) protects the power MOSFET from potentially catastrophic peak currents.  $I_{SENSE}$  is an analog feedback that limits current during the power MOSFET's transition to an "on" state. It is intended to protect power MOSFETs (in a half-bridge arrangement) from "shoot-through" current, resulting from excess di/dt and  $t_{rr}$  of flyback diodes or from logic timing overlap. An 0.8-V drop across (R1) should indicate a current level that is approximately four times the maximum allowable load current. When the  $I_{SENSE}$  input is not used, it should be tied to pin 6 (V<sub>SS</sub>).

#### Pin 6: V<sub>SS</sub>

$V_{SS}$  is the driver's ground return pin. The applications diagram illustrates the connection of  $V_{SS}$  for source-referenced

"floating" applications (half-bridge, high-side) and ground-referenced applications (half-bridge, low-side).

Pin 7: PULL-DOWN Pin 8: PULL-UP

Pull-up and pull-down outputs collectively provide the power MOSFET gate with charging and discharging currents. Turn "on" or "off" di/dt can be limited by adding resistance ( $R_2$ ) in series with the appropriate output.

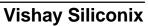

#### **APPLICATIONS**

#### "Floating" High-Side Drive Applications

As demonstrated in Figure 1, the Si9910 is intended for use as both a ground-referenced gate driver and as a "high-side" or source-referenced gate driver in half-bridge applications. Several features of the Si9910 permit its use in half-bridge high-side drive applications.

A simple and inexpensive method of isolating a floating supply to power the Si9910 in high-side driver applications had to be provided. Therefore, the Si9910 was designed to be compatible with two of the most commonly used floating supply techniques: the bootstrap and the charge pump. Both of these techniques have limitations when used alone. A properly designed bootstrap circuit can provide low-impedance drive which minimizes transition losses and the charge pump circuit provides static operation.

The Si9910 is configured to take advantage of either floating supply technique if the application is not sensitive to their particular limitations, or both techniques if switching losses must be minimized and static operation is necessary. The schematic above illustrates both the charge pump and bootstrap circuits used in conjunction with an Si9910 in a high-side driver application.

Input signal level shifting is accomplished with a passive pull-up (R4) and n-channel MOSFET (Q2) for pull-down in applications below 500 V. Total node capacitance defines the value of R4 needed to guarantee an input transition rate which safely exceeds the maximum dv/dt rate of the output half-bridge. Using level-shift devices with higher current capabilities may necessitate the addition of current-limiting components such as R5.

#### **Bootstrap Undervoltage Lockout**

When using a bootstrap capacitor as a high-side floating supply, care must be taken to ensure time is available to recharge the bootstrap capacitor prior to turn-on of the high-side MOSFET. As a catastrophic protection against abnormal conditions such as start-up, loss of power, etc., an internal voltage monitor has been included which monitors the bootstrap voltage when the Si9910 is in the low state. The Si9910 will not respond to a high input signal until the voltage on the bootstrap capacitor is sufficient to fully enhance the power MOSFET gate. For more details, please refer to Application Note AN705.

#### **APPLICATION CIRCUIT**

FIGURE 1. High-Voltage Half-Bridge with Si9910 Drivers

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?70009">http://www.vishay.com/ppg?70009</a>.

Vishay

## **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com