# MIC5031

High-Speed High-Side MOSFET Driver

### Not Recommended for New Designs

## **General Description**

The MIC5031 MOSFET driver is designed to switch an N-channel enhancement-type MOSFET from a TTL control signal in a high-side switch application. The MIC5031 provides overcurrent protection, can accommodate loads with high-inrush current, and is designed to survive automotive power disturbances. This driver is suitable for up to 30kHz PWM operation with 0% to 100% duty cycle.

The MIC5031 is powered by the +4.5V to +30V load voltage. An external bootstrap capacitor and internal charge pump drive the gate output higher than the supply voltage. The bootstrap capacitor provides speed, while the charge pump can sustain the high gate output voltage continuously.

The MIC5031 features a resistor programmable overcurrent shutdown (circuit breaker) function that monitors the voltage drop across the external MOSFET. A capacitor programmable shutdown delay allows a high-inrush current load to be energized without causing undesired shutdown. An openload detection feature is included and can be used by adding an external high-value resistor.

The MIC5031 is protected against automotive load dump and reverse battery conditions. The driver is also protected from excessive power dissipation by an internal overtemperature shutdown circuit.

An open-collector fault flag output indicates overcurrent, overtemperature, or open-load fault conditions.

## Features

- +4.5V to +30V operation

- Fast gate drive (rise time = 70ns, fall time = 50ns, with 1000pF load and 5V supply)

- Overcurrent detection across MOSFET

- Overcurrent shutdown delay

- · Charge pump for high-side dc applications

- TTL compatible input

- Overtemperature shutdown

- Automotive load dump protection

- Reverse battery protection

- Open-collector fault flag

- Near zero-current disable state

### Applications

- Automotive power switch

- Automotive PWM control

- Circuit breaker

- PWM circuits

## **Ordering Information**

| Part Number | Temperature Range | Package      |  |  |

|-------------|-------------------|--------------|--|--|

| MIC5031BM   | –40°C to +85°C    | 16-lead SOIC |  |  |

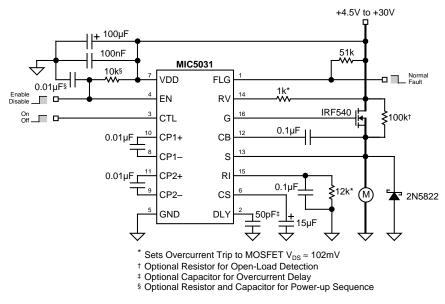

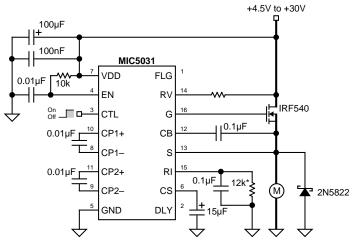

## **Typical Application**

High-Side Power Switch and Circuit Breaker

Micrel, Inc. • 1849 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 944-0970 • http://www.micrel.com

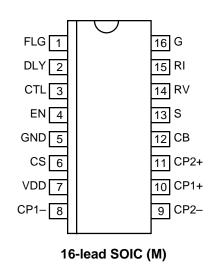

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                 |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FLG      | Fault Flag: (Output): Open-collector output sinks current upon overcurrent, open-load, or overtemperature detection. 10mA maximum load.                                                                                                                                                                                      |

| 2          | DLY      | Overcurrent Delay Time Capacitor: Optional. Capacitor to ground delays activation of overcurrent shutdown.                                                                                                                                                                                                                   |

| 3          | CTL      | Control (Input): TTL compatible on/off control input. Logic high drives the gate output above the supply voltage. Logic low forces the gate output near ground. Logic low also resets the overcurrent fault latch.                                                                                                           |

| 4          | EN       | Enable (Input): CMOS compatible input. Logic high enables the charge pump. Logic low disables the charge pump and draws near zero supply current.                                                                                                                                                                            |

| 5          | GND      | Ground: Power return.                                                                                                                                                                                                                                                                                                        |

| 6          | CS       | Internal Supply Storage Capacitor: 10μF external capacitor to GND.<br>Provides additional current to internal circuitry during switching transitions.                                                                                                                                                                        |

| 7          | VDD      | Supply (Input): +4.5V to +30V supply.                                                                                                                                                                                                                                                                                        |

| 8          | CP1–     | Charge Pump Capacitor #1: Refer to CP1+.                                                                                                                                                                                                                                                                                     |

| 9          | CP2-     | Charge Pump Capacitor #2: Refer to CP2+.                                                                                                                                                                                                                                                                                     |

| 10         | CP1+     | Charge Pump Capacitor #1: External 0.01µF voltage tripler capacitor.                                                                                                                                                                                                                                                         |

| 11         | CP2+     | Charge Pump Capacitor #2: External 0.01µF voltage tripler capacitor.                                                                                                                                                                                                                                                         |

| 12         | СВ       | Bootstrap Capacitor: 0.1µF capacitor to source for fastest rise time.                                                                                                                                                                                                                                                        |

| 13         | S        | Source: Source connection to external MOSFET.                                                                                                                                                                                                                                                                                |

| 14         | RV       | Reference Voltage Resistor: Resistor to VDD provides a reference voltage drop. A voltage drop across the external MOSFET that is greater than the voltage drop across the reference resistor indicates an overcurrent condition. ( <i>Refer to applications section</i> ) Zero temperature coefficient resistor recommended. |

| 15         | RI       | Reference Current Resistor: Resistor to GND sets constant current value through RV resistor ( <i>Refer to applications section</i> ) and matches temperature compensation of RV resistor. Zero temperature coefficient resistor recommended.                                                                                 |

| 16         | G        | Gate (Output) : Gate connection to external MOSFET.                                                                                                                                                                                                                                                                          |

# **Absolute Maximum Ratings**

| Supply Voltage (V <sub>DD</sub> )          | +36V               |

|--------------------------------------------|--------------------|

| Enable Input Voltage (V <sub>EN</sub> )    | +36V               |

| Control Input Voltage (V <sub>CTL</sub> )  |                    |

| V <sub>DD</sub> ≤ 15V                      | V <sub>חח</sub>    |

| V <sub>DD</sub> > 15V                      | +15 <del>¯</del> V |

| Flag Output Voltage (V <sub>FLG</sub> )    | +36V               |

| Reference Voltage Input (V <sub>RV</sub> ) | +36V               |

| Junction Temperature (T <sub>J</sub> )     | 150°C              |

# **Operating Ratings**

| Supply Voltage (V <sub>DD</sub> )            | +4.5V to +30V   |

|----------------------------------------------|-----------------|

| Ambient Temperature Range $(T_A)$            |                 |

| A-temperature range                          | –55°C to +125°C |

| B-temperature range                          | 40°C to +85°C   |

| Package Thermal Resistance ( $\theta_{JA}$ ) |                 |

| SOIC                                         | 115°C/W         |

# **Electrical Characteristics**

$V_{DD}$  = 12V;  $C_B$  = 0.1 $\mu F,~CP1$  = CP2 = 0.01 $\mu F;~T_A$  = 25°C; unless noted

| Symbol            | Parameter                        | Condition                                      | Min | Тур  | Max | Units |

|-------------------|----------------------------------|------------------------------------------------|-----|------|-----|-------|

| I <sub>DD</sub>   | Supply current                   | $V_{EN} = 0V, V_{CTL} = 0V$                    |     | 0.3  | 3   | μA    |

|                   |                                  | $V_{EN} = 12V, V_{CTL} = 0V$                   |     | 1.0  |     | mA    |

|                   |                                  | $V_{EN} = 12V, V_{CTL} = 5V$                   |     | 0.72 |     | mA    |

| I <sub>DDR</sub>  | Reverse voltage leakage current  | $V_{DD} = -12V$                                |     | -0.2 | -5  | μA    |

| V <sub>CTL</sub>  | Control input voltage threshold  |                                                |     | 1.55 |     | V     |

| V <sub>CTLH</sub> | Control input voltage hysteresis |                                                | 0.2 | 0.5  | 1.0 | V     |

| I <sub>CTL</sub>  | Control input current            |                                                |     | 0.1  | 1   | μA    |

| V <sub>EN</sub>   | Enable input voltage threshold   |                                                |     | 6    |     | V     |

| I <sub>EN</sub>   | Enable input current             |                                                |     | 0.1  | 1   | μA    |

| V <sub>IOS</sub>  | Overcurrent comparator offset    |                                                |     |      | ±5  | mV    |

| I <sub>RV</sub>   | Current limit reference current  | R <sub>RI</sub> = 12.0k                        | 97  | 100  | 103 | μA    |

| t <sub>SHDL</sub> | Overcurrent shut down delay      | C <sub>DLY</sub> = 50pF                        |     | 16   |     | μs    |

| V <sub>G</sub>    | Gate drive voltage               | $V_{EN} = 12V, V_{CTL} = 5V$                   |     | 25   |     | V     |

| t <sub>DLR</sub>  | Gate turn-on delay               | V <sub>EN</sub> = 12V, C <sub>L</sub> = 1000p  |     | 420  |     | ns    |

| t <sub>R</sub>    | Gate rise time                   | C <sub>L</sub> = 1000pF                        |     | 90   |     | ns    |

| t <sub>DLF</sub>  | Gate turnoff delay               | C <sub>L</sub> = 1000pF                        |     | 300  |     | ns    |

| t <sub>F</sub>    | Gate fall time                   | C <sub>L</sub> = 1000pF                        |     | 50   |     | ns    |

| V <sub>OLTH</sub> | Open-load threshold voltage      | $V_{EN} = 12V, V_{CTL} = 0V$                   |     | 6.3  |     | V     |

| Т <sub>от</sub>   | Overtemperature shut down        | $V_{EN} = 12V, V_{CTL} = 5V$                   |     | 140  |     | °C    |

| Тотн              | Overtemp. shut down hysteresis   | $V_{EN} = 12V, V_{CTL} = 5V$                   | 10  |      |     | °C    |

| f <sub>CP</sub>   | Charge pump frequency            | V <sub>DD</sub> = 5V, <b>Note 1</b>            |     | 190  |     | kHz   |

| V <sub>FLG</sub>  | Flag active voltage              | open load error, I <sub>FLG</sub> = 2mA (sink) |     | 0.2  |     | V     |

General Note: Devices are ESD protected; however, handling precautions are recommended.

Note 1: Oscillator burst mode at  $V_{DD} \geq 5.2 V.$

Micrel

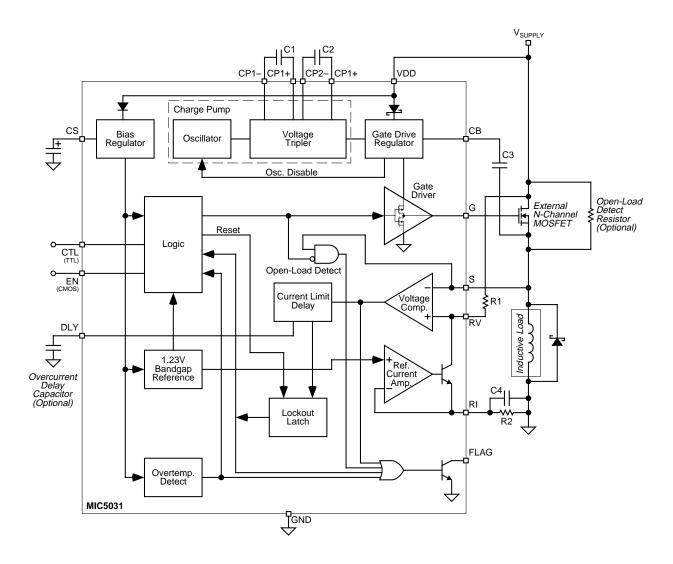

## **Block Diagram**

## **Functional Description**

#### Refer to "Functional Diagram."

The MIC5031 is a noninverting device. Applying a CMOS logic high signal to EN (enable input) activates the driver's internal circuitry. Applying a TTL logic high signal to CTL (control input) produces gate drive output. The G (gate) output is used to turn on an external N-channel MOSFET.

#### Control

CTL (control) is a TTL compatible input. The threshold is approximately 1.4V, independent of the supply voltage.

The falling edge of a signal applied to CTL also resets the overcurrent lockout latch.

#### Enable

EN (enable) is a CMOS compatible input. EN enables or disables all internal circuitry. The enable threshold is approximately half the supply voltage. The MIC5031 supply current is near zero when the driver is disabled (low). See "Applications Information: Power-Up Sequence."

#### Charge Pump

The charge pump produces a voltage that is higher than the supply voltage. This higher voltage is required to drive the external N-channel MOSFET in high-side switch circuits.

The charge pump consists of an oscillator and a voltage tripler. When the driver is enabled, the charge pump is switched on and off to regulate its output voltage.

External capacitors C1 and C2 are required. The charge pump will not operate without these capacitors.

#### **Bootstrap Capacitor**

The external bootstrap capacitor is necessary to achieve the fastest gate rise times. The bootstrap capacitor (C3) supplies additional current at a higher voltage to the gate drive regulator as the MOSFET is switched on.

When the MOSFET is off, the gate drive regulator voltage is applied to the boost capacitor. As the MOSFET turns on, the MOSFET source-to-ground voltage increases. The increasing source voltage is added to the voltage across the capacitor for a voltage doubling effect.

#### **Gate Drive Regulator**

The gate drive regulator manages the voltage from the bootstrap capacitor, the supply, and the charge pump.

The gate drive regulator charges the bootstrap capacitor when the MOSFET is off and limits the voltage from the bootstrap capacitor as the MOSFET is switched on. It also performs skip-mode control by switching the charge pump on and off to regulate the gate drive output voltage.

#### Gate Output

When the MIC5031 is enabled and CTL is high, the gate driver steers regulated voltage to G (gate output). When CTL is low, the gate driver grounds G. This respectively charges or discharges the external MOSFET's gate, .

### Current Sense

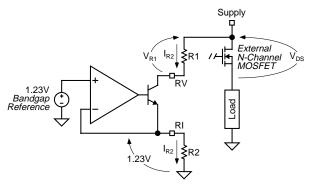

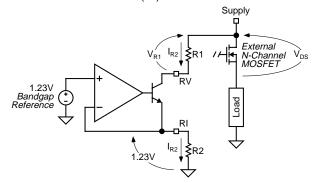

Refer to the "Voltage Reference (Simplified)" diagram.

The MIC5031 detects an overcurrent condition by comparing the voltage drop across the external MOSFET to a reference voltage drop created across R1. If  $V_{DS}$  exceeds  $V_{R1}$ , a comparator (not shown) shuts off the external MOSFET by way of the current limit delay, lockout latch, and logic.

The bandgap reference, op amp and NPN create a constant voltage (1.23V) across R2. This results in a constant current,  $I_{R2}$ , through R2. Ignoring a small amount of base current, the same current ( $I_{R2}$ ) flows through R1. R1 is selected to achieve the desired reference voltage drop,  $V_{R1}$ . Refer to the applications section for formulas.

### Voltage Reference (Simplified)

An overcurrent condition also activates the fault flag output when the lockout latch is activated.

#### **Overcurrent-Shutdown Delay**

The overcurrent-shutdown delay circuit permits a delay between overcurrent detection and latch activation for highinrush current loads.

The delay can be increased by adding capacitance from DLY to GND.

#### **Open-Load Detect**

The open load detect resistor is an external high-value pullup resistor that causes the source voltage of the external MOSFET to increase when the load is missing.

The MIC5031 monitors the S-pin voltage only when the gate driver is off. If the voltage on the S-pin rises above the open-load detect threshold, the fault flag is activated.

#### **Overtemperature Detect**

The overtemperature detect circuit switches the logic to turn the output off at approximately 140°C. An overtemperature shutdown condition is restored to normal automatically When the device cools to about 130°C (10°C hysteresis).

An overtemperature condition also activates the fault flag output.

#### Fault Flag

FLT (fault flag) is an open-collector NPN transistor. Fault is active (pulls collector near ground) upon overcurrent, open-load, or overtemperature.

# **Applications Information**

## **Power-Up Sequence**

The supply voltage ( $V_{DD}$ ) must be applied to VDD before EN is asserted. If EN is not required for the application, an RC network must be used to delay the voltage rise applied to EN with respect to VDD. See Figure 1.

Figure 1. Enable Application

Refer to "Typical Application" for controlling EN from opencollector or open-drain logic. The 10k resistor and  $0.01\mu$ F capacitor connected to VDD, GND, and EN keep EN low during power up before the open-collector or open-drain logic becomes active.

The 10k resistor and  $0.01 \mu F$  capacitor can be omitted if EN is held low by the external logic until VDD is powered.

### **Overcurrent Detection**

Using the MOSFET manufacturer's data and the maximum allowable load current, determine the maximum drain-to-source voltage drop,  $V_{DS}$ , that will occur across the external MOSFET in normal operation. This will also be the reference voltage and the overcurrent trip voltage,  $V_{R1}$ .

Figure 2. Resistor Calculations

#### Reference Current Resistor

Resistor R2 sets the reference current. For most applications, a reference current of  $100\mu A$  is suggested.

$$R2 = \frac{R1}{I_{R2}}$$

where:

R2 = reference current resistor ( $\Omega$ )

$$I_{R2}$$

= reference current (A) [R2 = 12k $\Omega$  for approximately 100 $\mu$ A]

#### Reference Voltage Resistor

The reference voltage resistor value is calculated from the reference current and the reference voltage (overcurrent drop voltage).

$$R1 = \frac{V_R}{I_{R2}}$$

where:

R1 = reference voltage resistor ( $\Omega$ )

V<sub>R1</sub> = reference voltage (V) [see above]

I<sub>R2</sub> = reference current (A) [see above]

### **Overcurrent Delay Capacitor**

For lamp switching applications, the delay capacitor ( $C_{DLY}$ ) may be as high as several microfarads. Lamps often have an inrush current of 10× their steady-state operating current. In PWM applications, pay attention to the input frequency vs. the overcurrent delay. They can conflict with each other if not properly planned.

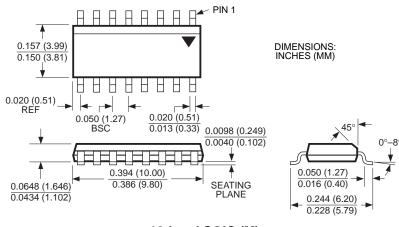

# **Package Information**

16-Lead SOIC (M)

### MICREL INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 1999 Micrel Incorporated