# DESIGN AND ANALYSIS TECHNIQUES FOR DYNAMIC CURRENT MIRRORS

#### THESE No 890 (1990)

#### PRESENTEE AU DEPARTEMENT D'ELECTRICITE

#### ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ES SCIENCES TECHNIQUES

#### PAR

#### **GEORGE WEGMANN**

Ingénieur électricien diplômé EPFL de nationalité suisse et française

acceptée sur proposition du jury :

Prof. E.A. Vittoz, rapporteur Prof. R. Castello, corapporteur Prof. M. Declercq, corapporteur Prof. G.C. Temes, corapporteur

> Lausanne, EPFL 1990

| • |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

# ACKNOWLEDGMENTS

I wish to express my deepest appreciation to my research advisor Professor Eric Vittoz for his outstanding teaching, guidance and support throughout the time of my graduate studies. I will never forget when he picked me up in the laboratory while I was desperately trying to model the charge injection phenomenon. I liked the free and easy manner we worked together and I was impressed by his interest for my work even for details. I hope many others will have the opportunity to profit from his wide knowledge and personality.

I would also like to express my thanks to Professor Rinaldo Castello, Professor Michel Declercq and Professor Gabor Temes for agreeing to be my co-referees and for the suggestions and corrections they made to this manuscript.

I address my gratitude to the late Professor Roger Dessoulavy who proposed me first to undertake some graduate studies. I am very thankful to Professor Michel Declercq, the director of the laboratory, who allowed me to finish this work in good conditions.

I am very grateful to all my friends, colleagues and former colleagues of the Laboratoire d'Electronique Générale, particularly to Dr. Christian Enz, Dr. François Krummenacher, Dr. Fouad Rahali, Dr. Jacques Robert, François Dorel and Norbert Jöhl, for their helpful discussions and stimulating collaboration.

I would also like to thank Professor Kamran Eshraghian from Adelaide University, Prof. Anton Mavretic from Boston University and Dr. Michel Dutoit from the EPFL for proofreading this thesis.

Finally, I would like to express my deepest gratitude to my dear parents for their support and encouragement during all these years of study.

\* . . . . .

#### RESUME

De nos jours l'électronique fait de plus en plus appel à des circuits digitaux et de ce fait la technologie CMOS (Complementary Metal Oxide Semiconductor) devient dominante. Cette technologie CMOS, comparée à une technologie bipolaire, offre différents avantages, comme des dimensions geométriques réduites et une consommation faible.

Néanmoins le domaine analogique persiste car la nature des phénomènes physiques et leur perception est analogique. Des capteurs électroniques perçoivent ces événements analogiques et délivrent un signal de sortie en conséquence. Avant de pouvoir utiliser ce signal pour un traitement numérique il doit être mis en forme et traité de manière analogique.

Le miroir de courant est un élément fonctionnel de base dans la plupart des blocs analogiques. Il permet de multiplier et duplifier un courant imposé, qui contient l'information (signal ou polarisation). Malheureusement, à cause des variations aléatoires au cours du processus de fabrication, les paramètres des transistors utilisés dans la réalisation des miroirs de courant sont affectés de différentes erreurs, telles que la variation de la tension de seuil et la variation du paramètre de transfer. Les courants de sortie de deux transistor dessinés identiques sont par conséquent différents.

Ce désappariement entre composants ainsi que le bruit en 1/f sont des limitations principales pour les circuits de haute précision. La technique standard consiste à réduire ces imperfections en augmentant simplement la taille des transistors et à noyer le désappariement des tensions de seuil dans une grande tension de grille.

Les techniques analogiques dynamiques exploitent l'absence de courant de grille d'un transistor MOS pour stocker temporairement une information analogique sur la capacité de grille. En utilisant séquentiellement le même transistor comme transistor d'entrée et de sortie d'un miroir de courant, la notion de désappariement disparaît. Cette technique d'échantillonnage permet d'augmenter la précision considérablement et de la pousser vers de nouvelles limites indépendantes de l'appariement entre transistors, donc des

variations du processus de fabrication. La précision des courants dépend alors de la capacité à mémoriser de manière exacte le signal.

L'idée de mémoriser des courants a été formulée il y a plus de dix ans déjà, mais il a fallu attendre l'avancement de la théorie sur les échantilloneurs-bloqueurs et le progrès de la technologie pour voir la première réalisation pratique performante d'un de ces circuit intégrés vers le début de 1988.

Cette thèse formule, étudie et analyse les différents aspects, possibilités, paramètres et limitations liés à ce nouveau type de miroirs de courant, appelés aussi copieurs de courants, qui repose sur un échantillonage de la tension de grille d'un transistor MOS. Des résultats expérimentaux permettent de mettre en évidence l'influence des améliorations proposées.

Le principe de mémorisation ainsi que les problèmes majeurs apparaissant lors de la commutation des transistors sont décrits. Des structures minimisant ces effets indésirables sont proposées, leurs avantages et désavantages comparés et des extensions possibles sont présentées. Les paramètres qui influencent la précision sont étudiés en détail, tel que les variations de la tension de drain, les courants de fuites, l'injection de charge, le bruit blanc et le bruit en 1/f. Les transitoires engendrés lors des commutations ainsi que le comportement dynamique d'une cellule de base sont analysés, et un compromis entre la précision et la vitesse en est déduit. Des considérations pratiques au sujet du "layout" sont énumérées et des résultats expérimentaux résument l'influence des différents paramètres. Le miroir de courant dynamique est implementé dans un filtre continu afin d'augmenter l'appariement des fréquences centrales. Finalement, des applications tels que filtre à courant commutés et convertisseur D/A & A/D sont mentionées.

# TABLE OF CONTENTS

| CHAPTER 1 INTRODUCTION                                                                                                                    | 1        |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

| CHAPTER 2 PRINCIPLE & STRUCTURES OF CURRENT COPIERS                                                                                       |          |

| 2.1 Principle of Current Copiers                                                                                                          | 8        |

| 2.2 Principal Accuracy Limitations                                                                                                        |          |

| 2.3 Principle of a Dynamic Current Mirror                                                                                                 |          |

| 2.4 Current Copier Structures  2.5.1 Op-Amp Structure  2.5.2 Cascoded Structure  2.5.3 Current Copier with Reduced Transconductance gmm4. |          |

| 2.5 Summary                                                                                                                               | 17       |

| CHAPTER 3 DYNAMIC CURRENT MIRROR CONFIGURATIONS                                                                                           | 19       |

| 3.1 Basic Mirror Considerations  3.1.1 Externally Biased Dynamic Current Mirrors  3.1.2 Self-biased Dynamic Current Mirrors               | 20       |

| 3.2 Multiple and Multiplying Mirrors                                                                                                      | 24<br>24 |

| 3.3 Dividing Current Mirrors                                                                                                              |          |

| 3.3.2 Division by Any Integer Number (1/n)                                                                                                |          |

| CHAPTER 4                                                               |    |

|-------------------------------------------------------------------------|----|

| ACCURACY LIMITATIONS                                                    | 35 |

| 4.1 Influence of Drain Voltage Variations                               | 36 |

| 4.1.1 Output Conductance gds                                            |    |

| 4.1.2 Capacitive divider, $C_{gd}$ - $C$                                |    |

| 4.1.3 Optimization of the Ratio C <sub>G</sub> /C                       |    |

| 4.1.4 Direct Charge Flow Path                                           |    |

| 4.2 Leakage currents                                                    | 40 |

| 4.2.1 General Considerations                                            |    |

| 4.2.2 Leakage Current Sources of a Dynamic Current Mirror               | 40 |

| 4.3 Noise Analysis                                                      | 44 |

| 4.3.1 General Considerations                                            |    |

| 4.3.2 Importance of Direct Noise Sources                                | 45 |

| 4.3.3 Inherent Autozeroing Effect in the Current Copier                 |    |

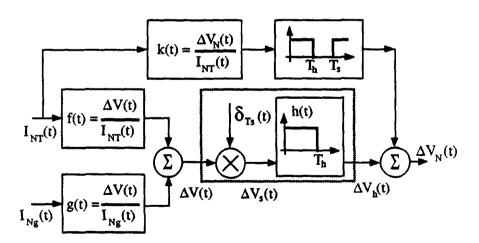

| 4.3.4 Noise Transfer Functions: F(f), G(f), K(f)                        | 50 |

| 4.3.5 Sample-&-Hold Block                                               | 52 |

| 4.3.6 Voltage Noise VN(f) & Voltage Noise Spectral Power Density        |    |

| Sv(f) on C                                                              | 54 |

| 4.3.6.1 Expressions in the Time & Frequency Domain                      | 54 |

| 4.3.6.2 Autozero Transfer Function of T <sub>m</sub>                    | 54 |

| 4.3.6.3 Voltage Noise Spectral Power Density Sv(f)                      | 56 |

| 4.3.7 Aliasing Effects                                                  | 57 |

| 4.3.7.1 Equivalent Noise Bandwidth Technique                            | 57 |

| 4.3.7.2 White Noise Aliasing                                            | 58 |

| 4.3.7.3 1/f Noise Aliasing                                              | 60 |

| 4.3.8 Noise Spectral Power Density Sv(f) in the Baseband                | 61 |

| 4.4 Charge Injection by Analog Switches                                 | 63 |

| 4.4.1 General Considerations                                            | 63 |

| 4.4.2 Interfering Parameters                                            | 63 |

| 4.4.3 Strategies                                                        | 64 |

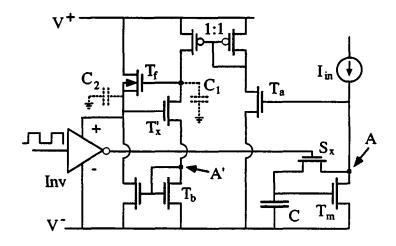

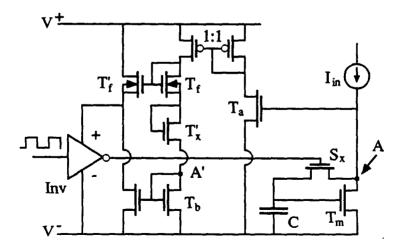

| 4.4.4 Reduction of the Turn-On Voltage $V_{GON}$ of the Sampling Switch |    |

| S <sub>x</sub>                                                          | 66 |

4.5 Summary......69

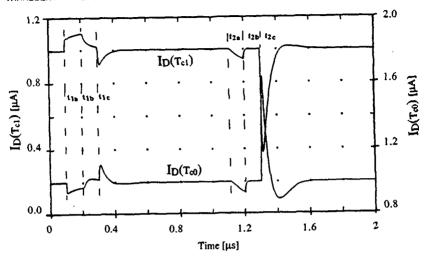

| CHAPTER 5 DYNAMIC BEHAVIOR & TRANSIENT ANALYSIS                                                                                                    | 71       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.1 Critical Switching Configurations                                                                                                              | 72       |

| 5.2 Simplified Transient Analysis                                                                                                                  | 77       |

| 5.3 Speed versus Accuracy 5.3.1 Settling Time Constant τ <sub>3</sub> 5.3.2 Speed-Accuracy Trade-Off 5.4 Summary                                   | 82<br>83 |

| CHAPTER 6 LAYOUT & DESIGN CONSIDERATIONS                                                                                                           | 85       |

| 6.1 General Considerations                                                                                                                         | 86       |

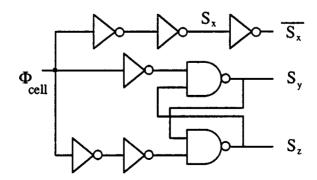

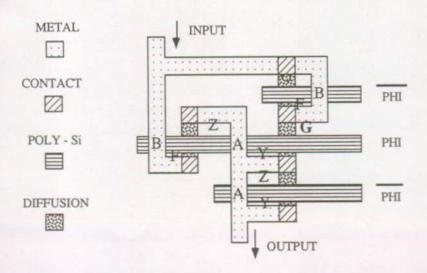

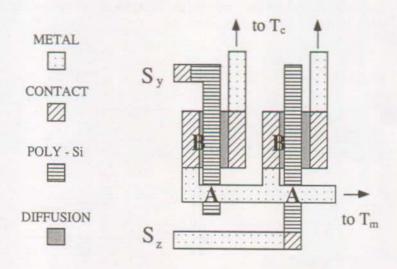

| 6.2 Cell Level  6.2.1 Clock Phase Generation with Simple Inverters  6.2.2 Clock Phase Generation with NAND/NOR Gates  6.2.3 Layout of the Switches | 87       |

| 6.3 Circuit Level                                                                                                                                  | 91       |

| 6.3 Summary                                                                                                                                        | 92       |

| CHAPTER 7 EXPERIMENTAL RESULTS & MEASUREMENTS                                                                                                      | 93       |

| 7.1 General Considerations                                                                                                                         | 94       |

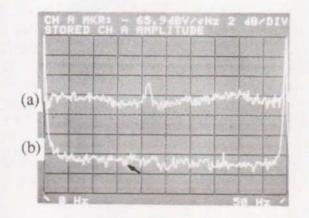

| 7.2 AC Measurements                                                                                                                                | 95       |

| 7.2.1 Variations of Input Voltage $V_{in}(t)$ and Output Current $I_{Out}(t)$                                                                      |          |

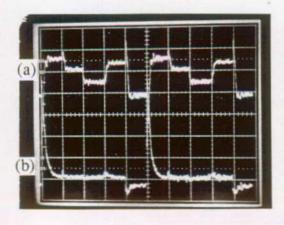

| 7.2.1.1 All Clock Phases Work Correctly                                                                                                            |          |

| 7.4.1.4 One fliase is minimally delayed                                                                                                            |          |

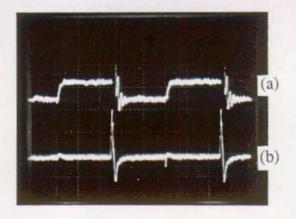

| 7.2.1.3 Basic Cell with a Reduced Transconductance gmma            | 97  |

|--------------------------------------------------------------------|-----|

| 7.2.1.4 Mismatch between Two Mirrors                               |     |

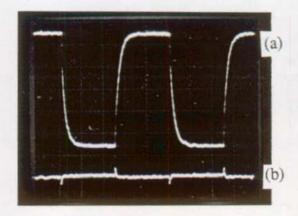

| 7.2.2 Main Time Constant $\tau_{m0}$ of the Output Cell            | 99  |

| 7.3 DC Measurements                                                | 100 |

| 7.3.1 Multiplying Mirror of Ratio 1:1, 1:2 and 1:4                 | 100 |

| 7.3.2 Basic Cell with a Reduced Transconductance $g_{mm\Delta}$    | 103 |

| 7.3.3 Multiple Current Mirror with Eight Outputs                   | 104 |

| 7.3.4 P-Type Mirror with One External Clock                        | 105 |

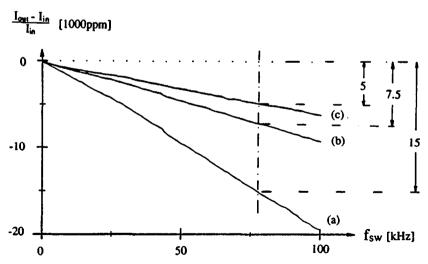

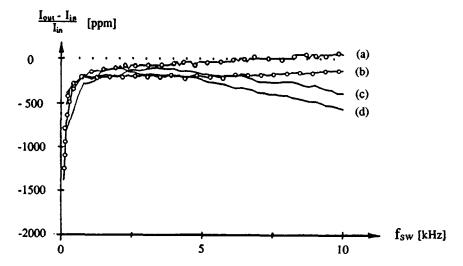

| 7.3.5 Influence of the Clock Frequency                             |     |

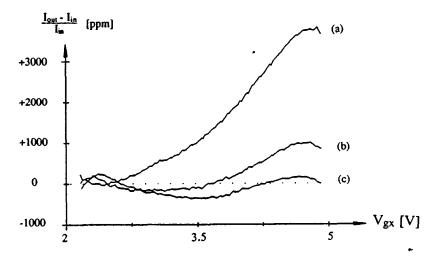

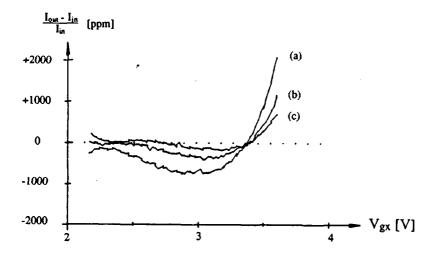

| 7.3.6 Influence of the Sampling Switch Gate-On Voltage $V_{gx}$    | 108 |

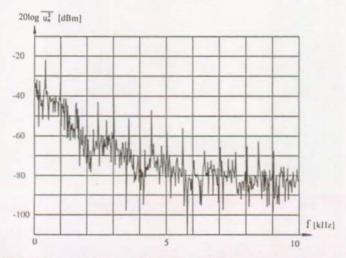

| 7.4 Noise Measurements                                             | 110 |

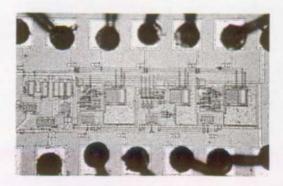

| 7.5 Die Photograph                                                 | 112 |

| 7.6 Summary                                                        | 113 |

| CHAPTER 8 APPLICATIONS                                             | 115 |

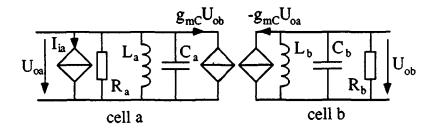

| 8.1 Continuous Time Filters                                        | 116 |

| 8.1.1 General Considerations                                       | 116 |

| 8.1.2 A 4th Order LC Coupled Bandpass Filter with Center Frequency |     |

| Mismatch                                                           | 116 |

| 8.1.3 Synthesis of the Fourth Order LC Filter                      | 121 |

| 8.1.4 Simulations and Experimental Results                         | 123 |

| 8.2 D/A & A/D converters                                           | 128 |

| 8.3 Other Applications                                             | 129 |

| 8.4 Summary                                                        | 129 |

| CHAPTER 9                                                          | 121 |

| CONCLUSIONS                                                        | 131 |

| DIDI TOCO ADVINA O DEPEDENCES                                      | 126 |

TABLE of CONTENTS XI

| APPENDICES                                                        | 143  |

|-------------------------------------------------------------------|------|

| APPENDIX A MOS MODEL, DEFINITIONS, SYMBOLS & CHARACTERISTICS      | 145  |

| & CHARACTERISTICS                                                 | 145  |

| APPENDIX B                                                        |      |

| OPEN LOOP TRANSFER FUNCTION OF THE STORAGE PHASE                  | 1/0  |

| STORAGE FRASE                                                     | ,143 |

| APPENDIX C                                                        |      |

| EQUIVALENT NOISE BANDWIDTH                                        | 153  |

| C.1 Definition                                                    | 153  |

| C.2 Equivalent White Noise Bandwidth                              | 154  |

| C.2.1 First Order Low-Pass Filter                                 |      |

| C.2.2 Second Order Low-Pass Filter                                | 154  |

| C.2.3 Real Poles:                                                 | 155  |

| C.2.4 Imaginary Poles: General Case                               | 155  |

| Example: Transfer Function $F(p)$                                 | 156  |

| C.2.5 Second Order Low-Pass with a Single Zero                    | 157  |

| Example: Transfer Function $G(p)$                                 | 157  |

| C.3 Equivalent 1/f Noise Bandwidth                                | 158  |

| C.3.1 First Order Low-Pass Filter.                                |      |

| C.3.2 Second Order Low-Pass with Real Poles                       | 160  |

| C.3.3 Second Order Low-Pass with Identical Poles                  |      |

| C.4 Approximation of the Sum $\sum_{n=N}^{+N} \frac{1}{f - nf_s}$ | 161  |

| C.5 1/f Foldover Noise in the Baseband for a First Order          | Low- |

| Pass Filter                                                       |      |

|                                                                   |      |

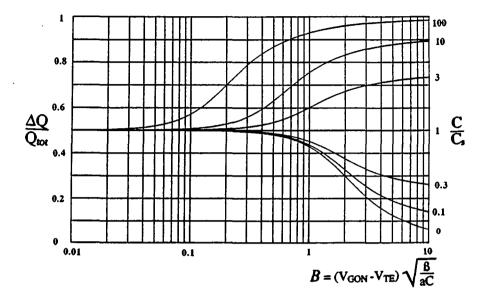

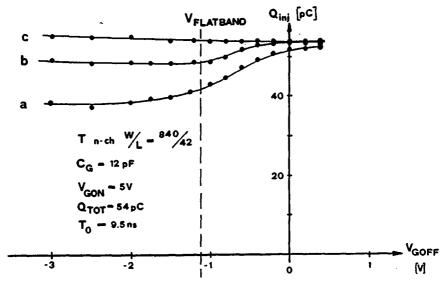

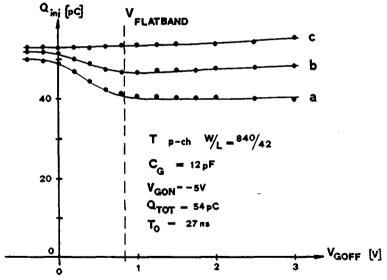

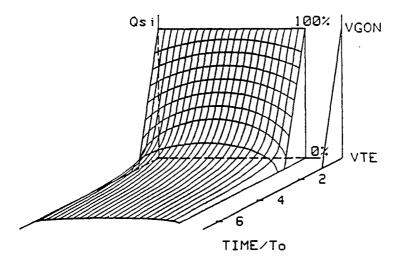

| APPENDIX D CHARGE INJECTION ANALYSIS      | 165 |

|-------------------------------------------|-----|

| D.1 General Considerations                | 165 |

| D.2 Charges Leaking to the Substrate      | 168 |

| D.3 Models                                | 170 |

| D.3.1 General Model                       |     |

| D.3.2 Simplified Model (Electrical model) |     |

| D.4 Experimental Results                  |     |

| D.5 Conclusions                           | 181 |

|                                           |     |

| CURRICUIT UM VITAE                        | 183 |

#### **CHAPTER 1**

# INTRODUCTION

In this introductory chapter the principal motivations associated with this PhD thesis, the design and analysis techniques for dynamic current mirrors, are highlighted. The errors affecting a current mirror due to the imperfections of the MOS devices are shown and well known circuit techniques developed to overcome such limitations are presented. The published results of other research laboratories working on this subject are reviewed, and finally in the conclusion of this chapter the aim and structure of this thesis are outlined.

Today's world of electronics becomes more and more digital and therefore CMOS becomes the dominant technology. A CMOS process compared to a bipolar process offers several advantages, mainly a low power consumption which is important for portable systems powered by batteries or for large systems. Another point is the smaller device geometries, which increase the number of gates that can be packed on a single chip.

Parallel to the increasing digital domain the analog field persists, because the origin of physical phenomenons and their perception is analog. Electronic sensors perceive these analog events and deliver a corresponding output signal. If this analog signal is not suitable for digital processing some analog preconditioning must be done [YEN82]. Combining both types of signal processing on the same chip to obtain the best possible performances is therefore desirable [MID84].

CMOS technology has led to a wide use of voltages and charge transfers for signal processing. As the feature sizes shrink a lower supply voltage is imposed, which reduces the dynamic voltage range of the circuits. Because process parameters are chosen to optimize digital performances, the analog functional blocks have to adapt themselves to the restricted voltage range.

Current mode circuits offer a solution to these problems as they require only a baseline digital process and avoid many of the anticipated low voltage problems by operating in the current domain [HUG89]. Due to the nonlinear current-voltage relationship the dynamic range of current-mode signals is larger than that of voltage-mode signals. Therefore the current mode approach can provide attractive and elegant solutions for many circuit and system problems [TOU90].

A ubiquitous elementary building block in most analog integrated circuits is the current mirror which is able to multiply and duplicate an imposed input current, that contains the information (bias or signal). The reproduced output current of is then available for any subsequent processing. Unfortunately, due to random process variations, transistor parameters are affected by a certain variation of the transconductance parameter and of the threshold voltage [SHY84], [LAK86]. Hence, the output currents of transistors which have been designed identically are different.

These random variations, the so-called devices mismatch, are a major limitation for most accurate and precise current mode circuit applications.

1. INTRODUCTION 3

Another main limitation of CMOS circuits is the 1/f flicker noise of the MOS transistors. The standard technique to reduce this 1/f noise and the error due to mismatch is to increase the transistor area and to overwhelm the threshold mismatch with a high gate voltage overhead, which simultaneously increases the saturation voltage of the devices.

The performance of a mirror with low saturation voltage can be improved by using lateral bipolar transistors [VIT83]. The resulting current error can be lower than 1%, but the major handicap is that only one type of mirror can be built (source or sink depending on the technology used).

Special circuit techniques allow us to reduce the inherent noise and offset in MOS amplifiers, like the chopper technique [HSI81], [ENZ89], and the autozero technique [YEN82], [DEG85]. The auto-zero technique is also used to ensure adequate biasing of CMOS inverters or analog-to-digital converters [CAN82]. Dynamic element matching [VdP76] is based on the chopper technique and shifts the error components to higher frequencies. The drawback of this technique is the high residual output ripple, which for most applications must be filtered out by using external components. Furthermore multiple mirrors are difficult to implement.

Dynamic analog techniques [VIT85.1] exploit the absence of gate current to temporarily store some analog information on the gate capacitance of the MOS device. A reported application of this analog storage capability is the dynamic comparator [YEE78] which sequentially uses the same transistor as the two devices of a differential pair. With this auto-zero technique the very notion of mismatch disappears. The achievable precision is moved to new limits and depends on the capability of accurately storage the signal, mainly limited by charge injection from the MOS transistors used as switches.

Although the idea of current sampling was formulated over ten years ago [OGU78], the first accurate implementation dates from 1988, because the circuit theory and process technology did not allow researchers to obtain the expected results. In the "Electronics Letters" issue of December 1988 [DAU88] published the idea and some simulated results, which induced a series of publications during the year of 1989. Several research laboratories have focused on the subject during the last few years, with the reported results of [GRO89] concerning D/A converters, [NAI89.2] for A/D converters, [HUG89] for current mode circuits and filters, and ourselves [VIT88], [WEG89.1] for dynamic current mirrors.

The primary objective being pursued in this dissertation is to investigate the different possibilities, to design and to analyze the performances and limitations of a new type of current mirror, a so-called dynamic mirror or current copier. The goal is to build highly accurate current mirrors in the simplest and most compact way. The best strategy for a given problem can be chosen only if all parameters influencing the circuit performances are known.

The outline of this thesis is the following:

Chapter 2 presents the principle of memorization of a current copier. The main limitations which influence the achievable accuracy are deduced and cell structures which reduce these effects derived.

In Chapter 3 the principle and the different configurations of dynamic current mirrors are extensively described, and their advantages and disadvantages discussed and compared. Possibilities of realizing multiple, multiplying and dividing current mirrors are highlighted.

Chapter 4 provides a deeper look at the different parameters, which limit the accuracy of a dynamic current mirror, namely drain voltage variations, leakage currents, noise and charge injection. The sampling of white noise and 1/f noise is analyzed and their contribution calculated. The influence of charge injection is evaluated and the interfering parameters shown.

The transient behavior is considered in **Chapter 5**, where the output spikes and the trade-off between speed and accuracy are highlighted.

Chapter 6 emphasizes layout considerations and the practical implementation of a dynamic current mirror.

Chapter 7 summarizes the experimental results obtained with such mirrors.

Chapter 8 deals with the different possible applications, focusing on a continuous time filter. The principle of D/A & A/D converters and switched current filters are outlined, and the extension to other functional blocs is suggested.

Finally Chapter 9 provides summarizing remarks and conclusions.

1. INTRODUCTION 5

A Bibliography where all the references mentioned in this thesis are listed in an alphabetical order is put at the end.

In Appendix A the MOS model, characteristics and definitions used in this thesis are listed, whereas Appendix B calculates the roots of the principal denominator of the transfer functions found in a dynamic current mirror. In Appendix C the mathematics used for noise calculations are considered. Appendix D describes the charge injection model used in this work. It is based on the analysis described in [WEG87].

These appendices are not absolutely necessary for the comprehension of the text, and are put in appendix to facilitate the reading.

|   |  | • |  |

|---|--|---|--|

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

| • |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

#### **CHAPTER 2**

# PRINCIPLE & STRUCTURES

of CURRENT COPIERS

The principle of memorizing and reproducing a current imposed by an external current source is introduced in this chapter. The notion of current copiers is defined and the parameters influencing the current accuracy are highlighted. Then the scheme of a dynamic current mirror is derived. The effect of drain voltage variations on the current precision are illustrated and structures which reduce these effects are deduced.

#### 2.1 Principle of Current Copiers

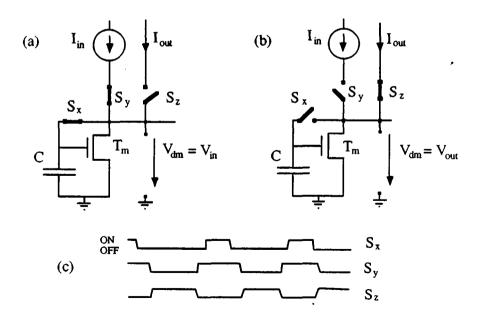

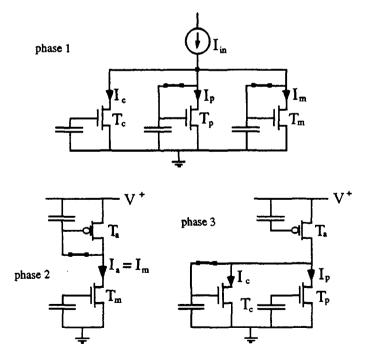

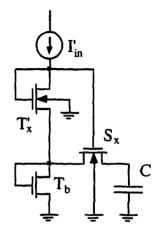

The basic cell of a dynamic current mirror [VIT88], [WEG89], which is also reported as a current copier [DAU88] or sampled current circuit [VAL89], is represented in Fig. 2.1. This simple and elegant scheme, which slightly modified is also known as the current matching concept [NAI89] or as the self-calibration technique for D/A converters [GRO89], is built of an elementary sample-&-hold circuit connected to an MOS transistor, and of a toggle switch ( $S_y$  and  $S_z$ ), which connects the device either to the input or the output.

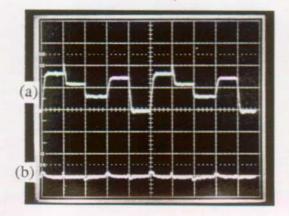

The cycle of memorizing and reproducing a current is the following:

While the switches  $S_x$  and  $S_y$  are closed {Fig. 2.1(a)}, the current source feeds the input current to the diode-connected transistor  $T_m$ . During this phase switch  $S_z$  is open. After opening sampling switch  $S_x$ , capacitor C maintains ("memorizes") the gate voltage and thus the drain current of  $T_m$  remains equal to  $I_{in}$ . When  $S_y$  is open and  $S_z$  closed {Fig. 2.1(b)}, the memorized drain current is available at the output.

Figure 2.1: Principle of a current copier or dynamic current mirror basic cell

Fig. 2.1(c) shows the corresponding clock phases. Transistor  $T_m$  works thus either as a drain-gate-connected transistor (switch  $S_x$  closed) or as an independent current source (switch  $S_x$  open).

Note that the value of the output current is independent of the parameters of transistor  $T_m$  and of linearity and hysteresis of the capacitor C. On the other hand the reproduced output current depends on the accuracy of gate voltage storage. Any error voltage  $\Delta V$  on the storage capacitor C produces an output current error  $\Delta I$

$$\frac{\Delta I}{I_{in}} = \frac{I_{out} \cdot I_{in}}{I_{in}} = \frac{g_{mm} \Delta V}{I_{in}} \tag{2.1}$$

where  $g_{mm}$  stands for the transconductance parameter of  $T_m$ .

(see Appendix A for more details on the MOS model, on the symbols and definitions used in this thesis).

#### 2.2 Principal Accuracy Limitations

The performance of the basic cell of a dynamic current mirror is limited by the following major effects:

#### (a) charge injection of the MOS transistors used as switches:

When switching off an MOS transistor, the mobile charge in the inversion charge layer is shared between drain, source and substrate [SHI87], [WEG87], [EIC89]. A part of the charge released by sampling switch  $S_x$  is added to the charge already stored on the hold capacitor C and the resulting error voltage  $\Delta V$  alters the value of the memorized drain current as shown by eq. (2.1).

#### (b) leakage currents of the reverse biased junctions:

The leakage currents at the gate node of  $T_m$  discharge the storage capacitor C. They determine the minimum switching frequency of the current copier for a given accuracy.

In the case of very low currents, the leakage currents to ground limit the absolute achievable accuracy.

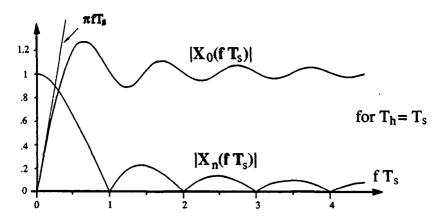

#### (c) sampled noise:

White noise is undersampled and the power spectral density of the white noise component in the baseband is increased because of additional foldover terms. 1/f noise is cancelled at low frequencies due to the inherent auto-zero technique, which introduces a double zero at the origin. It will be shown that the undersampled 1/f noise produces an increase of the white noise in the baseband.

#### (d) drain voltage variations:

Usually  $V_{in}$  is different from  $V_{out}$ . When switching  $S_y$  and  $S_z$ , hence when switching from the input to the output, the voltage difference  $V_{in}$ - $V_{out}$  is applied to the drain of  $T_m$ .

#### (d.1) transients or spikes:

When  $S_z$  is closed the output must produce some additional current to charge the parasitic capacitances at the drain of  $T_m$  to  $V_{out}$ . The resulting transients or "glitches" at the output have an amplitude which is proportional to the voltage step  $V_{in}$ - $V_{out}$ .

#### (d.2) output conductance:

An important requirement is that the reproduced current should not depend on the output voltage. As in a classical static current mirror, the finite output conductance of  $T_m$  has to be minimized to obtain an accurate current mirror.

## (d.3) capacitive divider between drain-to-gate capacitance $C_{gd}$ and C:

Gate voltage variations are produced through the capacitive divider formed with the storage capacitance C and the parasitic drain-to-gate capacitance  $C_{gd}$  of  $T_m$ .

Chapter 4 deals extensively with these "Accuracy Limitations", calculates their influences and compares their contributions.

#### 2.3 Principle of a Dynamic Current Mirror

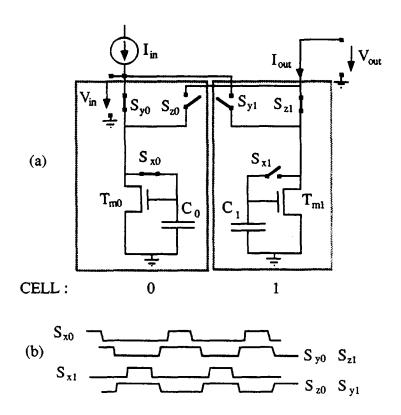

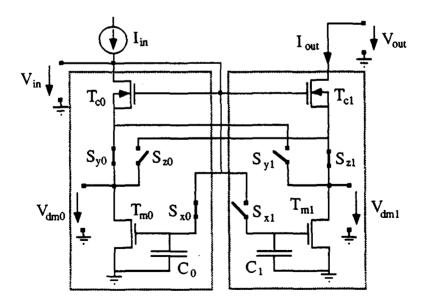

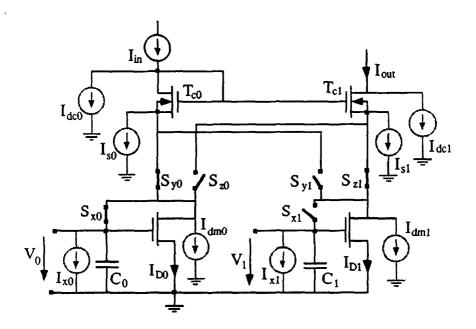

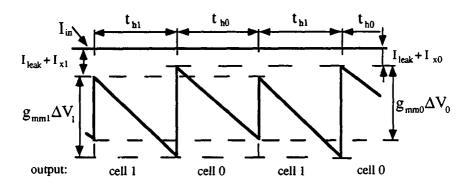

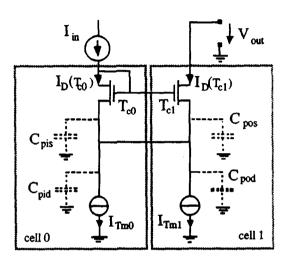

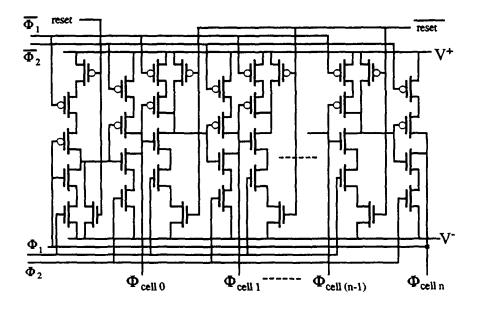

The principle of a dynamic current mirror [WEG89.1], which is capable of memorizing and reproducing an imposed current  $I_{in}$ , is shown in Fig. 2.2(a). To ensure a continuous output current, two current copiers are needed, which function with complementary clocks {Fig. 2.2 (b)}.

The switching cycle remains identical to the one mentioned in § 2.1. Each time  $S_{xj}$  is closed (j=0 or 1),  $V_{in}$  adapts to the value of gate voltage corresponding to  $I_{in}$ . Therefore  $V_{in}$  varies stepwise as a function of time with an amplitude proportional to the mismatch of  $T_{m0}$  and  $T_{ml}$ .

Figure 2.2: Principle of a dynamic current mirror operating with two current copiers

It has to be pointed out that the value of the output current  $I_{out}$  is independent of transistor and capacitor matching, hence independent of process variations.

The drain voltage of  $T_{mj}$  must return to the value  $V_{dmj} = V_{in}$  during the memorization phase {switches  $S_{xj}$  and  $S_{yj}$  closed,  $S_{zj}$  open}. When the current is restored {switches  $S_{xj}$  and  $S_{yj}$  open,  $S_{zj}$  closed}, it must jump to a value  $V_{out}$  imposed by the external load of the cell. The voltage step which occurs at the drain of  $T_m$  contributes to an important DC error through the output conductances and the parasitic drain capacitance  $C_{gd}$ .

#### 2.4 CURRENT COPIER STRUCTURES

The objective being pursued in this section is to find a structure for a current copier, which reduces the voltage variations on the drain of  $T_m$ . According to the reflections made in the precedent paragraph and in section 2.2(d),  $V_{dm}$  should remain as constant as possible in spite of the imposed voltage difference  $V_{in} - V_{out}$ .

#### 2.5.1 OP-AMP STRUCTURE

One possible solution, that performs current memorizing and restoring under constant drain voltage conditions, is based on active mirror considerations [NAI89.2], [VAL89].

During the memorization phase an operational amplifier forces the drain voltage  $V_{dm}$  to be equal to a bias voltage  $V_{bias}$ . Equilibrium is reached when the drain current of transistor  $T_m$  is equal to the input current. After copying, the cell is disconnected from the amplifier and  $V_{out} = V_{bias}$  is imposed by the op-amp. The drawback of this approach is that the output potential is fixed and therefore the principle can only be applied successfully in applications where this condition can be satisfied.

#### 2.5.2 CASCODED STRUCTURE

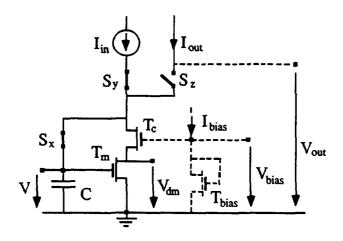

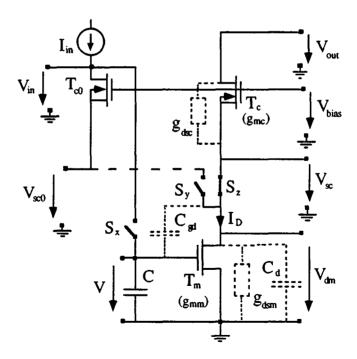

A much more elegant and simpler way of achieving a constant voltage  $V_{dm}$  is to implement a cascoded structure by means of a common-gate transistor [WEG89.1], [VIT90] in series with the main transistor  $T_m$  which leads to the solution represented in Fig. 2.3.

Figure 2.3: Cascoded current copier biased by an external current Ibias

The cascode combination of  $T_m$  and  $T_c$  is equivalent to a single transistor  $T_m$  with values of Early voltage  $V_E$  and of drain-to-gate capacitance  $C_{gd}$  increased and decreased, respectively, by a factor equal to the source to drain voltage gain of  $T_c$ . Because this gain can be as high as several hundred, the errors due to the output conductance  $g_{ds}$  and to the drain-gate capacitance  $C_{gd}$  are drastically reduced.

To increase the output dynamic range of this cell, the bias voltage  $V_{bias}$  should be as low as possible. The minimum value is given by the limit needed to keep  $T_m$  in saturation, which yields:

$$V_{bias} = V_{T0} + nV_{dm} + \sqrt{\frac{2nI_{in}}{\beta_c}} \ge V_{T0} + \sqrt{2nI_{in}} \left\{ \frac{1}{\sqrt{\beta_c}} + \frac{1}{\sqrt{\beta_m}} \right\}$$

(2.2)

with

$$V_{dm} \ge V_{dsat} = \sqrt{\frac{2I_{in}}{n\beta_m}}$$

(2.3)

Eq. (2.2) can be expressed in function of the specific current  $I_{si}$ :

$$V_{bias} \ge V_{T0} + 2n U_T \left\{ \sqrt{\frac{I_{in}}{I_{sc}}} + \sqrt{\frac{I_{in}}{I_{sm}}} \right\}$$

(2.4)

with:

$$I_{si} = 2n \beta_i U_T^2 \qquad (2.5)$$

The bias voltage  $V_{bias}$  can be produced by imposing an external current  $I_{bias}$  through a transistor  $T_{bias}$  as shown in dotted line in Fig. 2.3. The MOS voltage-current relationship in strong inversion leads to:

$$V_{bias} = V_{T0} + 2n U_T \sqrt{\frac{I_{bias}}{I_{sb}}}$$

(2.6)

Eqs. (2.4) and (2.6) yield

$$\frac{I_{bias}}{I_{sb}} \ge \left[\sqrt{\frac{I_{in}}{I_{sc}}} + \sqrt{\frac{I_{in}}{I_{sm}}}\right]^2 \tag{2.7}$$

The currents  $I_{si}$  are determined by the relative dimensions of the corresponding transistor  $T_i$ .

With the smallest possible value of  $V_{bias}$  given by eq. (2.4) the condition on  $V_{out}$  which keeps  $T_c$  in saturation is found to be:

$$V_{out} \ge 2 U_T \left\{ \sqrt{\frac{I_{in}}{I_{sm}}} + \sqrt{\frac{I_{in}}{I_{sc}}} \right\}$$

(2.8)

During the storage phase {Fig 2.1(a)}  $T_c$  and  $T_m$  must remain saturated which can be expressed by:

$$V_{T0} \ge 2 U_T \left\{ (1-n) \sqrt{\frac{I_{in}}{I_{sm}}} + \sqrt{\frac{I_{in}}{I_{sc}}} \right\}$$

(2.9)

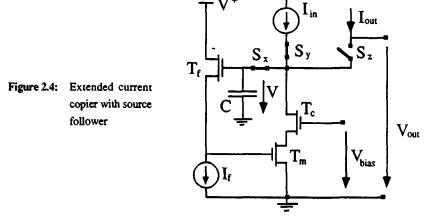

The first term of the sum on the right is usually much larger than the second one, because  $T_c$  operates as close as possible to weak inversion and  $T_m$  to strong inversion. Furthermore the first term is negative, which means that inequality of eq. (2.9) is satisfied for any positive values of threshold voltage  $V_{T0}$ . In the case that inequality (2.9) cannot be satisfied, a source follower  $T_f$  introducing a voltage shift can be placed between the storage capacitor C and the gate of  $T_m$  [DAU88], [AEB90]. Because of

storage capacitor C and the gate of  $T_m$  [DAU88], [AEB90]. Because of stability considerations the large functional capacitor C and the switch  $S_x$  must be moved from the gate of  $T_m$  to the gate of  $T_f$ . In Fig. 2.4 the now stable structure is represented with the additional current source  $I_f$  which is needed to bias  $T_f$ .

Because the voltage steps  $V_{in}$ - $V_{out}$  are still applied to  $S_y$  and  $S_z$ , the simple cascode cell configuration of figs. 2.3 & 2.4 is only applicable when the output current is used after the transients have faded out. The average current error due to the voltage step  $V_{in}$ - $V_{out}$  still reduces the DC accuracy of such a cell.

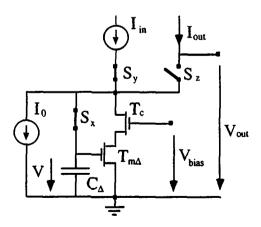

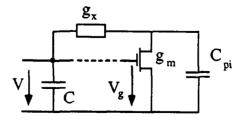

## 2.5.3 CURRENT COPIER WITH REDUCED TRANSCONDUCTANCE gmma

According to eq. (2.1) the achievable current accuracy depends linearly on the error voltage  $\Delta V$  and on the transconductance  $g_{mm}$ . To increase the current precision, the transconductance  $g_{mm}$  can be reduced by using a mirror structure with a modified basic cell, which memorizes only a current difference  $I_{in}$ - $I_0$ . This principle, which was reported as the self-

The comparison of the transfer parameter  $\beta$  and  $\beta_{\Delta}$  of two current copiers, which are built either with  $T_m$  or with  $T_{m\Delta}$  and which operate with the same gate-to-source voltage  $V_{gs}$ , leads to

$$\beta_{\Delta} = \frac{I_{in} I_{0}}{I_{in}} \beta \tag{2.10}$$

which is valid in strong inversion.

Introducing eq. (2.10) in the expression of transconductance  $g_{mm\Delta}$  of  $T_{m\Delta}$  yields:

$$g_{mon\Delta} = \sqrt{\frac{2\beta_{\Delta}(I_{in}-I_0)}{n}} = \frac{I_{in}-I_0}{I_{in}} g_{mm} \qquad (2.11)$$

But to make this improved cell work correctly, the current difference  $I_{in}$ - $I_0$  must be positive to ensure that the diode-connected n-type transistor  $T_{m\Delta}$  still is properly biased. Thus an additional current source  $I_0$  of value close to, but always smaller than  $I_{in}$ , must be available. Furthermore V must be higher than the saturation voltage of  $I_0$ .

Figure 2.5: Current copier memorizing the current difference lin-lo

Due to the lowered transconductance parameter  $g_{mm\Delta}$ , a larger voltage swing is needed to compensate for the current mismatch. Therefore, if a dynamic current mirror is built with two improved basic cells, the variations of  $V_{in}$  are increased in comparison with the variations of a normal basic cell.

#### 2.5 SUMMARY

The current copier cell which successively memorizes and reproduces a given input current was illustrated and the principle of a dynamic current mirror introduced. The principal accuracy limitations were reviewed. Structures were proposed which reduce the influence of the voltage step at the drain of  $T_m$ , while switching from the input to the output or vice versa. A structure which reduces the transconductance parameter was presented. The relations between output voltage, input current, bias current and device geometries for different configurations were calculated.

| • |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

#### **CHAPTER 3**

# DYNAMIC CURRENT MIRROR

# **CONFIGURATIONS**

In this chapter the focus is placed upon the practical implementation of dynamic current mirrors based on current copiers. Several possible structures of dynamic current mirrors performing the ratio 1:1 are presented, their advantages and disadvantages are discussed and the corresponding bias and output voltages calculated. The extension to a multiple and multiplying mirror is deduced and an algorithmic current divider is proposed.

#### 3.1 BASIC MIRROR CONSIDERATIONS

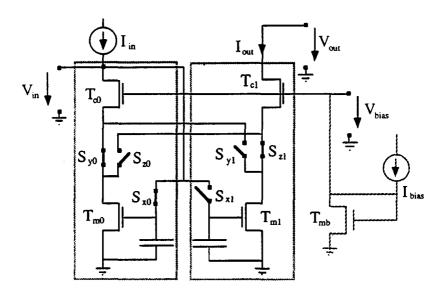

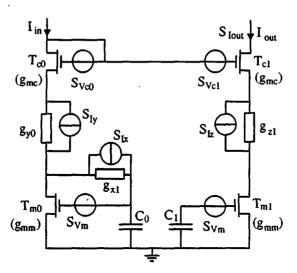

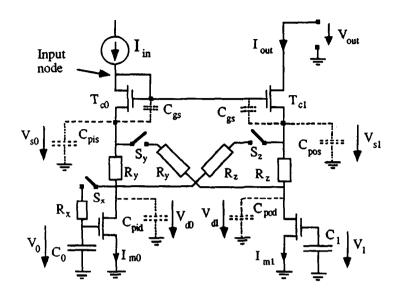

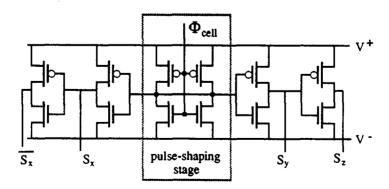

In analog design a symmetrical structure is generally preferred to an asymmetrical one, because parasitic capacitances and leakage currents are balanced, mismatch components reduced, and the layout is facilitated. According to the considerations made in §§ 2.2 & 2.3 the practical implementation of a dynamic current mirror [WEG89.1] can be deduced. The toggle switches  $S_{yj}$  and  $S_{zj}$  are placed at the sources of the common-gate transistors  $T_{cj}$  to reduce the voltage difference which appears at their terminals.

#### 3.1.1 EXTERNALLY BIASED DYNAMIC CURRENT MIRRORS

The structure of an externally biased dynamic current mirror is represented in Fig. 3.1. The condition on  $V_{bias}$  is:

$$V_{bias} = V_{T0} + nV_{dm} + \sqrt{\frac{2nI_{in}}{\beta_c}} \ge V_{T0} + 2nU_T \left\{ \sqrt{\frac{I_{in}}{I_{sc}}} + \sqrt{\frac{I_{in}}{I_{sm}}} \right\}$$

(3.1)

Figure 3.1: Dynamic current mirror which is externally biased by  $I_{bias}$

The bias circuit required for the dynamic current mirror is shown dotted.

#### 3.1.2 SELF-BIASED DYNAMIC CURRENT MIRRORS

From the externally biased mirror of Fig. 3.1 a similar, self-biased current mirror can be deduced, which is much more compact. From Fig. 3.2 it can be seen that  $V_{in}$  is connected to  $V_{bias}$  and therefore biases the common gate transistors  $T_{ci}$  [WEG89.2].

The drawback of this structure is that the two transistors  $T_{c0}$  and  $T_{c1}$  must be located in separate wells, which are connected to their sources. Otherwise the condition, which expresses that  $V_{dmj}$  (j=0,1) must be larger than the saturation voltage  $V_{dsat}$  of  $T_{mj}$ , leads to relation (3.2) which is impossible to satisfy.

$$-2U_T \sqrt{\frac{I_{in}}{I_{sc}}} > 0 \tag{3.2}$$

Figure 3.2: Self-biased dynamic current mirror with  $T_{cj}$  in separate wells

Therefore if an n-type current mirror is needed, a p-well technology must be available and vice versa for a p-type mirror.

For  $T_{c\theta}$  and  $T_{cl}$  located in separate wells, the following condition on the transconductance parameters  $\beta_i$  or on  $I_{si}$  must be fulfilled

$$\sqrt{\frac{\beta_m}{\beta_c}} = \sqrt{\frac{I_{sm}}{I_{sc}}} \le \frac{n \cdot l}{n} \tag{3.3}$$

For the limiting value of relation (3.3) the output voltage  $V_{out}$  is found to be:

$$V_{out} \ge 2U_T \left\{ n \sqrt{\frac{I_{in}}{I_{sm}}} + (I - n) \sqrt{\frac{I_{in}}{I_{sc}}} \right\}$$

(3.4)

Sometimes inequality (3.3) cannot be satisfied or, because of the technology, it is not possible to implement separate wells. In this case, the connection of  $S_{xj}$  of the self-biased dynamic current mirror of Fig. 3.2 must be modified to obtain the structure of a compact mirror represented in Fig. 3.3, a so-called "stacked" mirror structure [WEG89.1].

The drawback of this structure is its relatively high saturation voltage which increases  $\dot{V}_{out}$  given by

$$V_{out} \ge V_{T0} + 2U_T \{ n \sqrt{\frac{I_{in}}{I_{sm}}} + \sqrt{\frac{I_{in}}{I_{sc}}} \}$$

(3.5)

which is more than a threshold voltage higher than  $V_{out}$  given by eq. (3.4). Note that eq. (3.5) remains valid whether  $T_{c0}$  and  $T_{c1}$  are in a separate well or not. Normally the first term of relation (3.5) is dominant because  $T_{mj}$  is biased in strong inversion, whereas  $T_{cj}$  operates as close as possible to weak inversion [VIT89].

Due to the two diode-connected transistors, which impose the voltages, the "stacked" mirror is uncritical even for a large current range. The devices of the input branch always remain in the saturated mode independently of the dimensions of the transistors.

Figure 3.3: Self-biased, so-called "stacked" dynamic current mirror

Table 3.1 recapitulates the minimum output voltages  $V_{out}$  of the different structures mentioned in §§ 3.1.1 and 3.1.2.

| Mirror of:               | Minimal Output Voltages $V_{\it Out}$                                                  | Particular Conditions                                                                                      |  |

|--------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| Fig. 3.1:<br>ext. biased | $2U_T \left\{ \sqrt{\frac{I_{in}}{I_{0m}}} + \sqrt{\frac{I_{in}}{I_{0c}}} \right\}$    | $V_{bias} \ge V_{T0} + 2nU_T \left\{ \sqrt{\frac{I_{in}}{I_{sc}}} + \sqrt{\frac{I_{in}}{I_{sm}}} \right\}$ |  |

| Fig. 3.2:<br>self-biased | $2U_T\left\{n\sqrt{\frac{I_{in}}{I_{0m}}} + (1-n)\sqrt{\frac{I_{in}}{I_{0c}}}\right\}$ | $\sqrt{\frac{I_{sm}}{I_{sc}}} \le \frac{n-l}{n}$                                                           |  |

| Fig.3.3:                 | $V_{T0} + 2U_T \{ n \sqrt{\frac{I_{in}}{I_{0m}}} + \sqrt{\frac{I_{in}}{I_{0c}}} \}$    | None                                                                                                       |  |

Table 3.1: Comparison of the minimal output voltages  $V_{out}$  of the different structures

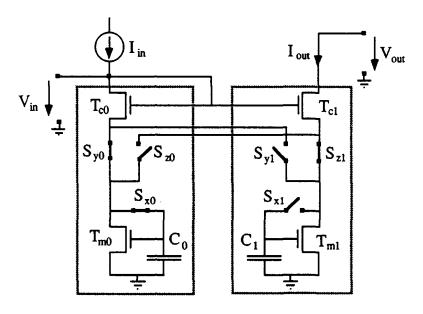

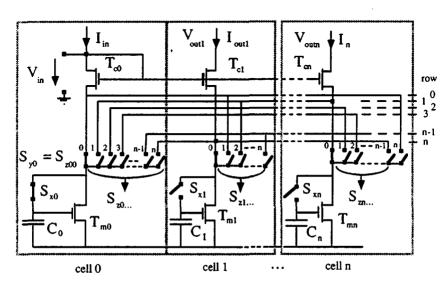

# 3.2 MULTIPLE AND MULTIPLYING MIRRORS

# 3.2.1 MULTIPLE CURRENT MIRRORS (1:1: . . :1)

A multiple dynamic current mirror with n identical current outputs is obtained by simply repeating n-times the cascoded current copier, which involves a total of (n+1) copiers.

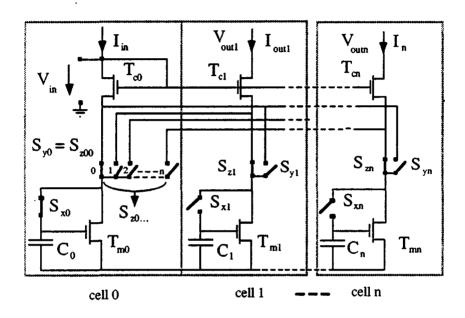

Figure 3.4: Multiple "stacked" dynamic current mirror according to strategy (a)

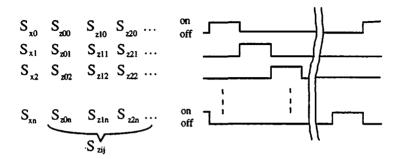

Figure 3.5: Clock phases for the dynamic current mirror of Fig. 3.4

The two following switching strategies are possible, which lead to slightly different circuit schemes:

- (a) all current copiers are identical and sweep sequentially each output while delivering the stored current, meaning that during a switching cycle every cell is connected once to each of the outputs.

- (b) all current copiers, except copier 0, are identical and are connected to their corresponding output, or in other words copier 1 is always delivering the current to output 1, copier 2 to output 2, etc.. In opposition to strategy (a) only copier 0 is sweeping all the outputs and is delivering the output current in place of the cell that is being updated.

# Let us first consider strategy (a):

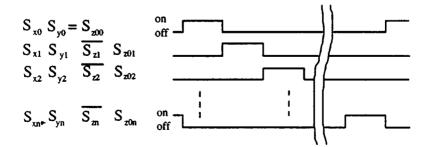

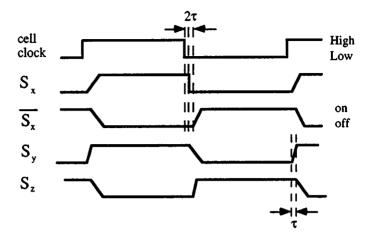

A corresponding self-biased and stacked circuit scheme, which is based on the dynamic current mirror of Fig. 3.3, is represented in Fig. 3.4 and the corresponding clock phases in Fig. 3.5.

Because the (n+1) current copiers sweep each output an averaging effect occurs, which can increase the DC accuracy of the output currents. On the other hand, glitches are present (n+1) times during a switching cycle, because (n+1) current sources are connected to every output. The increase in DC accuracy obtained by the averaging effect is degraded due to these additional transients [WEG90.2].

The number of additional connections and the number of clock phases per cell increase linearly with the number of outputs (see table 3.2), which results in an important increase in size of each current copier.

From Fig. 3.5 it can be seen that each clock must drive n times the switches  $S_{zij}$   $(j\neq i)$ , once  $S_{yj}$  (or  $S_{zii}$ ) and once  $S_{xj}$ , which corresponds to a total of (n+2) switches. This large capacitive load influences the slope of the clocks which degradation has to be counterbalanced by an adequate increase of size of the corresponding clock drivers.

The large number of connections and clock phases, hence the chip size, can be reduced with the help of strategy (b). The corresponding self-biased "stacked" mirror and the switching sequence are shown in Fig. 3.6 and 3.7,

respectively. All the cells are identical, except cell 0, and each cell delivers the current to only one specific output, which reduces drastically the number of clock phases and connections.

Figure 3.6: Multiple "stacked" dynamic current mirror according to strategy (b)

Figure 3.7: Clock phases corresponding to the mirror of Fig. 3.6

The number of connections of an output cell is independent of n and remains equal to that of a current copier. The clock phases driving the switches  $S_{yj}$  and  $S_{zj}$  are complementary. The switches  $S_{zoj}$  are driven by the same clocks as  $S_{yj}$ , which simplifies the control logic of a mirror based on strategy (b).

Table 3.2 shows how an output cell of the multiple current mirror of Fig. 3.4 and Fig. 3.6 is modified as a function of the number of outputs n. An output cell of the multiple current mirror of Fig. 3.6 is independent of n and only the number of switches  $S_{zoj}$  varies as a function of the number of outputs. Approach (b) leads to a much simpler and more compact multiple current mirror than approach (a), with the only drawback being that cell 0 is slightly different from the other cells.

Note that it is also possible to build multiple dynamic mirrors with other mirror structures (Figs. 3.1 & 3.2) or with variations of the current copier, as proposed in chapter 2.

|                                       | strategy (a): Circuit of Fig. 3.4 | strategy (b): Circuit of Fig. 3.6 |

|---------------------------------------|-----------------------------------|-----------------------------------|

| no. of clock phases<br>per cell       | n+1+1                             | 3                                 |

| no of additional connections per cell | 2 (n - 1)                         | 0                                 |

| additional capacitance<br>at drain    | (n - 1) C <sub>Sz</sub>           | 0                                 |

| transients per<br>switching cycle     | (n+1)                             | 2                                 |

| switches driven by<br>each clock      | n+1+1                             | 3                                 |

Table 3.2: Comparison of the number of connections of strategy (a) & (b)

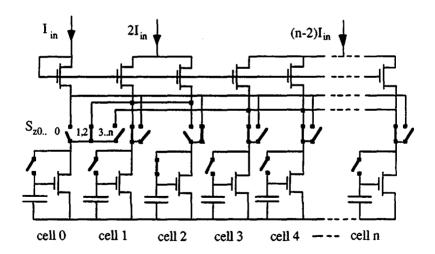

#### 3.2.2 MULTIPLYING CURRENT MIRRORS (1:m:n)

Obviously the n continuous output currents of § 3.2.1 can be added to realize a (1:m:n) multiplying dynamic current mirror. Fig. 3.8 shows such a mirror with two outputs of value  $2I_{in}$  and  $(n-2)I_{in}$ .

This mirror is based on strategy (b) or in other words, current copier 0 always takes the place of the cell which is updated. For the clock phase which is represented in Fig. 3.8, cell 0 is connected to the output labeled  $2I_{in}$ , while current copier 2 is being updated. It can be seen that the number of interconnections has been reduced by sharing the sources of the common-gate output transistors  $T_{cj}$  (j=1, 2) and  $T_{cj}$  (j=3...n). Furthermore, this approach avoids the need to split  $S_{20j}$  into several switches. Because the switches  $S_{20j}$  (j=1, 2) and  $S_{20j}$  (j=3...n) are replaced by  $S_{202}$  and  $S_{20n}$ , respectively, the control logic of these two switches is slightly modified.

The clock of  $S_{z02}$  is simply the "AND"-function of the clocks which activate cells 1 and 2, and, consequently, the clock controlling  $S_{z0n}$  is the "AND"-function of the clocks of the cells 3, 4,... and n.

Figure 3.8: Self-biased, stacked multiplying dynamic current mirror with two outputs; one of value  $2I_{in}$  and one of value  $(n-2)I_{in}$ .

# 3.3 DIVIDING CURRENT MIRRORS

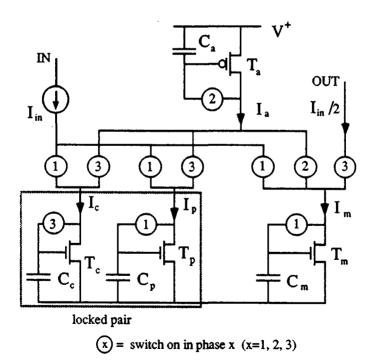

# 3.3.1 PRINCIPLE OF THE DIVISION BY 2 ( $I_{out} = \frac{I_{in}}{2}$ )

Due to the unavoidable transistor mismatch, it is not possible to divide a current  $I_{in}$  accurately by simply connecting n current copiers in parallel, since the input current would not be evenly shared among them.

With the help of the calibration scheme shown in Fig. 3.9 [ROB89.2], which performs a division by two, exactly half the input current can be forced to flow through the main transistor  $T_m$ , which delivers the output current. Transistor  $T_p$  and calibration transistor  $T_c$  form a so-called "locked pair" of transistors, since their output current sum equals the one of  $T_m$ .

Figure 3.9: Accurate divide-by-two dynamic current mirror: complete schematics

The circuit operates in three clock phases and the output current requires a few cycles to reach the correct current values. In Fig. 3.9 each switch is symbolized by a circled number, that indicates its phase of conduction. Each transistor can be connected either in a diode configuration (when a new current value is stored) or as an independent current source (when it reproduces the previously memorized current).

For the sake of clarity, the three different phases are represented explicitly in Fig. 3.10, where only the transistors which are active during the corresponding phase are represented.

The principle of accurate current division is the following:

During phase 1, transistors  $T_m$  and  $T_p$  share the input current  $I_{in}$  from which the previously established calibration current  $I_c$  is subtracted.

Thus, for cycle k:

$$I_{mk} = \frac{I_{ink} - I_{c(k-1)}}{2} (1 + \varepsilon) \tag{3.6}$$

$$I_{pk} = \frac{I_{ink} - I_{c(k-1)}}{2} (1 - \varepsilon) \tag{3.7}$$

where  $\varepsilon$  represents the mismatch between  $T_m$  and  $T_p$ . Note that for the first cycle (k=1), current  $I_{cl}$  of  $T_c$  is arbitrarily set to zero. Both currents,  $I_{mk}$  and  $I_{pk}$ , are memorized as voltages on the capacitors  $C_m$  and  $C_p$ , respectively.

During phase 2, the stored current  $I_{mk}$  is forced into the p-type transistor  $T_a$ , hence:

$$I_{mk} = I_{ak} \tag{3.7}$$

During phase 3, the difference between current  $I_{ak}$  and  $I_{pk}$ , which is memorized by  $T_p$ , is stored in  $T_c$  as the new value of the calibration current  $I_{ck}$ :

$$I_{ck} = I_{mk} \cdot I_{pk} = \varepsilon \left( I_{ink} \cdot I_{c(k-1)} \right) \tag{3.8}$$

Because in Fig. 3.9  $T_c$  is a current sink,  $I_{ck}$  can only flow towards ground. This additional constraint on  $I_{ck}$  reduces the complexity of the circuit. It

avoids the use of  $T_c$  either as a current sink or a current source, and it also avoids the corresponding control-logic. Since  $I_{ck}$  is positive,  $T_m$  and  $T_p$  must be designed to ensure  $\varepsilon > 0$ .

The evolution of the calibration current  $I_{ck}$  can be obtained by introducing z-transforms into eq. (3.8), which yields:

$$I_c(z) = \frac{z\varepsilon}{z+\varepsilon} I_{in}(z) \tag{3.9}$$

Introducing  $I_{in}(t) = I_{in}$  while  $t \ge 0$  leads to:

$$I_c(z) = \frac{z\varepsilon}{z+\varepsilon} \frac{z}{z-1} I_{in}$$

(3.10)

Figure 3.10: Accurate divide-by-two dynamic current mirror: scheme showing the different configurations for each phase

which yields the asymptotic or equilibrium value  $I_{c\infty}$  of calibration current  $I_c$ :

$$I_{c_{\infty}} = \lim_{z \to 1} (z - 1) I_{c}(z) = \frac{\varepsilon}{I + \varepsilon} I_{in}$$

(3.11)

The equilibrium value of the output current  $I_{m\infty}$  can be found either by introducing  $I_{c\infty}$  in eq. (3.5) or by taking the z-transform of  $I_{mk}$  which leads to:

$$I_{m\infty} = \lim_{z \to 1} (z-1) I_m(z) = \lim_{z \to 1} (z-1) \frac{z(1+\varepsilon)}{2(z+\varepsilon)} I_{in}(z) = \frac{I_{in}}{2}$$

(3.12)

which is independent of the mismatch  $\varepsilon$ . This equilibrium is reached exponentially with a time constant  $\tau$  [ROB89.2], [VIT90]

$$\tau = -\frac{1}{\ln(\varepsilon)} \ [cycles] \tag{3.13}$$

For example,  $\tau$  is equal to 0.33 and 0.43 [cycles], while  $\varepsilon$  = 5% and  $\varepsilon$  = 10%, respectively.

Therefore, after a few cycles the current  $I_{mk}$  settles to the desired value of  $I_{in}/2$ . Obviously the sum of the asymptotic values of the locked-pair corresponds also to half the input current. After the steady state is reached, the three-phase-cycle proceeds to update the stored voltages, which prevents the influence of leakage currents.

If the output current has to be available continuously,  $T_m$  and  $T_c$  must then be duplicated. It is also possible to duplicate only  $T_m$ . Then  $T_c$  must adapt its current to each  $T_m$ , which increases the time necessary for the updating of the current  $I_m$ .

Table 3.3 gives numerical values of  $I_m$  and  $I_c$  during phase 1 for two values of mismatch,  $\varepsilon = 5\%$  and  $\varepsilon = 10\%$ .

|     | $\varepsilon$ = 0.05 |            | $\varepsilon = 0.10$ |            |

|-----|----------------------|------------|----------------------|------------|

| k = | $I_{m(k)}$           | $I_{c(k)}$ | $I_{m(k)}$           | $I_{c(k)}$ |

| 0   | .525                 | 0          | .55                  | 0          |

| 1   | .49875               | .05        | .495                 | .1         |

| 2   | .50006               | .0475      | .5005                | .09        |

| 3   | .49999               | .04763     | .49995               | .091       |

| 4   | .5                   | .04762     | .50001               | .0909      |

| 5   | .5                   | .04762     | .5                   | .09091     |

| 6   | .5                   | .04762     | .5                   | .09091     |

Table 3.3: Evolution of  $I_{mk}$  and  $I_{ck}$  for two mismatch values  $\varepsilon$  between  $T_m$  and  $T_p$

# 3.3.2 DIVISION BY ANY INTEGER NUMBER (1/n)

This principle can be extended to any integer value n > 2 by using (n-1) "locked pairs" of transistors  $T_{pi} - T_{ci}$ . This involves the splitting of phase 3 into (n-1) phases, which are necessary to update each calibration transistor  $T_{cj}$  of the locked pair. The total number of phases needed is then (n+1), and the output current  $\frac{I_{in}}{n}$  of  $T_m$  is available while all the locked-pairs are calibrated, thus during a fraction  $\frac{n-1}{n+1}$  of the calibration cycle.

# 3.4 SUMMARY

The practical implementation of a dynamic current mirror of 1:1 ratio was investigated, which was built with two identical current copiers or basic cells. The gates of the input transistor  $T_{c0}$  and of the output transistor  $T_{c1}$  are connected together in a common-gate transistor configuration to reduce the drain voltage variations of the common-source transistors. The toggle switch is placed at the sources of the common-gate transistor, which reduces the amplitude of the transients and increases the DC current

accuracy. Externally biased dynamic current mirrors and two type of self-biased current mirrors were presented and their output voltage range were compared to each other. Two switching strategies which perform accurate multiple current outputs were studied, and the influence on the circuit complexity as a function of the number of current outputs was shown. The structure, which is more compact, was used to obtain a multiplying current mirror. Finally, the algorithm of an accurate divide-by-two current mirror was proposed and its asymptotic values were calculated. Its extension to any integer value was mentioned.

# **CHAPTER 4**

# **ACCURACY LIMITATIONS**

The accuracy limitations mentioned in chapter 2 are investigated and their influences on the circuit performance are studied. First the effect of drain voltage variations on the current accuracy are analyzed. Then the contribution of the different leakage currents to the gate voltage error is illustrated. A detailed analysis focusing attention upon both white and 1/f noise is presented. The noise spectral power density and the noise voltage at the gate node is calculated in the baseband, and the contributions of the different noise sources and their aliasing effects are highlighted. Finally the charge injection phenomenon is outlined and some strategies which reduce the influence of this effect are proposed.

# 4.1 INFLUENCE OF DRAIN VOLTAGE VARIATIONS

# 4.1.1 OUTPUT CONDUCTANCE gds

Channel length modulation contributes to an important current error, which can be represented by the drain-to-source conductance  $g_{ds}$ .

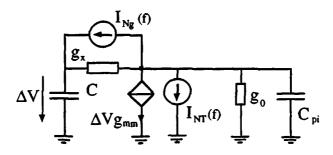

The cascoded structures presented in chapter 2 decrease the drain-to-source conductance  $g_{ds}$  of a current copier by the cascode gain. If the common-gate transistors  $T_{cj}$  and  $T_c$  are located in separate wells (Fig. 4.1), the total output conductance  $g_{ds}$  of a cell is found to be:

$$g_{ds} = g_{dsm} \frac{g_{dsc}}{g_{mc}} \tag{4.1}$$

Figure 4.1: Parasitic capacitances and conductances (dashed) of the current copier

If a common well is used, the transconductance  $g_{mc}$  is replaced by  $ng_{mc}$ , where n is typically between 1.5 and 2 and tends asymptotically to 1 with increasing gate voltage. Furthermore a supplementary term  $g_{dc}$  is added, which represents the conductance of the drain to the bulk of  $T_c$  [VIT89].

Thanks to the cascoded structure, the fraction of the output voltage  $\Delta V_{out}$  which is transmitted to the drain of  $T_m$  and which produces drain variations  $\Delta V_{dm}$ , is reduced to

$$\Delta V_{dm} = \Delta V_{out} \frac{g_{dsc}}{g_{mc}} \tag{4.2}$$

Again if a common well is used, the transconductance  $g_{mc}$  is replaced by  $ng_{mc}$ . The resulting current error can be expressed as:

$$\frac{\Delta I}{I_D} = \frac{g_{dsm}}{I_D} \Delta V_{dm} = \frac{\Delta V_{dm}}{V_E} = \frac{g_{dsc} \Delta V_{out}}{g_{mc} V_E}$$

(4.3)

with the Early voltage  $V_E$  given by

$$V_E = \lambda L_{ef} \tag{4.4}$$

$V_E$  is of the order of tens of volts and therefore steps of some hundred millivolts of  $V_{out}$  would produce an output current error of about 1% without a cascoded structure.

$T_c$  lowers the effect of output voltage variations on the current accuracy, but there still remains a small voltage difference  $V_{sc}$ - $V_{sco}$ , which is minimized if  $T_c$  and  $T_{c0}$  are matched.  $V_{bias}$  was calculated in § 3.1.

# 4.1.2 CAPACITIVE DIVIDER C<sub>sd</sub> - C

When switching  $S_y$  and  $S_z$  a voltage step proportional to  $V_{sc}$ - $V_{sco}$  is applied to the drain of  $T_m$ . A fraction  $\Delta V$  is transferred to the capacitance C through the capacitive divider formed by the gate-to-drain capacitance  $C_{gd}$  and C. The resulting current error  $\Delta I$  is:

$$\Delta I = g_{mm} \Delta V = \frac{g_{mm} C_{gd} (V_{sc} - V_{sco})}{(C + C_{gd})}$$

$$\tag{4.5}$$

#### 4.1.3 OPTIMIZATION OF THE RATIO CG/C

The optimum is calculated for a given value of the storage capacitance C and for a given value of transconductance  $g_{mm}$ , hence of a fixed ratio  $\frac{W_{ef}}{L_{ef}}$ . An increase of the effective channel length  $L_{ef}$  reduces the current error  $\Delta I$  due to  $g_{dsm}$  according to eq. (4.3), but increases  $\Delta I$  due to  $C_{gd}$  {eq. (4.5)}, because the effective channel width  $W_{ef}$  must be modified to maintain the desired ratio. Both current errors can be written explicitly in function of the stored drain current  $I_D$  and of drain voltage variations  $\Delta V_{dm}$

$$\Delta I = g_{mm}\Delta V + g_{dsm}\Delta V_{dm} = \Delta V_{dm}I_D \left\{ \frac{2}{(V-V_{T0})} \frac{C_{gd}}{(C+C_{gd})} + \frac{1}{\lambda L_{ef}} \right\}$$

(4.6)

The total capacitance C at the gate node can be split into the gate capacitance  $C_G$  and into an additional capacitance  $C_{ad}$ .

$$C = C_G + C_{ad} = W_{ef} L_{ef} C'_{ox} (1 + \xi)$$

(4.7)

with

$$\xi = \frac{C_{\alpha l}}{C_G} = \frac{C_{\alpha l}}{W_{ef} L_{ef} C_{ox}}$$

(4.8)

If  $T_m$  works in strong inversion,  $W_{ef}$  can be extracted from the transfer parameter  $\beta_m$ . Then with the help of eq. (4.7)  $L_{ef}$  can be expressed as:

$$L_{ef} = (V - V_{T0}) \sqrt{\frac{\mu C}{2nI_D(I + \xi)}}$$

(4.9)

Replacing in eq. (4.6) and assuming  $C \sim C_{8d}$  yields after differentiation to an optimum value  $\xi_{opt}$ :

$$\xi_{opt} = \frac{2\lambda L_{ov}}{V - V_{TO}} - I \tag{4.10}$$

which can also be expressed as:

$$\left\{\frac{C_G}{C}\right\}_{opt} = \frac{V - V_{T0}}{2\lambda L_{ov}} = \frac{I_{in}}{g_{mm} \lambda L_{ov}} \tag{4.11}$$

Typical numerical values for the parameters above are (for a standard  $3\mu$  CMOS process):

$$L_{ov} = 0.5 \mu m \qquad \lambda = \frac{5V}{\mu m} \qquad V - V_{T0} = 0.5V$$

which leads to:

$$\xi_{out} = 9$$

In this case the auxiliary capacitor should be nine times larger than the gate capacitance, or in other words  $T_m$  must be sized to obtain  $C_G$  equal to 10% of C.

#### 4.1.4 DIRECT CHARGE FLOW PATH

A third effect is due to the additional charge that is supplied from the output to charge the parasitic capacitances  $C_{gd}$  and  $C_d$ . When  $S_z$  has just been closed voltage  $V_{dm}$  changes from  $V_{sc0}$  to  $V_{sc}$ . Thus the current copier cell has just been switched from the input to the output. When switching back to the input  $(S_x$  and  $S_y$  closed,  $S_z$  open) the voltage  $V_{dm}$  is forced to  $V_{sc0}$  again and this additional charge is drained from the parasitic capacitances. This charge creates a current transient (current "glitch" or spike), which has no importance if the output current is only used after equilibrium is reached. However, if the current must be available continuously, these glitches are not acceptable. Furthermore they produce a DC error in the average output current given by:

$$\Delta I = f_{sw} (V_{sc} - V_{sc0}) (C_d + \frac{CC_{ed}}{C + C_{ed}})$$

(4.12)

where  $f_{sw}$  is the switching frequency [WEG89.2], [WEG90.2].

Chapter 5 "Dynamic Behavior & Transient Analysis" deals extensively with the origin of these glitches and shows their effects.

# 4.2 LEAKAGE CURRENTS

#### 4.2.1 GENERAL CONSIDERATIONS

The input and the output currents are affected by the parasitic leakage currents of several reverse-biased pn-junctions flowing to ground. These leakage currents  $l_j$  are due to the generation of electron-hole pairs in the depletion region of the pn-junctions. They are proportional to the depletion-layer width and charge, and therefore depend on the applied reverse bias  $V_{rev}$ , as shown by eq. (4.13) [SZE81].

$$I_j \quad \alpha \quad \left(I + \frac{V_{revi}}{V_{bi}}\right)^{m} \tag{4.13}$$

with built-in potential

$$V_{bi} = U_T \ln\left(\frac{N_A N_D}{n_i^2}\right)$$

(4.14)

where m = 1/2 for an abrupt junction and 1/3 for a linearly graded junction.  $N_A$  and  $N_D$  are the acceptor and donor concentrations, respectively, and  $n_i = 1.45 \cdot \frac{10^{10}}{\text{cm}^3}$  corresponds to the intrinsic carrier concentration of silicon at 300K.

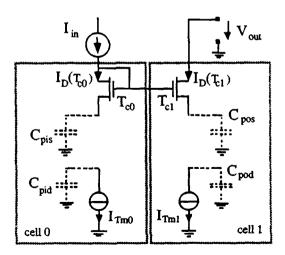

These leakage currents can be represented by current sources connected between the corresponding node and ground according to Fig. 4.2, which represents the self-biased stacked dynamic current mirror of Fig. 3.2.

Note that the leakage currents of the capacitances are negligible in comparison to that of the pn-junctions.

#### 4.2.2 LEAKAGE CURRENT SOURCES OF A DYNAMIC CURRENT MIRROR

Let us first assume that the on conductance  $g_{xj}$  of the sampling switch  $S_{xj}$  is negligible. During the storage phase the stored drain current  $I_{Dj}$  (j=0,1) is the difference between  $I_{in}$  and the leakage current sources, hence (according to Fig. 4.2)

$$I_{Di} = I_{in} - I_{dc0} - I_{s0} - I_{dmi} - I_{xi}$$

(4.15)

Figure 4.2: Different leakage current sources of a dynamic current mirror

where  $I_{xj}$  corresponds to the leakage currents at the gate node of  $T_{mj}$   $I_{dmj}$  corresponds to the sum of the leakage currents at the drain node of  $T_{mj}$ , whereas  $I_{dc0}$  and  $I_{s0}$  stand for the leakage currents of  $T_{c0}$  at the source and the drain node, respectively.

During the restoring or copying phase  $t_{hj}$  the output current is

$$I_{out}(t) = I_{Di}(t) + I_{dmi} + I_{sl} + I_{dcl}$$

(4.16)

where the stored drain current  $I_{Dj}(t)$  has become time dependent because of  $I_{xj}$  which discharges  $C_j$ . As a consequence, the gate voltage  $V_j$  varies linearly as a function of time t as shows Fig. 4.3. The gate voltage variations are supposed sufficiently small so that the small signal parameter  $g_{mmj}$  can be used. Introducing

$$I_{leak} = -I_{dc0} + I_{dc1} - I_{s0} + I_{s1}$$

(4.17)

the output current  $I_{outj}(t)$  can be expressed as

$$I_{outj}(t) = I_{in} + I_{leak} - I_{xj} - g_{mmj} \frac{I_{xi}}{C_i} t$$

(4.18)

Integrating eq. (4.18) over a time period  $t_{h0}+t_{h1}$  leads to an average output current  $\overline{\Delta I_{out}}$ :

$$\overline{\Delta I_{out}} = I_{in} + I_{leak} - \frac{1}{t_{h0} + t_{h1}} \left\{ t_{h0} I_{x0} + t_{h1} I_{x1} + \frac{g_{mm0} I_{x0}}{2 C_0} t_{h0}^2 + \frac{g_{mm1} I_{x1}}{2 C_1} t_{h1}^2 \right\} (4.19)$$

If both current branches are matched term  $I_{leak}$  is cancelled out because  $I_{dc0} = I_{dc1}$  and  $I_{s0} = I_{s1}$ . For  $t_{h0} = t_{h1} = T_h$ ,  $I_{x0} = I_{x1} = I_x$ ,  $g_{mm0} = g_{mm1} = g_{mm}$  and  $C_0 = C_1 = C$  the current error  $\Delta I$  due to leakage currents simplifies to

$$\Delta I = \overline{\Delta I_{out}} - I_{in} = -I_x \left\{ 1 + \frac{T_h g_{mm}}{2 C} \right\}$$

(4.20)

which shows clearly the limitation of the achievable accuracy due to the leakage current  $I_x$  of the sampling switch. The last term also sets a limit to the maximum duration  $T_h$  of the copying phase. A final limitation for very low currents still remains because of  $I_x$ .

Figure 4.3: Waveform of  $I_{out}$  for  $I_{in}$  = const. due to leakage currents while cell j is connected to the output

The voltage drop on the sampling switch conductance  $g_x$  due to the leakage current  $I_x$  may not be negligible during the storage phase. Assuming  $g_x > g_0$ , the drain voltage  $V_{dm}(t)$  and the gate voltage V(t) are affected as follows:

$$V(t) = V - \frac{T_h I_x}{C} e^{-t/\tau} + \frac{I_x}{g_{mm}} (e^{-t/\tau} - I)$$

(4.21)

$$V_{dm}(t) = V + I_x \frac{g_{mm} \cdot g_x}{g_x} \left\{ \frac{T_h}{C} e^{-it\tau} - \frac{(e^{-it\tau} - I)}{g_{mm}} \right\}$$

(4.22)

$$\tau = \frac{C}{g_{mm}} \tag{4.23}$$

Note that voltage V corresponds to the gate voltage at equilibrium while  $g_x > g_{mm}$  and that the drain capacitance  $C_d$  was neglected.

At time t=0 and  $t->\infty$  eqs. (4.21) & (4.22) lead to

$$V(0) = V - \frac{T_h I_x}{C}$$

$V(t > \infty) = V - \frac{I_x}{g_{mm}}$  (4.24)

$$V_{dm}(0) = V + I_x \frac{g_{mm} \cdot g_x}{g_x} \frac{T_h}{C} \qquad V_{dm}(t - \infty) = V + I_x \frac{g_{mm} \cdot g_x}{g_x g_{mm}}$$

(4.25)

Eq. (4.24) shows that the leakage currents  $I_x$  are a limit for the achievable accuracy while V is small, hence for low currents. If the voltage drop on  $g_x$  due to  $I_x$  is not negligible, the resulting increase of  $V_{dm}(t)$  expressed by eq. (4.25) reduces the output dynamic range. In the case of a self-biased mirror,  $T_{cl}$  may exit saturation, whereas for an externally biased mirror  $T_{c0}$  may be cut-off. Furthermore, in the case of the bias circuit of Fig. 3.1, the additional voltage drop due to  $I_x$  must be taken into account when fixing  $V_{bias}$ , hence when designing  $T_{mb}$ .

# 4.3 NOISE ANALYSIS

#### 4.3.1 GENERAL CONSIDERATIONS

The noise of an MOS transistor consists of [ALL87], [GRA84]:

- (a) a low frequency noise component, which is reported as "1/f noise" or as flicker noise. Flicker noise has a spectral power density with a 1/f frequency dependence (hence its name), and is mainly due to carrier traps at the Si-SiO<sub>2</sub> interface.

- (b) a white noise component the spectral power density of which is uniform. If the MOS transistor is biased in strong inversion, the main noise component is thermal noise, which is due to the random motion of electrons. On the other hand, shot noise, which is associated with the DC current flowing across the potential barrier, is the principal noise component, if the transistor is biased in weak inversion.

These noise sources are independent and can be represented in the small signal model of the MOS transistor either by a current generator from drain to source, or by a voltage source in series with the gate. An equivalent input noise resistance  $R_N$  can be defined for MOS transistors in saturation [VIT89],

$$R_N = \frac{\gamma}{g_m} + \frac{\rho}{fW_{ef}L_{ef}} \tag{4.26}$$

This noise resistance can be associated with the double sided voltage noise spectral power density  $S_V(f)$  or with the double sided current noise spectral power density  $S_I(f)$ :

$$S_V(f) = 2kT R_N \qquad -\infty > f > +\infty \qquad (4.27)$$

$$S_I(f) = g_m^2 S_V(f) = g_m^2 2kTR_N - \infty > f > + \infty$$

(4.28)

If the MOS transistors operate as switches, hence in the triode region, their equivalent noise resistance  $R_N$  is given by:

$$R_N = \frac{1}{\beta_{sw}(V_G - V_{T0} - nV_s)} = \frac{1}{g_{on}}$$

(4.29)

and  $S_l(f)$  yields

$$S_I(f) = g_{on}^2 S_V(f) = 2kTg_{on} \qquad -\infty > f > +\infty$$

(4.30)

Integrating  $S_V$  or  $S_I$  over the frequency domain leads to total voltage components  $V_N^2$  or current noise components  $I_N^2$ , respectively.

According to eq. (4.26) & (4.28)  $S_I(f)$  can be defined as:

$$S_l(f) = g_m^2 2kT \{ \frac{\gamma}{g_m} + \frac{\rho}{fW_{ef}L_{ef}} \} = 2kT\gamma g_m \{ l + \frac{f_k}{|f|} \}$$

(4.31)

where  $f_k = \frac{g_m \rho}{\gamma W_{ef} L_{ef}}$  is the so-called corner frequency, corresponding to the frequency where white and 1/f noise spectral densities are equal.

A dynamic current mirror is a sampled data circuit and therefore two kinds of noise sources are present:

- (a) direct noise, which occurs when the output current is sinked

- (b) sampled noise, which is due to the storage of the instantaneous value of a noise voltage on C, and which is superposed on the correct value of the gate voltage V.

The output current noise component  $I_N^2$  is the superposition of these two noise currents.

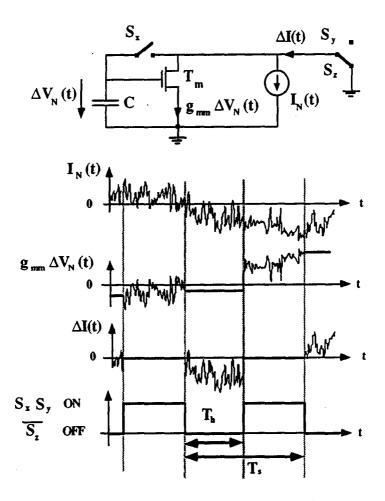

#### 4.3.2 IMPORTANCE OF DIRECT NOISE SOURCES

The different noise sources of a self-biased dynamic mirror are represented in Fig. 4.4. The following considerations remain valid for any kind of cascoded structure.

The total output current noise spectral power density  $S_{lout}(f)$  is the superposition of the noise sources represented in Fig. 4.4.

$$S_{lout}(f) = S_{loc}(f) + S_{lom}(f) + S_{loz}(f)$$

(4.32)

where  $S_{lom}(f)$  and  $S_{loz}(f)$  are the contributions to  $S_{lout}(f)$  of  $T_{mj}$  and  $g_{z1}$ , respectively.

Figure 4.4: Noise sources of a cascoded dynamic current mirror (only the conducting switches are represented)

$S_{loc}(f)$  stands for the noise contribution of  $T_{cl}$  and for all the noise sources of the input branch of the circuit.

These contributions are:

(a)

$$S_{loz}(f) = \left[ \frac{(ng_{mc} + g_{dsc}) g_{dsm}}{g_z (ng_{mc} + g_{dsm} + g_{dsc})} \right]^2 S_{lz}(f) \approx g_{dsm}^2 S_{Vz}(f) \quad (4.33)$$

A high switch conductance  $g_z$  is desirable, hence  $S_{Vz}(f)$  is very small.

(b)  $S_{loc}(f)$ , for a transistor  $T_{cl}$  located in a common well, is found to be:

$$S_{loc}(f) \approx \frac{g_{dsm}^2}{n^2} \left[ S_{Vc1}(f) + \frac{S_{lin}(f)}{g_{mc}^2} \right]$$

(4.34)

In this expression n is replaced by one if  $T_{cl}$  is in a separate well which is connected to the source.

(c)  $S_{lom}(f)$  can be expressed, regardless of whether  $T_{c1}$  is located in a common well or in a separate well, as:

$$S_{lom}(f) = g_{mm}^2 S_{Vm}(f) \tag{4.35}$$

From eq. (4.33) to eq. (4.35) it can be seen that the noise spectral power densities  $S_{lox}(f)$  and  $S_{loc}(f)$  are negligible compared to  $S_{lom}(f)$ , hence only this noise spectral power density has to be taken into account.

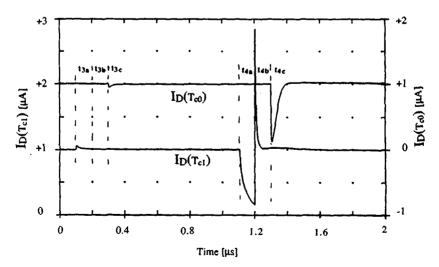

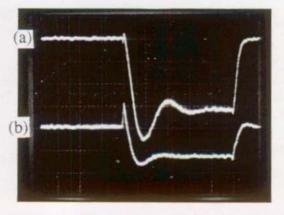

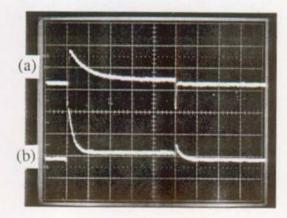

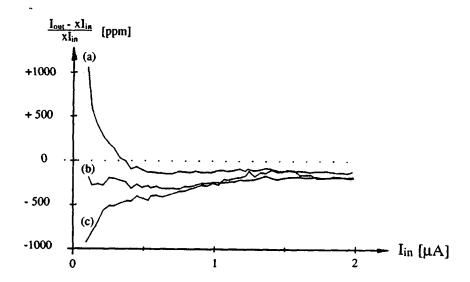

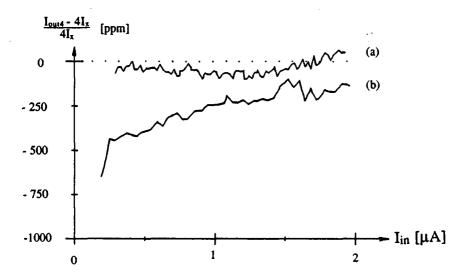

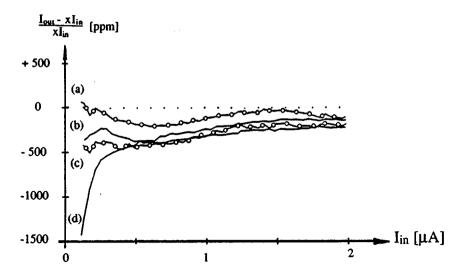

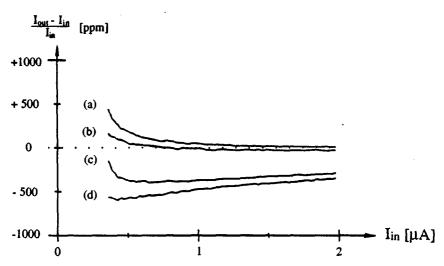

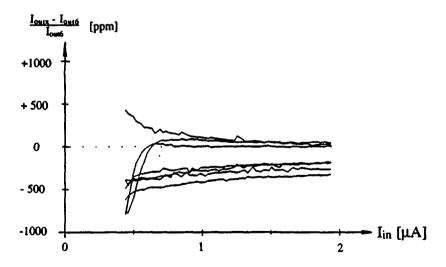

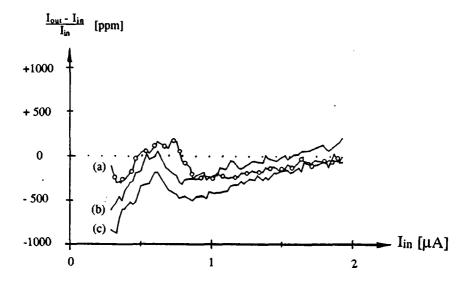

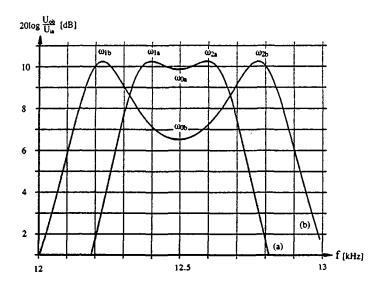

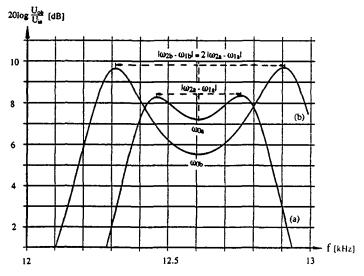

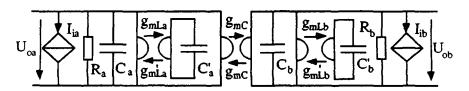

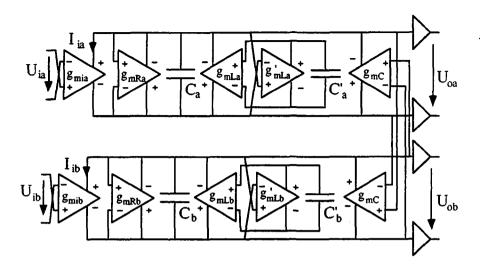

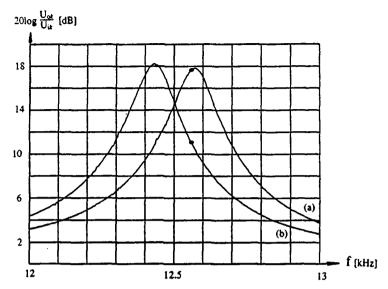

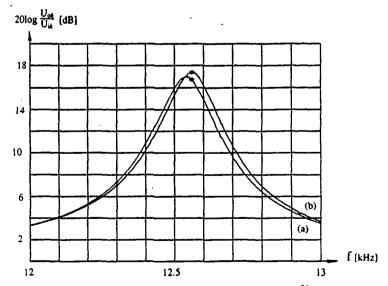

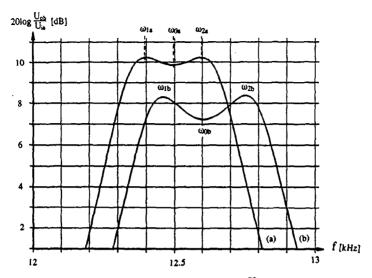

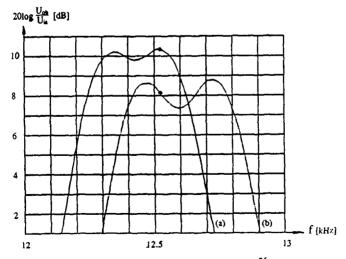

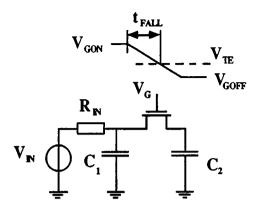

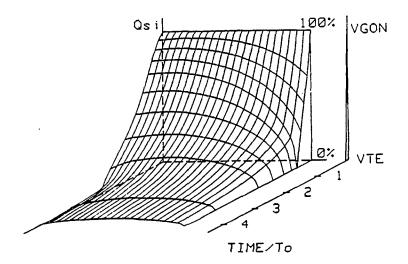

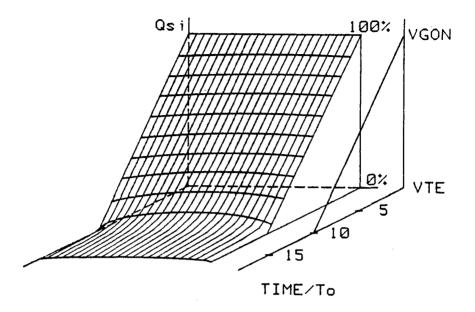

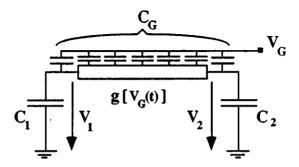

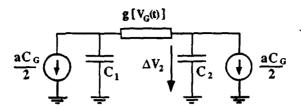

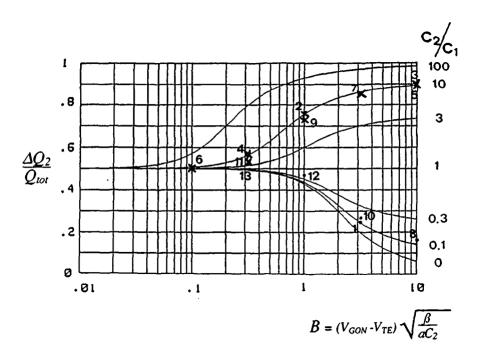

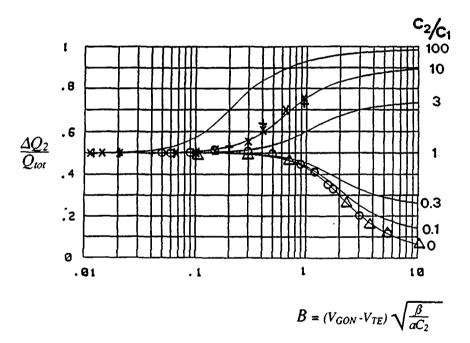

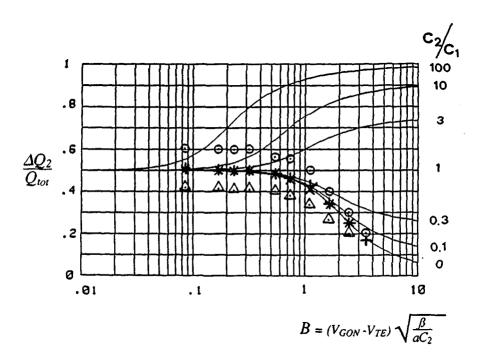

#### 4.3.3 INHERENT AUTOZEROING EFFECT IN THE CURRENT COPIER