# Section 19. Voltage Reference

### **HIGHLIGHTS**

This section of the manual contains the following major topics:

| Introduction                      |                                                                                                                                                                                                                                                                              |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Register                  | 19-3                                                                                                                                                                                                                                                                         |

| Configuring the Voltage Reference |                                                                                                                                                                                                                                                                              |

| Voltage Reference Accuracy/Error  |                                                                                                                                                                                                                                                                              |

| Operation During Sleep            |                                                                                                                                                                                                                                                                              |

| Effects of a Reset                |                                                                                                                                                                                                                                                                              |

| Connection Considerations         |                                                                                                                                                                                                                                                                              |

| Initialization                    |                                                                                                                                                                                                                                                                              |

| Design Tips                       |                                                                                                                                                                                                                                                                              |

| D Related Application Notes       |                                                                                                                                                                                                                                                                              |

| 1 Revision History                | 19-10                                                                                                                                                                                                                                                                        |

|                                   | Introduction<br>Control Register<br>Configuring the Voltage Reference<br>Voltage Reference Accuracy/Error<br>Operation During Sleep<br>Effects of a Reset<br>Connection Considerations<br>Initialization<br>Design Tips<br>D Related Application Notes<br>I Revision History |

#### 19.1 Introduction

The Voltage Reference module is typically used in conjunction with the Comparator module. The comparator module's inputs do not require very large drive, and therefore the drive capability of the Voltage Reference is limited.

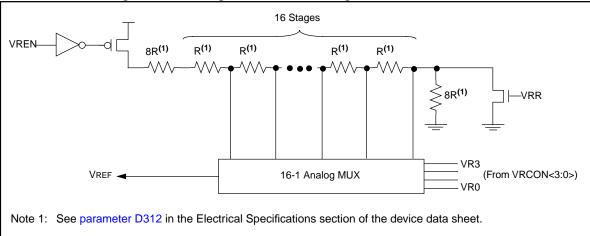

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Figure 19-1. The block diagram is given in Figure 19-1. Within each range, the 16 steps are monotonic (i.e. each increasing code will result in an increasing output).

Figure 19-1: Voltage Reference Block Diagram

| VR3:VR0 | VREF    |         |  |

|---------|---------|---------|--|

| VR3:VRU | VRR = 1 | VRR = 0 |  |

| 0000    | 0.00 V  | 1.25 V  |  |

| 0001    | 0.21 V  | 1.41 V  |  |

| 0010    | 0.42 V  | 1.56 V  |  |

| 0011    | 0.63 V  | 1.72 V  |  |

| 0100    | 0.83 V  | 1.88 V  |  |

| 0101    | 1.04 V  | 2.03 V  |  |

| 0110    | 1.25 V  | 2.19 V  |  |

| 0111    | 1.46 V  | 2.34 V  |  |

| 1000    | 1.67 V  | 2.50 V  |  |

| 1001    | 1.88 V  | 2.66 V  |  |

| 1010    | 2.08 V  | 2.81 V  |  |

| 1011    | 2.29 V  | 2.97 V  |  |

| 1100    | 2.50 V  | 3.13 V  |  |

| 1101    | 2.71 V  | 3.28 V  |  |

| 1110    | 2.92 V  | 3.44 V  |  |

| 1111    | 3.13 V  | 3.59 V  |  |

Table 19-1: Typical Voltage Reference with VDD = 5.0V

#### 19.2 Control Register

Register 19-1: VRCON Register

|         | R/W-0                                                                                                                                                                                                                                                                             | R/W-0       | R/W-0      | U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------|-------|-------|-------|-------|

|         | VREN                                                                                                                                                                                                                                                                              | VROE        | VRR        | _     | VR3   | VR2   | VR1   | VR0   |

|         | bit 7                                                                                                                                                                                                                                                                             |             |            |       |       |       |       | bit 0 |

| bit 7   | VREN: VREF Enable<br>1 = VREF circuit powered on<br>0 = VREF circuit powered down                                                                                                                                                                                                 |             |            |       |       |       |       |       |

| bit 6   | <ul> <li>VROE: VREF Output Enable</li> <li>1 = VREF is internally connected to Comparator module's VREF. This voltage level is also output on the VREF pin</li> <li>0 = VREF is not connected to the comparator module. This voltage is disconnected from the VREF pin</li> </ul> |             |            |       |       |       |       |       |

| bit 5   | VRR: VREF Range selection<br>1 = 0V to 0.75 VDD, with VDD/24 step size<br>0 = 0.25 VDD to 0.75 VDD, with VDD/32 step size                                                                                                                                                         |             |            |       |       |       |       |       |

| bit 4   | Unimplem                                                                                                                                                                                                                                                                          | ented: Read | as '0'     |       |       |       |       |       |

| bit 3:0 | <b>VR3:VR0:</b> VREF value selection $0 \le VR3:VR0 \le 15$                                                                                                                                                                                                                       |             |            |       |       |       |       |       |

|         | When VRR = 1:                                                                                                                                                                                                                                                                     |             |            |       |       |       |       |       |

|         | Vref = (VR<3:0>/ 24) • VDD                                                                                                                                                                                                                                                        |             |            |       |       |       |       |       |

|         | When VRR = 0:                                                                                                                                                                                                                                                                     |             |            |       |       |       |       |       |

|         | VREF = 1/4 * VDD + (VR3:VR0/ 32) • VDD                                                                                                                                                                                                                                            |             |            |       |       |       |       |       |

|         | Legend                                                                                                                                                                                                                                                                            | 11.13       | W - Writch | . 1.2 |       |       |       |       |

| Legend                 |                  |                          |

|------------------------|------------------|--------------------------|

| R = Readable bit       | W = Writable bit |                          |

| U = Unimplemented bit, | read as '0'      | - n = Value at POR reset |

## 19

Voltage Reference

#### 19.3 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1:  $VREF = (VR3: VR0/24) \times VDD$

if VRR = 0:  $VREF = (VDD \times 1/4) + (VR3: VR0/32) \times VDD$

The settling time of the Voltage Reference must be considered when changing the VREF output. Example 19-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

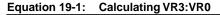

Generally the VREF and VDD of the system will be known and you need to determine the value to load into VR3:VR0. Equation 19-1 shows how to calculate the VR3:VR0 value. There will be some error since VR3:VR0 can only be an integer, and the VREF and VDD levels must be chosen so that the result is not greater then 15.

When VRR = 1  $VR3:VR0 = \frac{VREF}{VDD} \times 24$ When VRR = 0  $VR3:VR0 = \frac{VREF - VDD/4}{VDD} \times 32$

#### 19.4 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 19-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in the Device Data Sheets electrical specification parameter D311.

#### 19.5 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

#### 19.6 Effects of a Reset

A device reset disables the Voltage Reference by clearing the VREN bit (VRCON<7>). This reset also disconnects the reference from the VREF pin by clearing the VROE bit (VRCON<6>) and selects the high voltage range by clearing the VRR bit (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

Reference

#### 19.7 **Connection Considerations**

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the VREF pin if the corresponding TRIS bit is set and the VROE bit (VRCON<6>) is set. Enabling the Voltage Reference output onto the VREF pin with an input signal present will increase current consumption. Configuring the VREF as a digital output with VREF enabled will also increase current consumption.

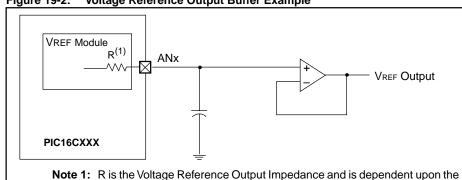

The VREF pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 19-2 shows an example buffering technique.

Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

Figure 19-2: Voltage Reference Output Buffer Example

#### 19.8 Initialization

Example 19-1 shows the steps to configure the voltage reference module.

Example 19-1: Voltage Reference Configuration

| MOVLW 0x02     | ; 4 Inputs Muxed to 2 comparators |

|----------------|-----------------------------------|

| MOVWF CMCON    | ,                                 |

| BSF STATUS, RP | 0 ; go to Bankl                   |

| MOVLW 0x07     | ; RA3:RA0 are outputs             |

| MOVWF TRISA    | ; outputs                         |

| MOVLW 0xA6     | ; enable VREF                     |

| MOVWF VRCON    | ; low range set VR3:VR0 = 6       |

| BCF STATUS, RP | 0 ; go to BankO                   |

| CALL DELAY10   | ; 10 µs delay                     |

|                |                                   |

## 19

#### 19.9 Design Tips

#### Question 1: My VREF is not what I expect.

#### Answer 1:

Any variation of the device VDD will translate directly onto the VREF pin. Also ensure that you have correctly calculated (specified) the VDD divider which generates the VREF.

# Question 2: I am connecting VREF into a low impedance circuit, and the VREF is not at the expected level.

#### Answer 2:

The Voltage Reference module is not intended to drive large loads. A buffer must be used between the PICmicro's VREF pin and the load.

#### 19.10 Related Application Notes

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the Mid-Range MCU family (that is they may be written for the Base-Line, or High-End families), but the concepts are pertinent, and could be used (with modification and possible limitations). The current application notes related to Voltage Reference are:

#### Title

Application Note #

AN611

Resistance and Capacitance Meter using a PIC16C622

19

Voltage Reference

#### 19.11 Revision History

**Revision A**

This is the initial released revision of the Voltage Reference description.