# Accelerating WiMAX System Design with FPGAs

# Abstract

WiMAX, or the IEEE 802.16 standard for broadband wireless access, is increasingly gaining in popularity as a technology with significant market potential. This paper first provides an overview of the existing and developing 802.16 standards and their key differences/applications. The PHY and MAC layers of a typical WiMAX base station are then described. The associated implementation challenges faced by WiMAX infrastructure developers, including performance/cost/flexibility trade-offs in the choice of silicon, are clearly outlined. The paper then describes how FPGA-based system implementation can address these challenges including the "accelerated time-to-market" requirement which is considered a key enabler for early success in this market. As an example design, the physical layer implementation of the 802.16d standard with Altera FPGAs and intellectual property (IP) is proposed.

■ Keywords: WiMAX, FPGA, OFDM, 802.16d, 802.16e, Altera

## Introduction

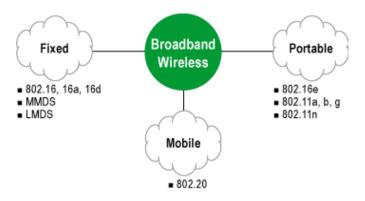

The explosive growth of the Internet over the last decade has lead to an increasing demand for high-speed, ubiquitous Internet access. Broadband wireless access (BWA) is increasingly gaining popularity as an alternative "last-mile" technology to DSL lines and cable modems. Following the hugely successful global deployment of the 802.11 wireless local area network (LAN) standard, deployment of the IEEE 802.16d wireless metropolitan area network (MAN) standard is currently in progress. This technology aims to provide fixed broadband wireless access to residential and small business applications, as well as enable Internet access in countries without any existing wired infrastructure in place. Standardization efforts are also underway for the 802.16e version that attempts to provide mobility to the end user in a MAN environment. The WiMAX Forum (Worldwide Interoperability for Microwave Access) is an industry-led, non-profit corporation formed to promote and certify compatibility and interoperability of broadband wireless products. The organization is a non-profit association formed in 2003 by equipment and component suppliers to promote the adoption of IEEE 802.16 compliant equipment by operators of broadband wireless access systems [1].

## Figure 1: Overview of broadband wireless standards

October 2004, ver. 1.0

WP-FPGA102204-1.0

|                        | 802.16                                | 802.16a/Rev d                                                                                    | 802.16e                                                |  |  |

|------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|

| Completed              | December 2001                         | 802.16a: Jan 2003<br>802.16Revd: June 2004                                                       | Est. Mid-2005                                          |  |  |

| Spectrum               | 10 - 66 GHz                           | 2 - 11 GHz                                                                                       | 2 – 6 GHz                                              |  |  |

| Application            | Backhaul                              | Wireless DSL & Backhaul                                                                          | Mobile Internet                                        |  |  |

| Channel<br>Conditions  | Line of Sight Only                    | Non Line of Sight                                                                                | Non Line of Sight                                      |  |  |

| Bit Rate               | 32 – 134 Mbps at 28MHz channelization | Up to 75 Mbps at 20MHz channelization                                                            | Up to 15 Mbps at 5MHz channelization                   |  |  |

| Modulation             | QPSK, 16QAM and<br>64QAM              | OFDM 256 sub-carriers<br>QPSK, 16QAM, 64QAM                                                      | Scalable OFDMA                                         |  |  |

| Mobility               | Fixed                                 | Fixed                                                                                            | Pedestrian Mobility –<br>Regional Roaming              |  |  |

| Channel<br>Bandwidths  | 20, 25 and 28 MHz                     | Selectable channel<br>bandwidths between 1.5 and<br>20 MHz                                       | Same as 802.16a with UL sub-channels to conserve power |  |  |

| Typical Cell<br>Radius | 1-3 miles                             | 4 to 6 miles; Max range 30<br>miles based on tower height,<br>antenna gain and power<br>transmit | 1-3 miles                                              |  |  |

## IEEE 802.16Rev d Standard

This revised standard consolidates IEEE Standards 802.16, 802.16a, and 802.16c, retaining all modes and major features without adding new modes. This standard specifies the air interface of a fixed (stationary) point-to-multipoint (PMP) BWA system providing multiple services in a wireless metropolitan area network (MAN) [2]. It also specifies an optional mesh topology enhancement to the medium access control layer (MAC). The WirelessMAN MAC is capable of supporting multiple physical layer (PHY) specifications optimized for the frequency bands of application. The standard includes PHY specifications, applicable to systems operating below 11 GHz and between 10 GHz and 66 GHz. The 10–66 GHz air interface, based on single-carrier modulation, is known as the WirelessMAN-SC air interface. For frequencies below 11 GHz, the WirelessMAN-SCa, Wireless- MAN-OFDM and WirelessMAN-OFDMA air interfaces are specified.

## MAC Layer Overview

The main focus of the MAC layer is to manage the resources of the airlink in an efficient manner.

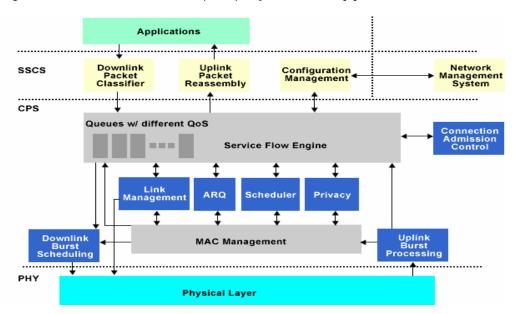

As illustrated in Figure 2, the MAC layer consists of three sub-layers.

- Service specific convergence sub-layer (SSCS) provides an interface to the upper layer entities through a CS service access point (SAP).

- The MAC common part sub-layer (CPS) provides the core MAC functions, including uplink scheduling, bandwidth request and grant, connection control, and automatic repeat request (ARQ).

- Privacy sub-layer (PS) provides authentication and data encryption functions.

2

Figure 2: Medium Access Control (MAC) Layer Functions [3]

The tasks performed by the 802.16 MAC protocol can also be partitioned in a different way into two categories [4]: periodic (per-frame) "fast path" activities, and aperiodic "slow path" activities. Fast path activities (such as scheduling, packing, fragmentation, and ARQ) must be performed at the granularity of single frames, and they are subject to hard real-time deadlines. They must complete in time for transmission of the frame they are associated with. In contrast, slow path activities typically execute according to timers that are not associated with a specific frame or the frame period and as such do not have stringent deadlines.

## PHY Layer Overview

Because of its superior performance in multipath fading wireless channels, orthogonal frequency division multiplexing (OFDM) signaling is recommended in OFDM and WirelessMAN OFDMA PHY layer modes of the 802.16 standard for operation in sub 11 GHz non-line of sight (NLOS) applications. OFDM technology has also been recommended in other wireless standards such as digital video broadcasting (DVB) and wireless local area networking (WLAN).

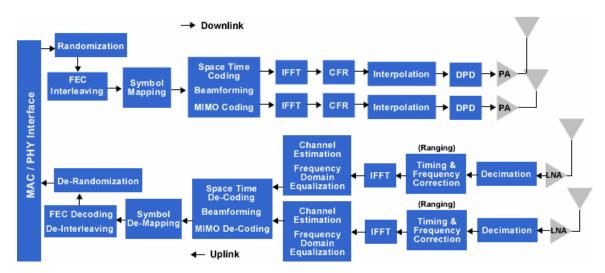

Figure 3 provides an overview of the typical PHY layer functions implemented in a WiMAX base station operating in the OFDM/OFDMA modes.

Apart from the usual functions such as randomization, forward error correction (FEC), interleaving, and mapping to QPSK and QAM symbols, the standard also specifies optional multiple antenna techniques. This includes space time coding (STC), beamforming using adaptive antennas schemes, and multiple input multiple output (MIMO) techniques which achieve higher data rates. The OFDM modulation/demodulation is usually implemented by performing fast fourier transform (FFT) and inverse FFT on the data signal. Although not specified in the standards, other advanced signal processing techniques such as crest factor reduction (CFR) and digital predistortion (DPD) are also usually implemented in the forward path, to improve the efficiency of the power amplifiers used in the base stations.

Figure 3: Overview of PHY Layer functions in a typical WiMAX base station

The uplink receive processing functions include time, frequency and power synchronization (ranging), and frequency domain equalization, along with rest of the decoding/demodulation operations necessary to recover the transmitted signal. Implementation of the PHY layer functions is described in WiMAX PHY Layer IP and Reference Designs section of this document.

## Hardware Platform for WiMAX Implementation

Designers of WiMAX systems need to meet a number of critical requirements such as processing speed, flexibility and time-to-market, and it is these stringent requirements that ultimately drive the choice of the hardware platform. Some of the major challenges are further described below.

## Implementation Challenges

- Processing speed: Broadband wireless systems such as WiMAX have throughput and data rate requirements that are significantly higher than those in cellular systems such as WCDMA and cdma2000. In order to be able to support such high data rates, the underlying hardware platform must have significant processing capabilities. In addition, several advanced signal processing techniques such as Turbo coding/decoding, and front end functions such as FFT/IFFT, beam forming, MIMO, CFR and DPD are very computationally intensive and require several billion multiply and accumulate (MAC) operations per second.

- Flexibility: WiMAX is a relatively new market and is currently going through the initial development and deployment process. 802.16Rev d has just been standardized while the 802.16e mobile version is still in the works. Under this current scenario, having hardware flexibility/re-programmability in the end WiMAX compliant product is very important. This ensures that in-field programmability is possible, alleviating the risks posed by constantly evolving standards.

- Time to Market: Because WiMAX is an emerging technology, time-to-market is a key differentiator for OEMs looking for early success in gaining market share. This has a direct effect on the development cycle and choice of hardware platform, with designers requiring easy-to-use development tools, software, boards, and off-the-shelf IP and reference designs in order to accelerate the system design.

#### **Altera Corporation**

Cost Reduction Path: Another important requirement to keep in mind while choosing the hardware platform is the availability of a long term cost reduction path. The evolving WiMAX standard/market is expected to stabilize after the initial uncertainty surrounding it, leading to a situation where cost of the final product becomes much more important than retaining flexibility. A hardware platform that has such a clear cost reduction path and enables a seamless flexibility/cost tradeoff is the need of the hour.

## FPGAs-The Right Solution

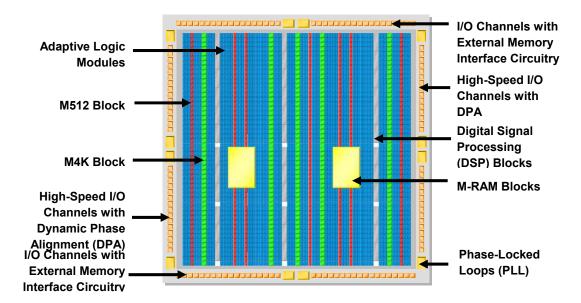

Field programmable gate arrays (FPGAs) provide an ideal implementation platform for developing broadband wireless systems such as WiMAX. State-of-the-art high-end, high performance FPGAs such as Altera's Stratix II FPGA, are usually used at the heart of high-bandwidth systems to accelerate performance and enable new functionality. Figure 3 provides an overview of the architectural layout of the industry leading Stratix II FPGA [5].

Stratix II devices improve on the features that set new standards in FPGAs. New device capabilities such as the new logic structure and design security technology round out the industry's most advanced FPGA feature set.

New Logic Structure

- New and innovative logic structure based on adaptive logic modules (ALMs) that packs more logic into less area and enables faster performance

- Dedicated arithmetic functionality to efficiently implement adder trees and other computationally intensive functions

#### TriMatrix™ Memory

- Up to 9 Mbits of memory in three block sizes: M-RAM, M4K, and M512 blocks

- Includes parity bits for error checking

- Performance up to 370 MHz

- Mixed-width data and mixed-clock modes

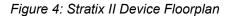

#### Digital Signal Processing (DSP) Blocks

- Dedicated multiplier, pipeline, and accumulate circuitry

- New rounding and saturation support in Q1.15 format in each DSP block

- Maximized performance of up to 370 MHz providing DSP throughput up to 284 GMACs

#### Remote System Upgrades

- Remote system upgrades for reliable and safe deployment of in-system upgrades and bug fixes

- Dedicated watchdog circuitry ensures proper functionality after update

## FPGA based WiMAX System Design

This section describes how each of the implementation challenges associated with WiMAX system design, as outlined in Implementation Challenges section, can be effectively addressed with FPGAs. Altera's Stratix II and Cyclone II FPGAs are considered as a case study.

## Processing Speed

As outlined in the previous section, high performance FPGAs such as Altera's Stratix II platform [5], contain embedded DSP blocks, TriMatrix<sup>TM</sup> memory architecture, innovative logic structure, and high-speed interfaces, providing a powerful and integrated platform to implement broadband wireless systems such as WiMAX.

Figure 5: Stratix II DSP Block Architecture

Optional Rounding & Saturation

Each DSP block can support a variety of multiplier bit sizes (9x9, 18x18, 36x36) and operation modes (multiplication, complex multiplication, multiply-accumulation and multiply-addition) and can offer a DSP throughput of 2.8 GMACS per DSP block. Such high throughputs are required for implementing complex DSP techniques found in WiMAX systems including adaptive beamforming, MIMO, FFT/IFFT, FIR filtering, CFR etc. The largest Stratix II device, the EP2S180 device, has 96 DSP blocks that offer a throughput of 284 GMACS and can support up to 384 18x18 multipliers. The throughput in Stratix II devices is orders of magnitude higher than single-chip DSP processors available in the marketplace today. In addition, new rounding and saturation support has been added to the DSP block to facilitate porting DSP firmware code onto the FPGA.

## Flexibility

As noted earlier, hardware flexibility/re-programmability in the end WiMAX compliant product is very important due to constantly evolving standards. Altera's Stratix II FPGAs provide the ability to easily evolve WiMAX systems in accordance with changing market demands. These devices allow remote system upgrades to be transmitted over any communications network, keeping products ahead of the competition, and also feature the dedicated recovery circuitry to ensure reliable updates.

Remote system upgrades are enabled using Stratix II devices and flash memory. As shown in Figure 6, a user can perform a remote system upgrade in three simple steps:

- 1. Send an update from the development location through a network to the Stratix II device.

- 2. Store the update in the memory.

- 3. Update the Stratix II device with the new data.

A Stratix II device-developed WiMAX system can be easily upgraded when:

- Additional protocol support is required to ensure compatibility with future products

- Enhancements or bug fixes are necessary

WiMAX systems that use Stratix II FPGAs can stave off premature obsolescence because they can support evolving standards and applications that were not known at the time of equipment deployment.

## Time-to-Market

As with any new promising technology, time-to-market is a key differentiator for OEMs developing WiMAX compliant products. To achieve this, designers need access to off-the-shelf IPs and reference designs that help accelerate their own development cycle. Easy-to-use development tools, software and availability of development boards are other key requirements.

## WiMAX PHY Layer IP and Reference Designs

This section describes some of the PHY layer solutions available from Altera. Development tools and software are discussed in Development Tools and Software section of this document.

**Forward Error Correction (FEC):** 802.16Rev d specifies the concatenation of a Reed-Solomon (RS) outer code and a rate-compatible convolutional inner code, on both uplink and downlink. The encoding is performed by first passing the data in block format through the RS encoder and then passing it through a zero-terminating convolutional encoder.

To implement these schemes, Altera provides the RS Compiler and Viterbi Compiler IPs that are fully parameterizable and have a user friendly interface [6]. For example, parameters such as number of bits per symbol, number of symbols per codeword, number of check symbols per codeword, field polynomial, first root of generator polynomial, and space between roots in generator polynomial can be specified using the RS Compiler. This makes the task of the designer very easy, as all that is required is providing the parameters as specified in 802.16Rev d. From this point, the source code for the FPGA is automatically created at the push of a button. Moreover, based on the throughput requirements, the user can specify different implementation techniques including discrete, continuous and streaming decoder architectures that essentially provide

flexibility to make throughput-resource consumption trade-offs. The automatically generated code is highly optimized for Altera FPGAs, including Stratix II and Cyclone II devices.

Turbo convolutional codes and Turbo Block codes are specified as optional FEC schemes in the standard. Low density parity check (LDPC) codes are a new type of FEC codes that are gaining in popularity and might be specified as optional FEC scheme in 802.16e version. Altera, along with its IP partners, provides a complete portfolio of FEC schemes for WiMAX systems.

**OFDM modulation/demodulation:** As shown in Figure 3, the OFDM or OFDMA sub-carriers are generated by performing the IFFT operation at the transmitter, while FFT operation is done at the receiver to transform the signal back to the frequency domain. As specified in the 802.16Rev d standard, a 256 point FFT/IFFT is required for the OFDM mode while the OFDMA mode of operation requires 2048 point FFT/IFFT. The FFT is a computationally intensive function requiring a large number of multipliers and Stratix II FPGAs, with embedded DSP blocks, offer an ideal scalable platform to implement FFT of various sizes. Altera also provides the FFT IP function that is a high performance, highly-parameterizable FFT processor [7]. The FFT function implements a Radix-2/4 decimation-in-frequency (DIF) FFT algorithm for transform lengths of 2<sup>m</sup> where 6 • m • 14, internally using a block-floating-point architecture to maximize signal dynamic range in the transform calculation. An accumulated block exponent is output to indicate any data scaling that has occurred during the transform to maintain precision and maximize the internal signal-tonoise ratio. Transform direction is specifiable on a per-block basis via an input port. Table 2 offers an overview of the resource consumption and throughputs achieved for various FFT sizes on the Stratix II platform.

| Device       | Points | Width<br><u>(1)</u> | Logic<br>Elements<br>(LEs) <u>(2)</u> | 18*18<br>Mults | M4K<br>blocks<br>used <u>(3)</u> | M-RAM<br>blocks<br>used | f <sub>MAX</sub><br>(MHz) | Clock<br>Cycle<br>Count | Transform<br>Time (μs) |

|--------------|--------|---------------------|---------------------------------------|----------------|----------------------------------|-------------------------|---------------------------|-------------------------|------------------------|

| EP2S15F484C3 | 256    | 16                  | 4,360                                 | 9              | 19                               | 0                       | 335.23                    | 256                     | 0.76                   |

| EP2S15F484C3 | 512    | 16                  | 4,826                                 | 9              | 19                               | 0                       | 319.19                    | 512                     | 1.6                    |

| EP2S15F484C3 | 1,024  | 16                  | 5,137                                 | 9              | 38                               | 0                       | 325.73                    | 1,024                   | 3.14                   |

| EP2S15F484C3 | 2,048  | 16                  | 6,946                                 | 18             | 75/44                            | 0/2                     | 309.89                    | 2,048                   | 6.61                   |

| EP2S30F484C3 | 4,096  | 16                  | 7,429                                 | 18             | 144/88                           | 0/2                     | 301.84                    | 4,096                   | 13.57                  |

| EP2S60F484C3 | 8,192  | 16                  | 7,351                                 | 18             | 304/176                          | 0/2                     | 293.06                    | 8,192                   | 27.95                  |

Notes:

1. Represents data and twiddle factor precision.

2. The LE count for Stratix II devices is based on the number of adaptive look-up tables (ALUTs) used for the design as reported by the Quartus II software.

3. For cases in which M-RAM utilization is permitted, the first number indicates the number of M4K blocks used when M-RAM usage is disabled.

**Multiple Antenna Techniques:** Multiple antennas techniques are specified in WiMAX systems to increase the range and reliability of transmission and reception. Multiple antenna schemes provide various benefits including array gain, diversity gain and co-channel interference suppression. 802.16Rev d currently supports several multiple antenna options including space-time codes (STC), multiple-input multiple-output (MIMO) antenna systems and adaptive antenna systems (AAS). These schemes involve computationally intensive algorithms and operations that are well suited for implementation on FPGAs.

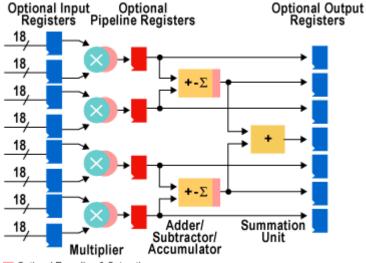

Figure 7 illustrates an example implementation of AAS to perform receive beamforming. The signals from different antennas are first downconverted to baseband using digital down converters (DDC) and then transformed back to the frequency domain using FFT operations. Complex weights are then applied to the signals before performing maximum ratio combining (MRC) to maximize the signal-to-noise ratio. The application of complex weights to the signals from different antennas involves complex multiplications that map well onto the embedded DSP blocks

Figure 7: Beam forming Implementation with AAS schemes

available in Stratix II devices. The weights are computed using the QR decomposition based recursive least squares (QRD-RLS) algorithm. Altera provides IP cores to implement adaptive weight update algorithms such as the least mean squares (LMS), normalized LMS (NLMS), RLS and QRD-RLS algorithms.

Altera also provides the Alamouti decoder core to implement the transmit diversity option using Alamouti space time codes as specified in the WiMAX standard. MIMO spatial multiplexing schemes usually require matrix decomposition algorithms such as the QR decomposition, Cholesky decomposition and Singular value decomposition (SVD). These cores are also provided by Altera to ease the implementation of MIMO techniques on FPGAs.

**Crest Factor Reduction (CFR):** CFR or peak-to-average-power-ratio (PAPR) reduction is an essential function for OFDM based systems such as WiMAX. Multi-carrier modulation techniques such as OFDM generate signals with high crest factors (peak-to-average ratios) that degrade the efficiency of the power amplifiers used in basestation transmitters. The operating point of the power amplifier (PA) is typically reduced, or backed off, to accommodate the peaks of the input signal. This is done to maintain linearity at the PA output and prevent out-of-band radiation. Input signals with a high crest factor will need large back-off and will lower the efficiency of the PA. It is, therefore, important to reduce the crest factor of the input signal and prevent the efficiency of the PA from falling to unacceptable levels.

As specified in the standard, randomization is a technique that reduces the probability of generating signals with high crest factors by scrambling the correlated bit patterns in the data to be transmitted. Another technique to reduce PAPR is by clipping the signal, followed by frequency domain filtering [8]. The output of the IFFT at the transmitter is interpolated by inserting zeros, followed by a non-linear clipping operation. Since clipping can increase out-of-band radiation, this is followed by frequency domain filtering that basically involves an additional FFT and IFFT operation. As described earlier, the FFT IP core from Altera can be used to perform the frequency domain filtering operation very efficiently.

#### Accelerating WiMAX System Design with FPGAs

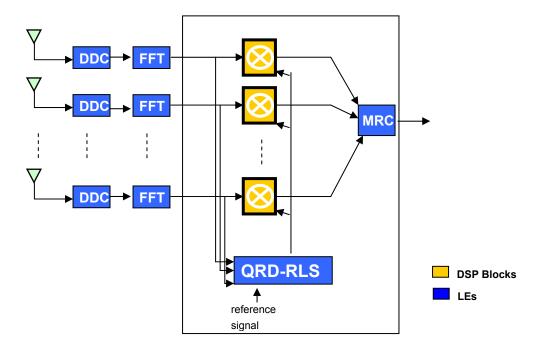

**Digital Up/Down Conversion:** Digital frequency conversion provides greater flexibility and higher performance (in terms of attenuation and selectivity) than traditional analog techniques. It also reduces component and manufacturing costs by eliminating the need for analog mixers and oscillators. In digital upconversion, the input data is interpolated in multiple stages before it is quadrature modulated with a tunable carrier frequency generated by a numerically controlled oscillator (NCO, as illustrated in Figure 8.

To implement the interpolating baseband finite impulse response (FIR) filter, Altera offers the fully parameterizable FIR Compiler IP using which optimal FIR filter architectures can be built via speed-area tradeoffs [9]. For example, fully serial architecture with distributed arithmetic can be used for high bandwidth systems, whereas a fully parallel architecture can be implemented for systems with low bandwidth. It also includes a built-in coefficient generator that automatically calculates the FIR coefficients based on the required filter characteristics.

#### Figure 8: Digital Up conversion Implementation

Altera also offers the NCO Compiler IP core that can generate a wide range of architectures for oscillators with spurious-free dynamic range in excess of 115 dB and very high performance [10]. To implement a multi carrier upconverter, based on each carrier frequency, the optimal FPGA resource can be selected to implement the NCOs, i.e., the NCOs can be implemented using either dedicated multipliers or memory or with the CORDIC IP that Altera offers. Digital downconverters (DDC) can also be similarly designed using the FIR Compiler and NCO Compiler IPs.

In addition to the PHY layer functions described above, Altera also provides IP cores and reference designs for other functions including digital predistortion (DPD), ranging, channel estimation etc. These reference designs can be used to develop new solutions and innovative WiMAX products, as well as help to reduce time-to-market and differentiate products from competing solutions.

#### Development Tools and Software

As noted earlier, another important requirement for accelerating WiMAX hardware design is the availability of easy-to-use development tools and software. This section describes how some of the design issues involved in WiMAX system design are addressed by FPGA tools from Altera.

**Rapid Prototyping:** The different DSP algorithms involved in WiMAX system design are usually implemented by designers in a high level model such as MathWork's MATLAB and Simulink environment. After verification of the functionality, the algorithms are then again coded using hardware description languages (HDLs) for implementation in hardware, resulting in long design cycles. The Altera DSP Builder tool integrates these phases by combining the algorithm development, simulation, and verification capabilities of The MathWorks MATLAB and Simulink system-level design tools with VHDL synthesis,

#### **Altera Corporation**

simulation, and Altera development tools [11]. The DSP Builder shortens DSP design cycles by helping designers create the hardware representation of a DSP design in an algorithm-friendly development environment. The existing MATLAB functions and Simulink blocks can be combined with Altera DSP Builder blocks and intellectual property (IP) to link system-level design and implementation with DSP algorithm development.

DSP Builder allows system, algorithm, and hardware designers to share a common development platform. Designers can use the blocks in DSP Builder to create a hardware implementation of a system modeled in Simulink in sampled time. DSP Builder contains bit- and cycle-accurate Simulink blocks, which cover basic operations such as arithmetic or storage functions. Complex functions can be integrated by using Altera IP functions in DSP Builder models.

**System –on-a-programmable chip (SOPC) design:** Some of the PHY and MAC layer functions involved in WiMAX systems are better suited for implementation in software. These control-oriented functions include aspects of the MAC layer such as the scheduler and channel estimation in the PHY layer. Such functions can be efficiently integrated into the FPGAs by implementing them on soft processors within the FPGA, eliminating the need for a separate digital signal processor. The Nios<sup>®</sup> II family of embedded processors from Altera features a general-purpose RISC CPU architecture designed to address a wide range of embedded applications [12]. The Nios II processor family consists of three cores–fast (Nios II/f), economy (Nios II/e), and standard (NiosII/s) cores–each optimized for a specific price and performance range.

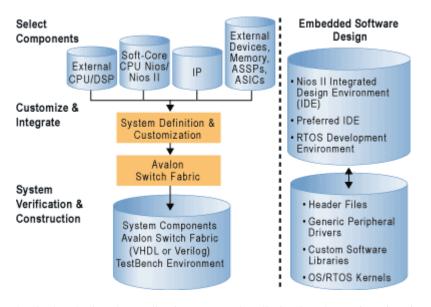

Designers can easily add Nios II processors to their systems by using the SOPC Builder tool featured in Altera's industry-leading Quartus<sup>®</sup> II design software. The SOPC Builder tool, included with the Quartus II design software from Altera, automatically generates the interconnect logic (Avalon<sup>TM</sup> switch fabric) connecting components used in SOPC applications [13].

As illustrated in Figure 9, the components include embedded processors that are internal or external to the FPGA and peripherals, including intellectual property (IP) cores and customer-created peripheral cores, and off-chip devices such as ASSPs and ASICs. With the export of header files and peripheral drivers, SOPC Builder accelerates the development of application software. SOPC Builder enables designers to focus on the key components of their systems and

Figure 9: SOPC Builder design flow

begin developing the applications sooner by eliminating the engineering time required for system integration tasks.

## Cost Reduction Path

Although flexibility is highly desired in initial WiMAX products (due to the evolving standards and market uncertainty), the standards will eventually stabilize, leading to a situation where flexibility of the WiMAX product needs to be traded for a low-cost ASIC implementation. Altera provides this cost reduction path for its FPGAs through HardCopy devices. Altera<sup>®</sup> HardCopy<sup>™</sup> devices are the industry's first structured ASICs that offer a comprehensive alternative to traditional ASICs [14]. ASIC design today faces increasing product development costs and long design cycles, both due to shrinking process geometries and growing design complexity. These challenges also demand first silicon success to avoid costly and time-consuming re-spins.

Altera addresses the pain associated with traditional ASIC design by providing the FPGAs, development tools, intellectual property (IP), and a seamless migration path from the function-verified prototypes to high-volume production devices. With HardCopy devices, users can obtain an average of 50% performance improvement and ~40% power reduction compared to FPGA and guaranteed first-time success in silicon. Supported by Altera's Quartus<sup>®</sup> II software (version 3.0 and later), engineers can now design an FPGA or a HardCopy device from their desktops using a similar design flow, architecture, tools, and IP.

## Conclusions

WiMAX is an emerging technology with significant potential and is poised to revolutionize the "broadband wireless internet access" market. The diverse hardware requirements including processing speed, flexibility, integration and time-to-market necessitate an FPGA based implementation platform. Altera's high-density FPGAs and HardCopy devices provide WiMAX OEMs with significant competitive advantages by minimizing development time and resources, maximizing first-time success, and accelerating time-to-market.

## References

[1] The WiMAX Forum. www.wimaxforum.org

[2] IEEE 802.16Rev d. Air Interface for Fixed Broadband Wireless Access Systems

[3] Hassan Yaghoobi. 802.16 Broadband wireless access: the next big thing in wireless. Intel Developer Forum, Sep 2003

[4] Govindan Nair, Joey Chou, Tomasz Madejski, Krzysztof Perycz, David Putzolu, Jerry Sydir. IEEE 802.16 Medium Access Control and Service Provisioning. Intel Technology Journal, Aug 2004

[5] Stratix II Device Family Features. http://www.altera.com/products/devices/stratix2/features/st2-features.html

[6] Error Detection & Correction. http://www.altera.com/products/ip/dsp/error\_detection\_correction/ipm-index.jsp

[7] FFT MegaCore Function. http://www.altera.com/products/ip/dsp/transforms/m-ham-fft.html

[8] Jean Armstrong. New OFDM peak-to-average power reduction scheme. Vehicular Technology Conference, 2001

[9] FIR Compiler MegaCore Function. http://www.altera.com/products/ip/dsp/filtering/m-alt-fircompiler.html

[10] NCO Compiler. http://www.altera.com/products/ip/dsp/signal\_generation/m-alt-ncocompiler.html

[11] DSP Builder. http://www.altera.com/products/software/products/dsp/dsp-builder.html

[12] Nios II family of embedded processors. http://www.altera.com/products/ip/processors/nios2/ni2-index.html

[13] SOPC Builder. http://www.altera.com/products/software/products/sopc/sop-index.html [14] HardCopy Devices. <u>http://www.altera.com/products/devices/hardcopy/hrd-index.html</u>

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries.\* All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.