## **CHAPTER 8**

# **3V Tips 'n Tricks**

## **Table Of Contents**

| TIPS 'N 1 | TRICKS INTRODUCTION                        |     | TIP #8:  | 3.3V → 5V Using A Voltage           |     |

|-----------|--------------------------------------------|-----|----------|-------------------------------------|-----|

|           | Powering 3.3V Systems From 5V              |     |          | Comparator                          | 8-8 |

|           | Using an LDO Regulator                     | 8-3 | TIP #9:  | 5V → 3.3V Direct Connect            | 8-9 |

| TIP #2:   | Low-Cost Alternative Power System          |     | TIP #10: | 5V → 3.3V With Diode Clamp          | 8-9 |

|           | Using a Zener Diode                        | 8-4 | TIP #11: | 5V → 3.3V Active Clamp8             | -10 |

| TIP #3:   | Lower Cost Alternative Power System        |     | TIP #12: | 5V → 3.3V Resistor Divider8         | -10 |

|           | Using 3 Rectifier Diodes                   | 8-4 | TIP #13: | 3.3V → 5V Level Translators8        | -12 |

| TIP #4:   | Powering 3.3V Systems From 5V              |     | TIP #14: | 3.3V → 5V Analog Gain Block8        | -13 |

|           | Using Switching Regulators                 |     | TIP #15: | 3.3V → 5V Analog Offset Block8      | -13 |

| TIP #5:   | 3.3V → 5V Direct Connect                   | 8-6 | TIP #16: | 5V → 3.3V Active Analog Attenuator8 | -14 |

| TIP #6:   | 3.3V → 5V Using a MOSFET                   |     | TIP #17: | 5V → 3V Analog Limiter8             | -15 |

|           | Translator                                 |     | TIP #18: | Driving Bipolar Transistors8        | -16 |

| TIP #7:   | $3.3V \rightarrow 5V$ Using A Diode Offset | 8-7 |          | Driving N-Channel MOSFET            |     |

|           |                                            |     |          | Transistors 8                       | -18 |

#### TIPS 'N TRICKS INTRODUCTION

#### Overview - the 3.3 Volt to 5 Volt Connection

One of the by-products of our ever increasing need for processing speed is the steady reduction in the size of the transistors used to build microcontrollers. Up-integration at cheaper cost also drives the need for smaller geometries. With reduced size comes a reduction in the transistor breakdown voltage, and ultimately, a reduction in the supply voltage when the breakdown voltage falls below the supply voltage. So, as speeds increase and complexity mounts, it is an inevitable consequence that the supply voltages would drop from 5V to 3.3V, or even 1.8V for high density devices.

Microchip microcontrollers have reached a sufficient level of speed and complexity that they too are making the transition to sub-5V supply voltages. The challenge is that most of the interface circuitry is still designed for 5V supplies. This means that, as designers, we now face the task of interfacing 3.3V and 5V systems. Further, the task includes not only logic level translation, but also powering the 3.3V systems and translating analog signals across the 3.3V/5V barrier.

This Tips 'n Tricks book addresses these challenges with a collection of power supply building blocks, digital level translation blocks and even analog translation blocks. Throughout the book, multiple options are presented for each of the transitions, spanning the range from all-in-one interface devices, to low-cost discrete solutions. In short, all the blocks a designer is likely to need for handling the 3.3V challenge, whether the driving force is complexity, cost or size.

Additional information can be found on the Microchip web site at www.microchip.com/3volts.

**Note:** The tips 'n tricks presented here assume a 3.3V supply. However, the techniques work equally well for other supply voltages with the appropriate modifications.

#### **Power Supplies**

One of the first 3.3V challenges is generating the 3.3V supply voltage. Given that we are discussing interfacing 5V systems to 3.3V systems, we can assume that we have a stable 5 VDC supply. This section will present voltage regulator solutions designed for the 5V to 3.3V transition. A design with only modest current requirements may use a simple linear regulator. Higher current needs may dictate a switching regulator solution. Cost sensitive applications may need the simplicity of a discrete diode regulator. Examples from each of these areas are included here, with the necessary support information to adapt to a wide variety of end applications.

Table 1: Power Supply Comparisons

| Method                    | <b>V</b> REG | ΙQ                   | Eff. | Size             | Cost | Transient<br>Response |

|---------------------------|--------------|----------------------|------|------------------|------|-----------------------|

| Zener<br>Shun<br>Reg.     | 10%<br>Typ   | 5 mA                 | 60%  | Sm               | Low  | Poor                  |

| Series<br>Linear<br>Reg.  | 0.4%<br>Typ  | 1 μA<br>to<br>100 μA | 60%  | Sm               | Med  | Excellent             |

| Switching<br>Buck<br>Reg. | 0.4%<br>Typ  | 30 µA<br>to<br>2 mA  | 93%  | Med<br>to<br>Lrg | High | Good                  |

# TIP #1 Powering 3.3V Systems From 5V Using an LDO Regulator

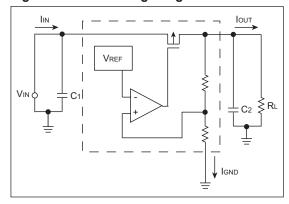

The dropout voltage of standard three-terminal linear regulators is typically 2.0-3.0V. This precludes them from being used to convert 5V to 3.3V reliably. Low Dropout (LDO) regulators, with a dropout voltage in the few hundred milli-volt range, are perfectly suited for this type of application. Figure 1-1 contains a block diagram of a basic LDO system with appropriate current elements labeled. From this figure it can be seen that an LDO consists of four main elements:

- 1. Pass transistor

- 2. Bandgap reference

- 3. Operational amplifier

- 4. Feedback resistor divider

When selecting an LDO, it is important to know what distinguishes one LDO from another. Device quiescent current, package size and type are important device parameters. Evaluating for each parameter for the specific application yields an optimal design.

Figure 1-1: LDO Voltage Regulator

An LDOs quiescent current, Iq, is the device ground current, IgND, while the device is operating at no load. IgND is the current used by the LDO to perform the regulating operation. The efficiency of an LDO can be approximated as the output voltage divided by the input voltage when IouT>>Iq. However, at light loads, the Iq must be taken into account when calculating the efficiency. An LDO with lower Iq will have a higher light load efficiency. This increase in light load efficiency has a negative effect on the LDO performance. Higher quiescent current LDOs are able to respond quicker to sudden line and load transitions.

## TIP #2 Low-Cost Alternative Power System Using a Zener Diode

Details a low-cost regulator alternative using a Zener diode.

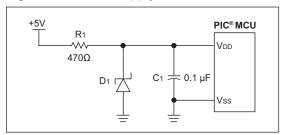

Figure 2-1: Zener Supply

A simple, low-cost 3.3V regulator can be made out of a Zener diode and a resistor as shown in Figure 2-1. In many applications, this circuit can be a cost-effective alternative to using a LDO regulator. However, this regulator is more load sensitive than a LDO regulator. Additionally, it is less energy efficient, as power is always being dissipated in R1 and D1.

R1 limits the current to D1 and the PIC MCU so that VDD stays within the allowable range. Because the reverse voltage across a Zener diode varies as the current through it changes, the value of R1 needs to be considered carefully.

R1 must be sized so that at maximum load, typically when the PIC MCU is running and is driving its outputs high, the voltage drop across R1 is low enough so that the PIC MCU has enough voltage to operate. Also, R1 must be sized so that at minimum load, typically when the PIC MCU is in Reset, that VDD does not exceed either the Zener diode's power rating or the maximum VDD for the PIC MCU.

### TIP #3 Lower Cost Alternative Power System Using 3 Rectifier Diodes

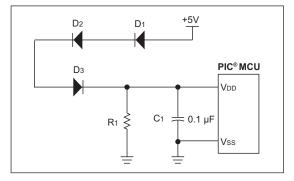

Figure 3-1 details a lower cost regulator alternative using 3 rectifier diodes.

Figure 3-1: Diode Supply

We can also use the forward drop of a series of normal switching diodes to drop the voltage going into the PIC MCU. This can be even more cost-effective than the Zener diode regulator. The current draw from this design is typically less than a circuit using a Zener.

The number of diodes needed varies based on the forward voltage of the diode selected. The voltage drop across diodes D1-D3 is a function of the current through the diodes. R1 is present to keep the voltage at the PIC MCUs VDD pin from exceeding the PIC MCUs maximum VDD at minimum loads (typically when the PIC MCU is in Reset or sleeping). Depending on the other circuitry connected to VDD, this resistor may have its value increased or possibly even eliminated entirely. Diodes D1-D3 must be selected so that at maximum load, typically when the PIC is running and is driving its outputs high, the voltage drop across D1-D3 is low enough to meet the PIC MCUs minimum VDD requirements.

# TIP #4 Powering 3.3V Systems From 5V Using Switching Regulators

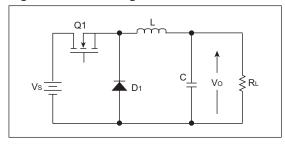

A buck switching regulator, shown in Figure 4-1, is an inductor-based converter used to step-down an input voltage source to a lower magnitude output voltage. The regulation of the output is achieved by controlling the ON time of MOSFET Q1. Since the MOSFET is either in a lower or high resistive state (ON or OFF, respectively), a high source voltage can be converted to a lower output voltage very efficiently.

The relationship between the input and output voltage can be established by balancing the volt-time of the inductor during both states of Q1.

#### Equation 4-1

$$(Vs - Vo) * ton = Vo * (T - ton)$$

Where:  $T \equiv ton/Duty Cycle$

It therefore follows that for MOSFET Q1:

#### **Equation 4-2**

When choosing an inductor value, a good starting point is to select a value to produce a maximum peak-to-peak ripple current in the inductor equal to ten percent of the maximum load current.

#### Equation 4-3

$$V = L * (di/dt)$$

$L = (Vs - Vo) * (ton/lo * 0.10)$

When choosing an output capacitor value, a good starting point is to set the LC filter characteristic impedance equal to the load resistance. This produces an acceptable voltage overshoot when operating at full load and having the load abruptly removed.

#### Equation 4-4

$$Z_0 \equiv \sqrt{L/C}$$

$$C = L/R^2 = (I_0^2 * L)/V_0^2$$

When choosing a diode for D1, choose a device with a sufficient current rating to handle the inductor current during the discharge part of the pulse cycle (I<sub>L</sub>).

Figure 4-1: Buck Regulator

#### **Digital Interfacing**

When interfacing two devices that operate at different voltages, it is imperative to know the output and input thresholds of both devices. Once these values are known, a technique can be selected for interfacing the devices based on the other requirements of your application. Table 4-1 contains the output and input thresholds that will be used throughout this document. When designing an interface, make sure to reference your manufacturers data sheet for the actual threshold levels.

Table 4-1: Input/Output Thresholds

|                | Vон min            | Vol max | V⊪ min            | VIL max           |

|----------------|--------------------|---------|-------------------|-------------------|

| 5V TTL         | 2.4V               | 0.5V    | 2.0V              | 0.8V              |

| 3.3V<br>LVTTL  | 2.4V               | 0.4V    | 2.0V              | 0.8V              |

| 5V<br>CMOS     | 4.7V<br>(Vcc-0.3V) | 0.5V    | 3.5V<br>(0.7xVcc) | 1.5V<br>(0.3xVcc) |

| 3.3V<br>LVCMOS | 3.0V<br>(Vcc-0.3V) | 0.5V    | 2.3V<br>(0.7xVcc) | 1.0V<br>(0.3xVcc) |

#### TIP #5 3.3V → 5V Direct Connect

The simplest and most desired way to connect a 3.3V output to a 5V input is by a direct connection. This can be done only if the following 2 requirements are met:

- The Voн of the 3.3V output is greater than the Viн of the 5V input

- The Vol of the 3.3V output is less than the Vil of the 5V input

An example of when this technique can be used is interfacing a 3.3V LVCMOS output to a 5V TTL input. From the values given in Table 4-1, it can clearly be seen that both of these requirements are met.

3.3V LVCMOS VoH of 3.0 volts is greater than 5V TTL ViH of 2.0 volts, and

3.3V LVCMOS VoL of 0.5 volts is less than 5V TTL VII of 0.8 volts.

When both of these requirements are not met, some additional circuitry will be needed to interface the two parts. See Tips 6, 7, 8 and 13 for possible solutions.

## TIP #6 3.3V → 5V Using a MOSFET Translator

In order to drive any 5V input that has a higher Vih than the Voh of a 3.3V CMOS part, some additional circuitry is needed. A low-cost two component solution is shown in Figure 6-1.

When selecting the value for R1, there are two parameters that need to be considered; the switching speed of the input and the current consumption through R1. When switching the input from a '0' to a '1', you will have to account for the time the input takes to rise because of the RC time constant formed by R1, and the input capacitance of the 5V input plus any stray capacitance on the board. The speed at which you can switch the input is given by the following equation:

#### **Equation 6-1**

Tsw =

$$3 \times R1 \times (Cin + Cs)$$

Since the input and stray capacitance of the board are fixed, the only way to speed up the switching of the input is to lower the resistance of R1. The trade-off of lowering the resistance of R1 to get faster switching times is the increase in current draw when the 5V input remains low. The switching to a '0' will typically be much faster than switching to a '1' because the ON resistance of the N-channel MOSFET will be much smaller than R1. Also, when selecting the N-channel FET, select a FET that has a lower VGS threshold voltage than the VOH of 3.3V output.

Figure 6-1: MOSFET Translator

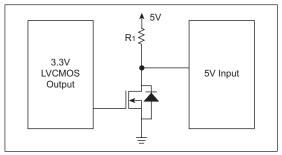

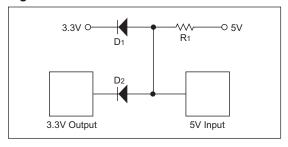

## TIP #7 3.3V → 5V Using a Diode Offset

The inputs voltage thresholds for 5V CMOS and the output drive voltage for 3.3V LVTTL and LVCMOS are listed in Table 7-1.

Table 7-1: Input/Output Thresholds

|                   | 5V CMOS<br>Input | 3.3V LVTTL<br>Output | 3.3V LVCMOS<br>Output |

|-------------------|------------------|----------------------|-----------------------|

| High<br>Threshold | > 3.5V           | > 2.4V               | > 3.0V                |

| Low<br>Threshold  | < 1.5V           | < 0.4V               | < 0.5V                |

Note that both the high and low threshold input voltages for the 5V CMOS inputs are about a volt higher than the 3.3V outputs. So, even if the output from the 3.3V system could be offset, there would be little or no margin for noise or component tolerance. What is needed is a circuit that offsets the outputs and increases the difference between the high and low output voltages.

Figure 7-1: Diode Offset

When output voltage specifications are determined, it is done assuming that the output is driving a load between the output and ground for the high output, and a load between 3.3V and the output for the low output. If the load for the high threshold is actually between the output and 3.3V, then the output voltage is actually much higher as the load resistor is the mechanism that is pulling the output up, instead of the output transistor.

If we create a diode offset circuit (see Figure 7-1), the output low voltage is increased by the forward voltage of the diode D1, typically 0.7V, creating a low voltage at the 5V CMOS input of 1.1V to 1.2V. This is well within the low threshold input voltage for the 5V CMOS input. The output high voltage is set by the pull-up resistor and diode D2, tied to the 3.3V supply. This puts the output high voltage at approximately 0.7V above the 3.3V supply, or 4.0 to 4.1V, which is well above the 3.5V threshold for the 5V CMOS input.

Note: For the circuit to work properly, the pull-up resistor must be significantly smaller than the input resistance of the 5V CMOS input, to prevent a reduction in the output voltage due to a resistor divider effect at the input. The pull-up resistor must also be large enough to keep the output current loading on the 3.3V output within the specification of the device.

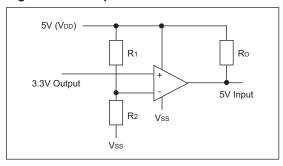

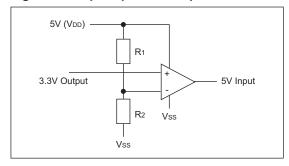

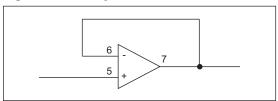

# TIP #8 3.3V → 5V Using a Voltage Comparator

The basic operation of the comparator is as follows:

- When the voltage at the inverting (-) input is greater than that at the non-inverting (+) input, the output of the comparator swings to Vss.

- When the voltage at the non-inverting (+) input is greater than that at the non-inverting (-) input, the output of the comparator is in a high state.

To preserve the polarity of the 3.3V output, the 3.3V output must be connected to the non-inverting input of the comparator. The inverting input of the comparator is connected to a reference voltage determined by R1 and R2, as shown in Figure 8-1.

Figure 8-1: Comparator Translator

#### Calculating R1 and R2

The ratio of R1 and R2 depends on the logic levels of the input signal. The inverting input should be set to a voltage halfway between VoL and VoH for the 3.3V output. For an LVCMOS output, this voltage is:

#### Equation 8-1:

$$1.75V = \frac{(3.0V + .5V)}{2}$$

Given that R1 and R2 are related by the logic levels:

#### Equation 8-2:

$$R_1 = R_2 \quad \left( \begin{array}{cc} 5V \\ \hline 1.75V \end{array} \right)$$

assuming a value of 1K for R2, R1 is 1.8K.

An op amp wired up as a comparator can be used to convert a 3.3V input signal to a 5V output signal. This is done using the property of the comparator that forces the output to swing high (VDD) or low (Vss), depending on the magnitude of difference in voltage between its 'inverting' input and 'non-inverting' input.

**Note:** For the op amp to work properly when powered by 5V, the output must be capable of rail-to-rail drive.

Figure 8-2: Op Amp as a Comparator

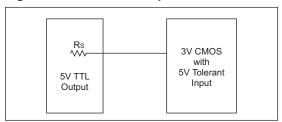

#### TIP #9 5V → 3.3V Direct Connect

5V outputs have a typical VoH of 4.7 volts and a VoL of 0.4 volts and a 3.3V LVCMOS input will have a typical ViH of 0.7 x VDD and a VIL of 0.2 x VDD.

When the 5V output is driving low, there are no problems because the 0.4 volt output is less than in the input threshold of 0.8 volts. When the 5V output is high, the VoH of 4.7 volts is greater than 2.1 volt VIH, therefore, we can directly connect the 2 pins with no conflicts if the 3.3V CMOS input is 5 volt tolerant.

Figure 9-1: 5V Tolerant Input

If the 3.3V CMOS input is not 5 volt tolerant, then there will be an issue because the maximum volt specification of the input will be exceeded.

See Tips 10-13 for possible solutions.

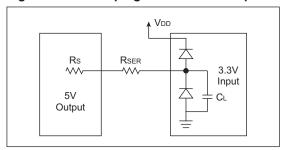

## TIP #10 5V $\rightarrow$ 3.3V With Diode Clamp

Many manufacturers protect their I/O pins from exceeding the maximum allowable voltage specification by using clamping diodes. These clamping diodes keep the pin from going more than a diode drop below Vss and a diode drop above VDD. To use the clamping diode to protect the input, you still need to look at the current through the clamping diode. The current through the clamp diodes should be kept small (in the micro amp range). If the current through the clamping diodes gets too large, then you risk the part latching up. Since the source resistance of a 5V output is typically around  $10\Omega$ , an additional series resistor is still needed to limit the current through the clamping diode as shown Figure 10-1. The consequence of using the series resistor is it will reduce the speed at which we can switch the input because the RC time constant formed the capacitance of the pin (C<sub>L</sub>).

Figure 10-1: Clamping Diodes on the Input

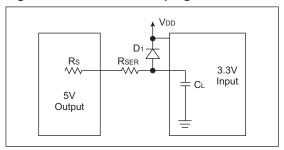

If the clamping diodes are not present, a single external diode can be added to the circuit as shown in Figure 10-2.

Figure 10-2: Without Clamping Diodes

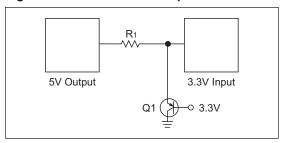

## TIP #11 5V $\rightarrow$ 3.3V Active Clamp

One problem with using a diode clamp is that it injects current onto the 3.3V power supply. In designs with a high current 5V outputs, and lightly loaded 3.3V power supply rails, this injected current can float the 3.3V supply voltage above 3.3V. To prevent this problem, a transistor can be substituted which routes the excess output drive current to ground instead of the 3.3V supply. Figure 11-1 shows the resulting circuit.

Figure 11-1: Transistor Clamp

The base-emitter junction of Q1 performs the same function as the diode in a diode clamp circuit. The difference is that only a small percentage of the emitter current flows out of the base of the transistor to the 3.3V rail, the bulk of the current is routed to the collector where it passes harmlessly to ground. The ratio of base current to collector current is dictated by the current gain of the transistor, typically 10-400, depending upon which transistor is used.

## TIP #12 5V → 3.3V Resistor Divider

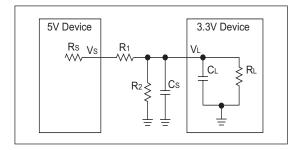

A simple resistor divider can be used to reduce the output of a 5V device to levels appropriate for a 3.3V device input. An equivalent circuit of this interface is shown in Figure 12-1.

Figure 12-1: Resistive Interface Equivalent Circuit

Typically, the source resistance, Rs, is very small (less than  $10\Omega$ ) so its affect on R1 will be negligible provided that R1 is chosen to be much larger than Rs. At the receive end, the load resistance, RL, is very large (greater than  $500~k\Omega$ ) so its affect on R2 will be negligible provided that R2 is chosen to be much less than RL.

There is a trade-off between power dissipation and transition times. To keep the power requirements of the interface circuit at a minimum, the series resistance of R1 and R2 should be as large as possible. However, the load capacitance, which is the combination of the stray capacitance, Cs, and the 3.3V device input capacitance, CL, can adversely affect the rise and fall times of the input signal. Rise and fall times can be unacceptably long if R1 and R2 are too large.

Neglecting the affects of Rs and RL, the formula for determining the values for R1 and R2 is given by Equation 12-1.

#### **Equation 12-1: Divider Values**

$$\frac{V_S}{R_1 + R_2} = \frac{V_L}{R_2} \quad ; \text{ General relationship}$$

$$R_1 = \frac{(V_S - V_L) \cdot R_2}{V_L} \quad ; \text{ Solving for R1}$$

$$R_1 = 0.515 \cdot R_2 \quad ; \text{ Substituting voltages}$$

The formula for determining the rise and fall times is given in Equation 12-2. For circuit analysis, the Thevenin equivalent is used to determine the applied voltage, VA, and the series resistance, R. The Thevenin equivalent is defined as the open circuit voltage divided by the short circuit current. The Thevenin equivalent, R, is determined to be 0.66\*R1 and the Thevenin equivalent, VA, is determined to be 0.66\*Vs for the circuit shown in Figure 12-2 according to the limitations imposed by Equation 12-2.

## Equation 12-2: Rise/Fall Time

$$t = -\left[R \cdot C \cdot \ln\left(\frac{V_F - V_A}{V_I - V_A}\right)\right]$$

Where:

t = Rise or Fall time

R = 0.66\*R1 C = Cs+CI

V<sub>I</sub> = Initial voltage on C (V<sub>L</sub>)

$V_F = Final \ voltage \ on \ C (V_L)$

$V_A = Applied voltage (0.66*Vs)$

As an example, suppose the following conditions exist:

- Stray capacitance = 30 pF

- Load capacitance = 5 pF

- Maximum rise time from 0.3V to 3V  $\leq$  1  $\mu$ S

- Applied source voltage Vs = 5V

The calculation to determine the *maximum* resistances is shown in Equation 12-3.

#### **Equation 12-3: Example Calculation**

Solve Equation 12-2 for R:

$$R = - \left[ \frac{t}{C \cdot \ln \left( \frac{V_F - V_A}{V_I - V_A} \right)} \right]$$

Substitute values:

$$R = - \left[ \frac{10 \cdot 10^{-7}}{35 \cdot 10^{-12} \cdot \ln \left( \frac{3 - (0.66 \cdot 5)}{0.3 - (0.66 \cdot 5)} \right)} \right]$$

Thevenin equivalent maximum R:

R = 12408

Solve for maximum R1 and R2:

$$R1 = 0.66 \cdot R$$

$R2 = \frac{R1}{0.515}$

$$R1 = 8190$$

$R2 = 15902$

#### TIP #13 3.3V → 5V Level Translators

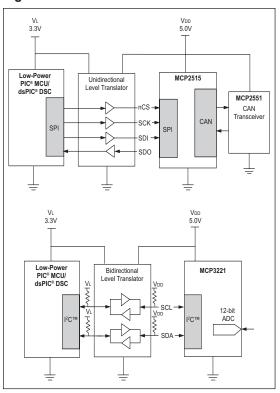

While level translation can be done discretely, it is often preferred to use an integrated solution. Level translators are available in a wide range of capabilities. There are unidirectional and bidirectional configurations, different voltage translations and different speeds, all giving the user the ability to select the best solution.

Board-level communication between devices (e.g., MCU to peripheral) is most often done by either SPI or I<sup>2</sup>C™. For SPI, it may be appropriate to use a unidirectional level translator and for I<sup>2</sup>C, it is necessary to use a bidirectional solution. Figure 13-1 illustrates both solutions.

Figure 13-1: Level Translator

#### Analog

The final 3.3V to 5V interface challenge is the translation of analog signals across the power supply barrier. While low level signals will probably not require external circuitry, signals moving between 3.3V and 5V systems will be affected by the change in supply. For example, a 1V peak analog signal converted by an ADC in a 3.3V system will have greater resolution than an ADC in a 5V system, simply because more of the ADCs range is used to convert the signal in the 3.3V ADC. Alternately, the relatively higher signal amplitude in a 3.3V system may have problems with the system's lower common mode voltage limitations.

Therefore, some interface circuitry, to compensate for the differences, may be needed. This section will discuss interface circuitry to help alleviate these problems when the signal makes the transition between the different supply voltages.

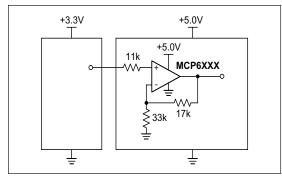

## TIP #14 3.3V $\rightarrow$ 5V Analog Gain Block

To scale analog voltage up when going from 3.3V supply to 5V supply. The 33 k $\Omega$  and 17 k $\Omega$  set the op amp gain so that the full scale range is used in both sides. The 11 k $\Omega$  resistor limits current back to the 3.3V circuitry.

Figure 14-1: Analog Gain Block

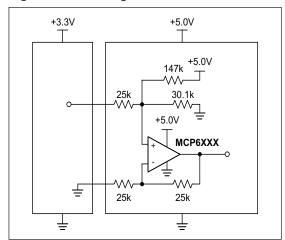

### TIP #15 3.3V → 5V Analog Offset Block

Offsetting an analog voltage for translation between 3.3V and 5V.

Shift an analog voltage from 3.3V supply to 5V supply. The 147 k $\Omega$  and 30.1 k $\Omega$  resistors on the top right and the +5V supply voltage are equivalent to a 0.85V voltage source in series with a 25 k $\Omega$  resistor. This equivalent 25 k $\Omega$  resistance, the three 25 k $\Omega$  resistors, and the op amp form a difference amplifier with a gain of 1 V/V. The 0.85V equivalent voltage source shifts any signal seen at the input up by the same amount; signals centered at 3.3V/2 = 1.65V will also be centered at 5.0V/2 = 2.50V. The top left resistor limits current from the 5V circuitry.

Figure 15-1: Analog Offset Block

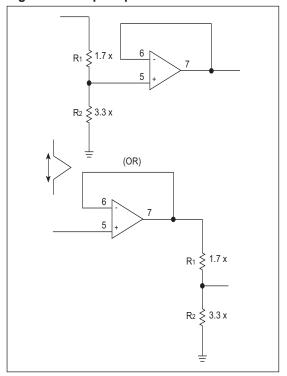

## TIP #16 5V → 3.3V Active Analog Attenuator

Reducing a signal's amplitude from a 5V to 3.3V system using an op amp.

The simplest method of converting a 5V analog signal to a 3.3V analog signal is to use a resistor divider with a ratio R1:R2 of 1.7:3.3. However, there are a few problems with this.

- 1. The attenuator may be feeding a capacitive load, creating an unintentional low pass filter.

- The attenuator circuit may need to drive a low-impedance load from a high-impedance source.

Under either of these conditions, an op amp becomes necessary to buffer the signals.

The op amp circuit necessary is a unity gain follower (see Figure 16-1).

Figure 16-1: Unity Gain

This circuit will output the same voltage that is applied to the input.

To convert the 5V signal down to a 3V signal, we simply add the resistor attenuator.

Figure 16-2: Op Amp Attenuators

If the resistor divider is before the unity gain follower, then the lowest possible impedance is provided for the 3.3V circuits. Also, the op amp can be powered from 3.3V, saving some power. If the X is made very large, then power consumed by the 5V side can be minimized.

If the attenuator is added after the unity gain follower, then the highest possible impedance is presented to the 5V source. The op amp must be powered from 5V and the impedance at the 3V side will depend upon the value of R1||R2.

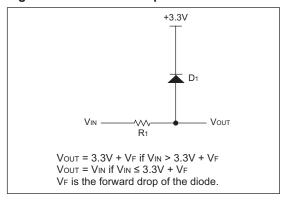

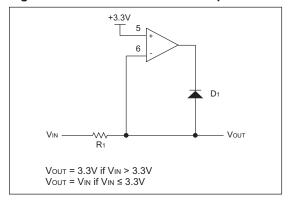

## TIP #17 5V → 3V Analog Limiter

When moving a 5V signal down to a 3.3V system, it is sometimes possible to use the attenuation as gain. If the desired signal is less than 5V, then attaching that signal to a 3.3V ADC will result in larger conversion values. The danger is when the signal runs to the 5V rail. A method is therefore required to control the out-of-range voltages while leaving the in-range voltages unaffected. Three ways to accomplish this will be discussed here.

- 1. Using a diode to clamp the overvoltage to the 3.3V supply.

- 2. Using a Zener diode to clamp the voltage to any desired limit.

- 3. Using an op amp with a diode to perform a precision clamp.

The simplest method to perform the overvoltage clamp is identical to the simple method of interfacing a 5V digital signal to the 3.3V digital signals. A resistor and a diode are used to direct excess current into the 3.3V supply. The resistor must be sized to protect the diode and the 3.3V supply while not adversely affecting the analog performance. If the impedance of the 3.3V supply is too low, then this type of clamp can cause the 3.3V supply voltage to increase. Even if the 3.3V supply has a good low-impedance, this type of clamp will allow the input signal to add noise to the 3.3V supply when the diode is conducting and if the frequency is high enough, even when the diode is not conducting due to the parasitic capacitance across the diode.

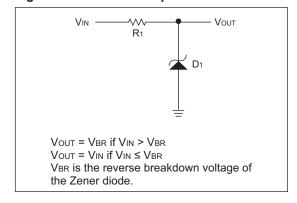

Figure 17-1: Diode Clamp

To prevent the input signal from affecting the supply or to make the input more robust to larger transients, a variation is to use a Zener diode. The Zener diode is slower than the fast signal diode typically used in the first circuit. However, they are generally more robust and do not rely on the characteristics of the power supply to perform the clamping. The amount of clamping they provide is dependant upon the current through the diode. This is set by the value of R1. R1 may not be required if the output impedance of the VIN source is sufficiently large.

Figure 17-2: Zener Clamp

If a more precise overvoltage clamp is required that does not rely upon the supply, then an op amp can be employed to create a precision diode. In Figure 17-3, such a circuit is shown. The op amp compensates for the forward drop in the diode and causes the voltage to be clamped at exactly the voltage supplied on the non-inverting input to the op amp. The op amp can be powered from 3.3V if it is rail-to-rail.

Figure 17-3: Precision Diode Clamp

Because the clamping is performed by the op amp, there is no affect on the power supply. The impedance presented to the low voltage circuit is not improved by the op amp, it remains R1 in addition to the source circuit impedance.

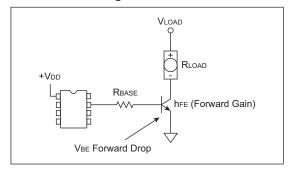

## **TIP #18 Driving Bipolar Transistors**

When driving bipolar transistors, the amount of base current "drive" and forward current gain

(B/hFE) will determine how much current the transistor can sink. When driven by a microcontroller I/O port, the base drive current is calculated using the port voltage and the port current limit (typically 20 mA). When using 3.3V technology, smaller value base current limiting resistors should be used to ensure sufficient base drive to saturate the transistor.

Figure 18-1: Driving Bipolar Transistors

Using Microcontroller I/O Port

The value of RBASE will depend on the microcontroller supply voltage. Equation 18-1 describes how to calculate RBASE.

Table 18-1: Bipolar Transistor DC Specifications

| Characteristic                            | Sym                 | Min               | Max               | Unit | Test<br>Condition                      |  |  |  |

|-------------------------------------------|---------------------|-------------------|-------------------|------|----------------------------------------|--|--|--|

| OFF CHARACTER                             | OFF CHARACTERISTICS |                   |                   |      |                                        |  |  |  |

| Collector-Base<br>Breakdown<br>Voltage    | V(BR)CBO            | 60                | -                 | V    | Ic = 50 μA,<br>IE = 0                  |  |  |  |

| Collector-Emitter<br>Breakdown<br>Voltage | V(BR)CEO            | 50                | -                 | V    | Ic = 1.0<br>mA,<br>I <sub>B</sub> = 0  |  |  |  |

| Emitter-Base<br>Breakdown<br>Voltage      | V(BR)EBO            | 7.0               | _                 | V    | IE = 50 μA,<br>IC = 0                  |  |  |  |

| Collector Cutoff<br>Current               | Ісво                | -                 | 100               | nA   | V <sub>CB</sub> = 60V                  |  |  |  |

| Emitter Cutoff<br>Current                 | ІЕВО                | -                 | 100               | nA   | V <sub>EB</sub> = 7.0V                 |  |  |  |

| ON CHARACTERISTICS                        |                     |                   |                   |      |                                        |  |  |  |

| DC Current Gain                           | hfE                 | 120<br>180<br>270 | 270<br>390<br>560 | _    | VcE = 6.0V,<br>Ic = 1.0 mA             |  |  |  |

| Collector-Emitter<br>Saturation Voltage   | VCE(SAT)            | -                 | 0.4               | V    | Ic = 50 mA,<br>I <sub>B</sub> = 5.0 mA |  |  |  |

When using bipolar transistors as switches to turn on and off loads controlled by the microcontroller I/O port pin, use the minimum hee specification and margin to ensure complete device saturation.

Equation 18-1: Calculating the Base Resistor Value

$$R_{BASE} = \frac{(V_{DD} - V_{BE}) \times h_{FE} \times R_{LOAD}}{V_{LOAD}}$$

#### **3V Technology Example**

$V_{DD}$  = +3V,  $V_{LOAD}$  = +40V,  $R_{LOAD}$  = 400 $\Omega$ , hre min. = 180,  $V_{BE}$  = 0.7V

RBASE = 4.14 k $\Omega$ , I/O port current = 556  $\mu$ A

#### **5V Technology Example**

$V_{DD}$  = +5V,  $V_{LOAD}$  = +40V,  $R_{LOAD}$  = 400 $\Omega$ , hre min. = 180,  $V_{BE}$  = 0.7V

RBASE =  $7.74 \text{ k}\Omega$ , I/O port current =  $556 \mu\text{A}$

For both examples, it is good practice to increase base current for margin. Driving the base with 1 mA to 2 mA would ensure saturation at the expense of increasing the input power consumption.

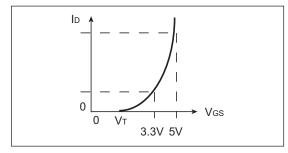

## TIP #19 Driving N-Channel MOSFET Transistors

Care must be taken when selecting an external N-Channel MOSFET for use with a 3.3V microcontroller. The MOSFET gate threshold voltage is an indication of the device's capability to completely saturate. For 3.3V applications, select MOSFETs that have an ON resistance rating for gate drive of 3V or less. For example, a FET that is rated for 250 µA of drain current with 1V applied from gate-to-source is not necessarily going to deliver satisfactory results for 100 mA load with a 3.3V drive. When switching from 5V to 3V technology, review the gate-to-source threshold and ON resistance characteristics very carefully as shown in Figure 19-1. A small decrease in gate drive voltage can significantly reduce drain current.

Figure 19-1: Drain Current Capability Versus

Gate to Source Voltage

Low threshold devices commonly exist for MOSFETs with drain-to-source voltages rated below 30V. MOSFETs with drain-to-source voltages above 30V typically have higher gate thresholds (VT).

Table 19-1: RDS(ON) and VGS(th)

Specifications for IRF7467

|         | Static Drain-<br>to-Source<br>On-Resistance | -   | 9.4  | 12   | mΩ | V <sub>G</sub> S = 10V,<br>I <sub>D</sub> = 11A                |

|---------|---------------------------------------------|-----|------|------|----|----------------------------------------------------------------|

| Ros(on) |                                             | -   | 10.6 | 13.5 |    | V <sub>GS</sub> = 4.5V,<br>I <sub>D</sub> = 9.0A               |

|         |                                             | -   | 17   | 35   |    | V <sub>GS</sub> = 2.8V,<br>I <sub>D</sub> = 5.5A               |

| Vgs(th) | Gate<br>Threshold<br>Voltage                | 0.6 | -    | 2.0  | V  | V <sub>DS</sub> = V <sub>GS</sub> ,<br>I <sub>D</sub> = 250 μA |

As shown in Table 19-1, the threshold voltage for this 30V, N-Channel MOSFET switch is 0.6V. The resistance rating for this MOSFET is 35 m $\Omega$  with 2.8V applied gate, as a result, this device is well suited for 3.3V applications.

Table 19-2: RDS(ON) and VGS(th)

Specifications for IRF7201

|  | Ros(on) | Static Drain-<br>to-Source   | -   | - | 0.030 | Ω | V <sub>GS</sub> = 10V,<br>I <sub>D</sub> = 7.3A                |

|--|---------|------------------------------|-----|---|-------|---|----------------------------------------------------------------|

|  |         | On-Resistance                | -   | - | 0.050 |   | V <sub>GS</sub> = 4.5V,<br>I <sub>D</sub> = 3.7A               |

|  | Vgs(th) | Gate<br>Threshold<br>Voltage | 1.0 | - | -     | V | V <sub>DS</sub> = V <sub>GS</sub> ,<br>I <sub>D</sub> = 250 μA |

For the IRF7201 data sheet specifications, the gate threshold voltage is specified as a 1.0V minimum. This does not mean the device can be used to switch current with a 1.0V gate-to-source voltage as there is no RDS(ON) specification for VGS(th) values below 4.5V. This device is not recommended for 3.3V drive applications that require low switch resistance but can be used for 5V drive applications.

| NOTES: |  |

|--------|--|

|--------|--|

## **Sales Office Listing**

**AMERICAS**

**Atlanta**

Tel: 678-957-9614

**Boston**

Tel: 774-760-0087

Chicago

Tel: 630-285-0071

Cleveland

Tel: 216-447-0464

**Dallas**

Tel: 972-818-7423

**Detroit**

Tel: 248-538-2250

Kokomo

Tel: 765-864-8360

Los Angeles

Tel: 949-462-9523

Santa Clara

Tel: 408-961-6444

Toronto

Mississauga, Ontario Tel: 905-673-0699 **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39

**Denmark - Copenhagen** Tel: 45-4450-2828

France - Paris

Tel: 33-1-69-53-63-20

**Germany - Munich**

Tel: 49-89-627-144-0

Italy - Milan

Tel: 39-0331-742611

Netherlands - Drunen

Tel: 31-416-690399

**Spain - Madrid** Tel: 34-91-708-08-90

UK - Wokingham

Tel: 44-118-921-5869

ASIA/PACIFIC

Australia - Sydney

Tel: 61-2-9868-6733

China - Beijing

Tel: 86-10-8528-2100

China - Chengdu

Tel: 86-28-8665-5511

China - Hong Kong SAR

Tel: 852-2401-1200 **China - Nanjing**

Tel: 86-25-8473-2460

China - Qingdao

Tel: 86-532-8502-7355

China - Shanghai

Tel: 86-21-5407-5533 **China - Shenvang**

Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8203-2660

China - Wuhan

Tel: 86-27-5980-5300

China - Xiamen

Tel: 86-592-2388138

China - Xian

Tel: 86-29-8833-7252

China - Zhuhai

Tel: 86-756-3210040

ASIA/PACIFIC

India - Bangalore

Tel: 91-80-4182-8400

India - New Delhi Tel: 91-11-4160-8631

India - Pune

Tel: 91-20-2566-1512

Japan - Yokohama

Tel: 81-45-471- 6166

Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila

Tel: 63-2-634-9065

Singapore

Tel: 65-6334-8870

Taiwan - Hsin Chu

Tel: 886-3-572-9526 **Taiwan - Kaohsiung**

Tel: 886-7-536-4818

Taiwan - Taipei

Tel: 886-2-2500-6610

Thailand - Bangkok

Tel: 66-2-694-1351

1/30/07

Microchip Technology Inc. · 2355 W. Chandler Blvd. · Chandler, AZ 85224-6199

Microcontrollers • Digital Signal Controllers • Analog • Serial EEPROMs

Information subject to change. The Microchip name and logo, the Microchip logo, dsPIC, MPLAB, PIC, PICmicro and PICSTART are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. FilterLab, MXDEV and MXLAB are registered trademarks of Microchip Technology Incorporated in the U.S.A. ICSP, MPASM, MPLIB, MPLINK, PICDEM, PICDEM, PICDEM are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. © 2008, Microchip Technology Incorporated. All Rights Reserved. Printed in the U.S.A. 2/08