# **APPLICATION NOTE**

# **AN10216-01** I<sup>2</sup>C MANUAL

**Abstract** – The I<sup>2</sup>C Manual provides a broad overview of the various serial buses, why the I<sup>2</sup>C bus should be considered, technical detail of the I<sup>2</sup>C bus and how it works, previous limitations/solutions, comparison to the SMBus, Intelligent Platform Management Interface implementations, review of the different I<sup>2</sup>C devices that are available and patent/royalty information. The I<sup>2</sup>C Manual was presented during the 3 hour TecForum at DesignCon 2003 in San Jose, CA on 27 January 2003.

**Jean-Marc Irazabal** – I<sup>2</sup>C Technical Marketing Manager **Steve Blozis** – I<sup>2</sup>C International Product Manager

**Specialty Logic Product Line Logic Product Group**

**Philips Semiconductors**

March 24, 2003

## **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                                                                                                                                                                                        | ••••••••••••                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| OVERVIEW                                                                                                                                                                                                                 | 4                                         |

| Description                                                                                                                                                                                                              |                                           |

| SERIAL BUS OVERVIEW                                                                                                                                                                                                      | 4                                         |

| UART OverviewSPI OverviewCAN Overview                                                                                                                                                                                    |                                           |

| USB Overview                                                                                                                                                                                                             |                                           |

| I <sup>2</sup> C THEORY OF OPERATION                                                                                                                                                                                     | 13                                        |

| I <sup>2</sup> C Bus Terminology.  START AND STOP CONDITIONS.  HARDWARE CONFIGURATION.  BUS COMMUNICATION.  TERMINOLOGY FOR BUS TRANSFER.  I <sup>2</sup> C DESIGNER BENEFITS.  I <sup>2</sup> C MANUFACTURERS BENEFITS. |                                           |

| OVERCOMING PREVIOUS LIMITATIONS                                                                                                                                                                                          | 18                                        |

| Address Conflicts                                                                                                                                                                                                        | 19 20 20 22 22 22 22 22 22 22 22 22 22 22 |

| DEVELOPMENT TOOLS AND EVALUATION BOARD OVERVIEW                                                                                                                                                                          | 20                                        |

| Purpose of the Development Tool and I <sup>2</sup> C Evaluation Board                                                                                                                                                    | 28                                        |

| COMPARISON OF I <sup>2</sup> C WITH SMBUS                                                                                                                                                                                | 31                                        |

| I <sup>2</sup> C/SMBus compliancy                                                                                                                                                                                        |                                           |

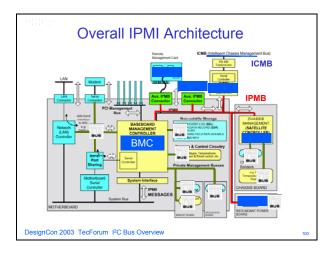

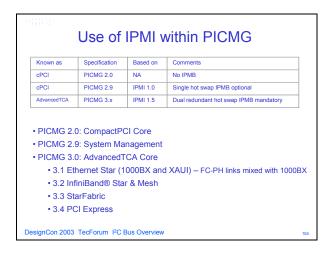

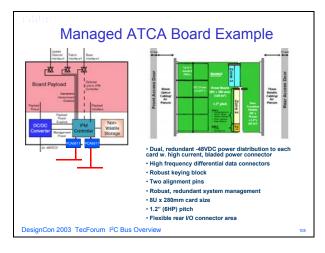

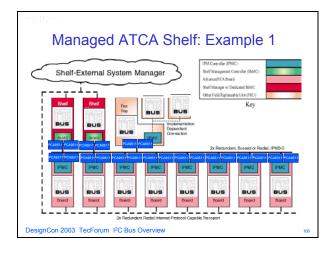

| INTELLIGENT PLATFORM MANAGEMENT INTERFACE (IPMI)                                                                                                                                                                         | 32                                        |

| Intel Server Management                                                                                                                                                                                                  | 33                                        |

| I <sup>2</sup> C DEVICE OVERVIEW                                                                                                                                                                                         | 35                                        |

| TV RECEPTION                                                                                                                                                                                                             | 36                                        |

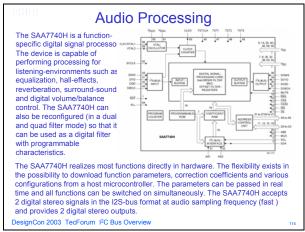

| AUDIO PROCESSING                                | 37 |

|-------------------------------------------------|----|

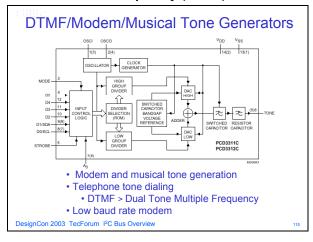

| DUAL TONE MULTI-FREQUENCY (DTMF)                | 37 |

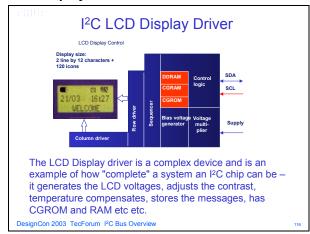

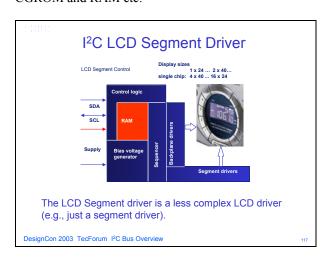

| LCD DISPLAY DRIVER                              | 37 |

| LIGHT SENSOR                                    | 38 |

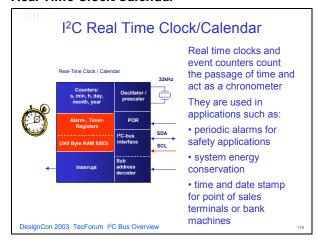

| REAL TIME CLOCK/CALENDAR                        | 38 |

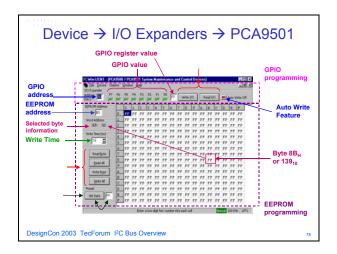

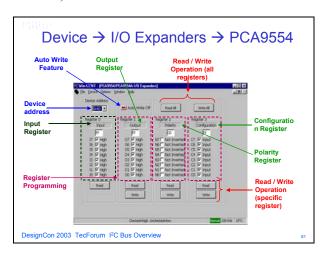

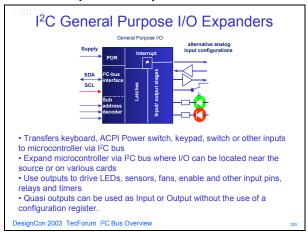

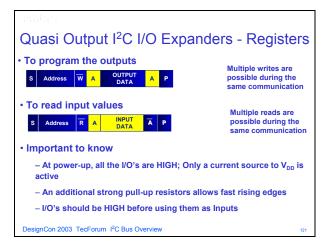

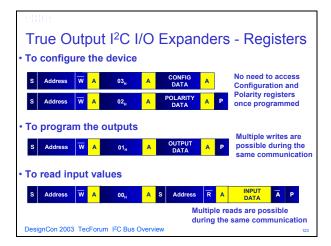

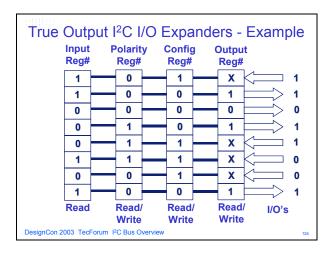

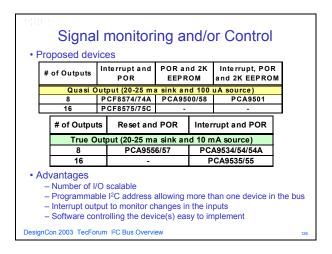

| GENERAL PURPOSE I/O EXPANDERS                   | 38 |

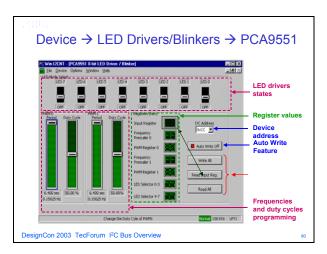

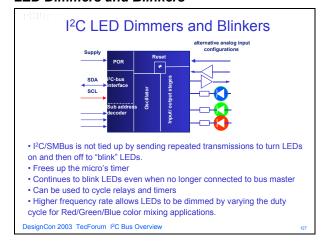

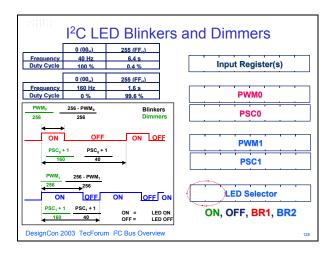

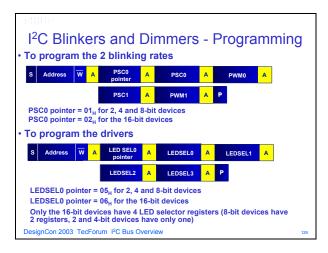

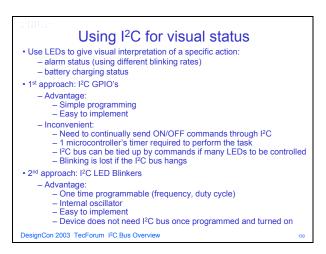

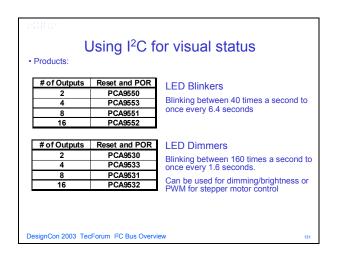

| LED DIMMERS AND BLINKERS                        | 40 |

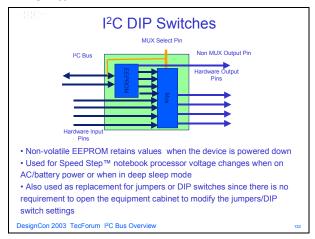

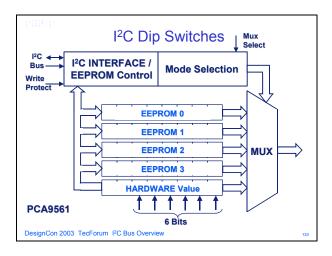

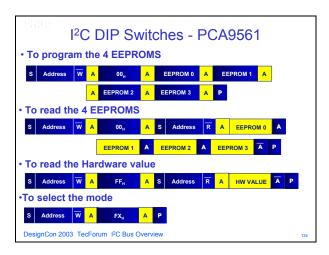

| DIP SWITCH                                      | 42 |

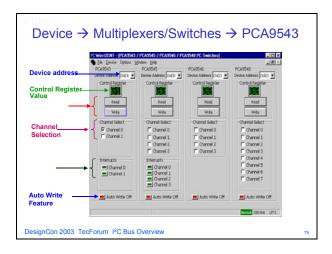

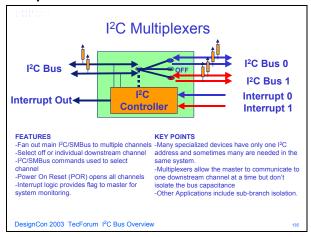

| MULTIPLEXERS AND SWITCHES.                      | 43 |

| VOLTAGE LEVEL TRANSLATORS                       | 45 |

| BUS REPEATERS AND HUBS                          | 45 |

| HOT SWAP BUS BUFFERS                            | 45 |

| BUS EXTENDERS                                   | 46 |

| ELECTRO-OPTICAL ISOLATION                       | 47 |

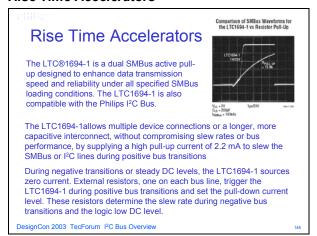

| RISE TIME ACCELERATORS                          | 47 |

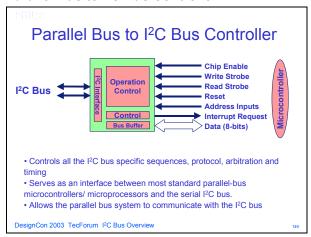

| PARALLEL BUS TO I <sup>2</sup> C BUS CONTROLLER | 48 |

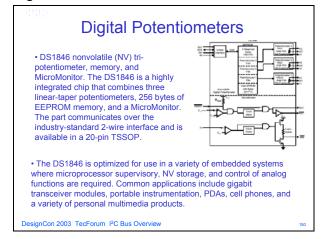

| DIGITAL POTENTIOMETERS                          |    |

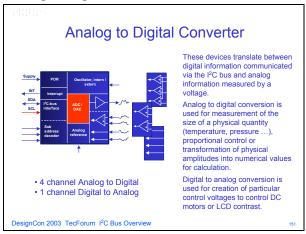

| ANALOG TO DIGITAL CONVERTERS                    | 48 |

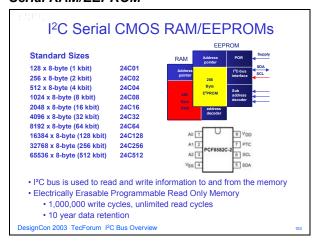

| SERIAL RAM/EEPROM                               | 49 |

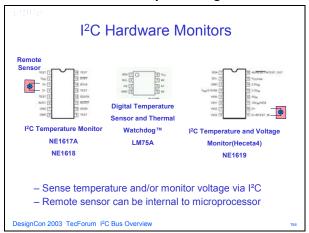

| HARDWARE MONITORS/TEMP & VOLTAGE SENSORS        | 49 |

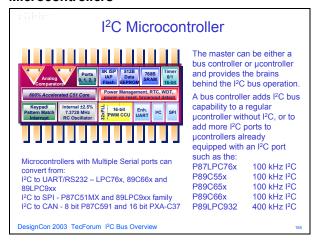

| Microcontrollers                                |    |

| I <sup>2</sup> C PATENT AND LEGAL INFORMATION   | 50 |

| ADDITIONAL INFORMATION                          | 50 |

| APPLICATION NOTES                               | 50 |

#### **OVERVIEW**

#### Description

Philips Semiconductors developed the I<sup>2</sup>C bus over 20 years ago and has an extensive collection of specific use and general purpose devices. This application note was developed from the 3 hour long I<sup>2</sup>C Overview TecForum presentation at DesignCon 2003 in San Jose, CA on 27 January 2003 and provides a broad overview of how the I<sup>2</sup>C bus compares to other serial buses, how the I<sup>2</sup>C bus works, ways to overcome previous limitations, new uses of I<sup>2</sup>C such as in the Intelligent Platform Management Interface, overview of the various different categories of I<sup>2</sup>C devices and patent/royalty information. Full size Slides are posted as a PDF file on the Philips Logic I<sup>2</sup>C collateral web site as **DesignCon 2003 TecForum I<sup>2</sup>C Bus Overview** PDF file. Place holder and title slides have been removed from this application note and some slides with all text have been incorporated into the application note speaker notes.

#### **Serial Bus Overview**

Slide 5

Slide 6

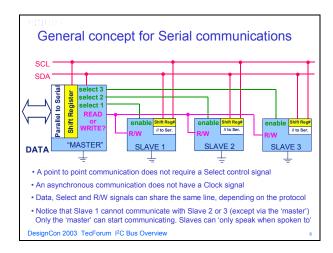

Buses come in two forms, serial and parallel. The data and/or addresses can be sent over 1 wire, bit after bit, or over 8 or 32 wires at once. Always there has to be some way to share the common wiring, some rules, and some synchronization. Slide 6 shows a serial data bus with

three shared signal lines, for bit timing, data, and R/W. The selection of communicating partners is made with one separate wire for each chip. As the number of chips grows, so do the selection wires. The next stage is to use multiplexing of the selection wires and call them an address bus.

If there are 8 address wires we can select any one of 256 devices by using a 'one of 256' decoder IC. In a parallel bus system there could be 8 or 16 (or more) data wires. Taken to the next step, we can share the function of the wires between addresses and data but it starts to take quite a bit of hardware and worst is, we still have lots of wires. We can take a different approach and try to eliminate all except the data wiring itself. Then we need to multiplex the data, the selection (address), and the direction info - read/write. We need to develop relatively complex rules for that, but we save on those wires. This presentation covers buses that use only one or two data lines so that they are still attractive for sending data over reasonable distances - at least a few meters, but perhaps even km.

Slide 7

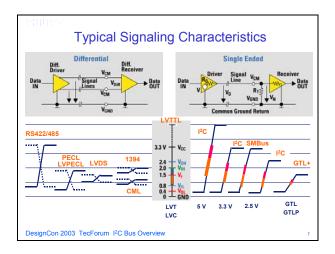

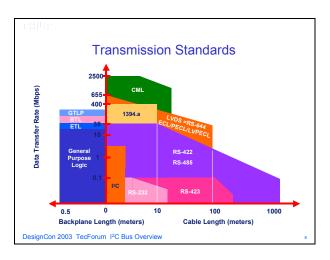

Devices can communicate differentially or single ended with various signal characteristics as shown in Slide 7.

Slide 8

The various data transmission rates vs length or cable or backplane length of the different transmission standards are shown in Slide 8.

|                             | ectivity methods        |

|-----------------------------|-------------------------|

| CAN (1 Wire)                | 33 kHz (typ)            |

| C ('Industrial', and SMBus) | 100 kHz                 |

| PI                          | 110 kHz (original speed |

| AN (fault tolerant)         | 125 kHz                 |

| С                           | 400 kHz                 |

| AN (high speed)             | 1 MHz                   |

| C 'High Speed mode'         | 3.4 MHz                 |

| ISB (1.1)                   | 1.5 MHz or 12 MHz       |

| CSI (parallel bus)          | 40 MHz                  |

| ast SCSI                    | 8-80 MHz                |

| Jitra SCSI-3                | 18-160 MHz              |

| irewire / IEEE1394          | 400 MHz                 |

| i-Speed USB (2.0)           | 480 MHz                 |

Slide 9

Increasing fast serial transmission specifications are shown in Slide 9. Proper treatment of the 480 MHz version of USB - trying to beat the emerging 400 MHz 1394a spec - that is looking to an improved 'b' spec - etc is beyond the scope of this presentation. Philips is developing leading-edge components to support both USB and 1394 buses.

Today the path forward in USB is built on "OTG" (On The Go) applications but the costs and complexity of this are probably beyond the limits of many customers. If designers are identified as designing for large international markets then please contact the USB group for additional support, particularly of Host and OTG solutions. Apologies for inclusion of the parallel SCSI bus. It is intended for comparison purposes and

also because it may be used within the PC software as a general data path that USB drivers can use.

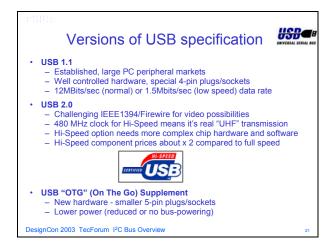

Terminology for USB: The use of older terms such as the spec version 1.1 and 2.0 is now discouraged. There is just "USB" (meaning the original 12 Mbits/sec and 1.5 Mbits/sec speeds of USB version 1.1) and Hi-Speed USB meaning the faster 480 Mbits/sec option included in spec version 2.0. Parts conforming to or capable of the 480 Mbits/sec are certified as Hi-Speed USB and will then feature the logo with the red stripe "Hi-Speed" fitted above the standard USB logo. The reason to avoid use of the new spec version 2.0 as a generic name is that this version includes all the older versions and speeds as well as the new Hi-Speed specs. So USB 2.0 compliance does NOT imply Hi-Speed (480 Mbits/sec). ICs can be compliant with USB 2.0 specifications yet only be capable of the older 'full speed' or 12 Mbits/sec.

Slide 10

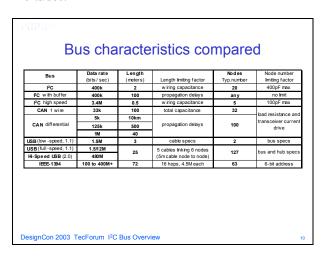

In Slide 10 we look at three important characteristics:

- Speed, or data rate

- Number of devices allowed to be connected (to share the bus wires)

- Total length of the wiring

Numbers are supposed to be realistic estimates but are based on meeting bus specifications. But rules are made to be broken! When buffered, I<sup>2</sup>C can be limited by wiring propagation delays but it is still possible to run much longer distances by using slower clock rates and maybe also compromising the bus rise and fall-time specifications on the buffered bus because it is not bound to conform to I<sup>2</sup>C specifications.

The figure in Slide 10 limiting  $I^2C$  range by propagation delays is conservative and allows for published response delays in chips like older  $E^2$  memories. Measured chip responses are typically < 700 ns and that allows for long cable delays and/or

operation well above 100 kHz with the P82B96. The theoretical round-trip delay on 100 m of cable is only approx 1  $\mu s$  and the maximum allowed delay, assuming zero delays in ICs, is about 3  $\mu s$  at 100 kHz. The figures for CAN are not quite as conservative; they are the 'often quoted values'. The round trip delay in 10 km cable is about 0.1 ms while 5 kbps implies 0.2 ms nominal bit time, and a need to sample during the second half of the bit time. That is under the user's control, but needs attention.

USB 2 and IEEE-1394 are still 'emerging standards'. Figures quoted may not be practical; they are just based on the specification restrictions.

#### **UART Overview**

Slide 11

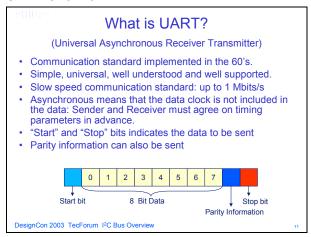

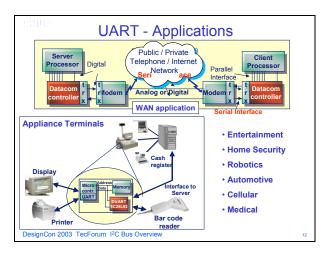

UARTs (Universal Asynchronous Receiver Transmitter) are serial chips on your PC motherboard (or on an internal modem card). The UART function may also be done on a chip that does other things as well. On older computers like many 486's, the chips were on the disk IO controller card. Still older computers have dedicated serial boards.

The UARTs purpose is to convert bytes from the PC's parallel bus to a serial bit-stream. The cable going out of the serial port is serial and has only one wire for each direction of flow. The serial port sends out a stream of bits, one bit at a time. Conversely, the bit stream that enters the serial port via the external cable is converted to parallel bytes that the computer can understand. UARTs deal with data in byte-sized pieces, which is conveniently also the size of ASCII characters.

Say you have a terminal hooked up to your PC. When you type a character, the terminal gives that character to its transmitter (also a UART). The transmitter sends that byte out onto the serial line, one bit at a time, at a specific rate. On the PC end, the receiving UART takes

all the bits and rebuilds the (parallel) byte and puts it in a buffer.

Along with converting between serial and parallel, the UART does some other things as a byproduct (side effect) of its primary task. The voltage used to represent bits is also converted (changed). Extra bits (called start and stop bits) are added to each byte before it is transmitted. Also, while the flow rate (in bytes/s) on the parallel bus speed inside the computer is very high, the flow rate out the UART on the serial port side of it is much lower. The UART has a fixed set of rates (speeds) that it can use at its serial port interface.

Slide 12

#### SPI Overview

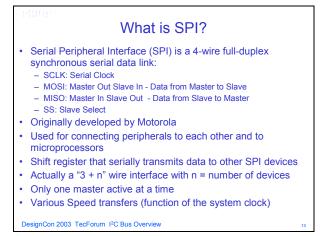

#### Slide 13

The Serial Peripheral Interface (SPI) circuit is a synchronous serial data link that is standard across many Motorola microprocessors and other peripheral chips. It provides support for a high bandwidth (1 mega baud) network connection amongst CPUs and other devices supporting the SPI.

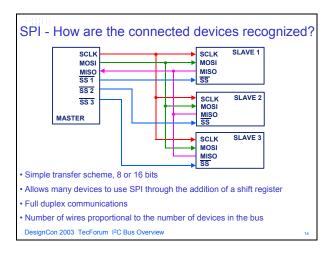

#### Slide 14

The SPI is essentially a "three-wire plus slave selects" serial bus for eight or sixteen bit data transfer applications. The three wires carry information between devices connected to the bus. Each device on the bus acts simultaneously as a transmitter and receiver. Two of the three lines transfer data (one line for each direction) and the third is a serial clock. Some devices may be only transmitters while others only receivers. Generally, a device that transmits usually possesses the capability to receive data also. An SPI display is an example of a receive-only device while EEPROM is a receiver and transmit device.

The devices connected to the SPI bus may be classified as Master or Slave devices. A master device initiates an information transfer on the bus and generates clock and control signals. A slave device is controlled by the master through a slave select (chip enable) line and is active only when selected. Generally, a dedicated select line is required for each slave device. The same device can possess the functionality of a master and a slave but at any point of time, only one master can control the bus in a multi-master mode configuration. Any slave device that is not selected must release (make it high impedance) the slave output line.

The SPI bus employs a simple shift register data transfer scheme: Data is clocked out of and into the active devices in a first-in, first-out fashion. It is in this manner that SPI devices transmit and receive in full duplex mode.

All lines on the SPI bus are unidirectional: The signal on the clock line (SCLK) is generated by the master and is primarily used to synchronize data transfer. The master-out, slave-in (MOSI) line carries data from the master to the slave and the master-in, slave-out (MISO) line carries data from the slave to the master. Each slave device is selected by the master via individual select lines. Information on the SPI bus can be transferred at a rate of near zero bits per second to 1 Mbits per second. Data transfer is usually performed in eight/sixteen bit blocks. All data transfer is

synchronized by the serial clock (SCLK). One bit of data is transferred for each clock cycle. Four clock modes are defined for the SPI bus by the value of the clock polarity and the clock phase bits. The clock polarity determines the level of the clock idle state and the clock phase determines which clock edge places new data on the bus. Any hardware device capable of operation in more than one mode will have some method of selecting the value of these bits.

#### **CAN Overview**

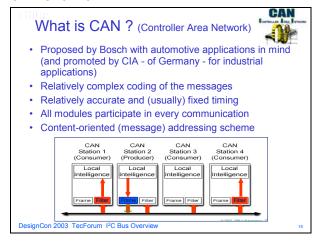

Slide 15

CAN objective is to achieve reliable communications in relatively critical control system applications e.g. engine management or anti-lock brakes. There are several aspects to reliability - availability of the bus when important data needs to be sent, the possibility of bits in a message being corrupted by noise etc., and electrical/mechanical failure modes in the wiring.

At least a ceramic resonator and possibly a quartz crystal are needed to generate the accurate timing needed. The clock and data are combined and 6 'high' bits in succession is interpreted as a bus error. So the clock and bit timings are important. All connected modules must use the same timings. All modules are looking for any error in the data at any point on the wiring and will report that error so the message can be re-sent etc.

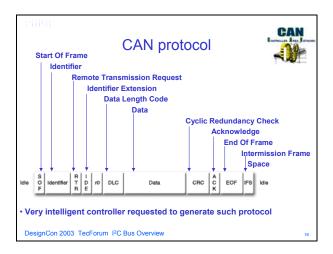

#### Slide 16

Like I<sup>2</sup>C, the CAN bus wires are pulled by resistors to their resting state called a 'recessive' state. When a transceiver drives the bus it forces a voltage called the 'dominant' state. The identifier indicates the meaning of the data, not the intended recipient. So all nodes receive and 'filter' this identifier and can decide whether to act on the data or not. So the bus is using 'multicast' - many modules can act on the message, and all modules are checking the message for transmission errors. Arbitration is 'bit wise' like I<sup>2</sup>C - the module forcing a '1' beats a module trying for a '0' and the loser withdraws to try again later.

- DLC: data length code

- CRC: cyclic redundancy check (remainder of a division calculation). All devices that pass the CRC will acknowledge or will generate an error flag after the data frame finishes.

- ACK: acknowledge.

- Error frame: (at least) 6 consecutive dominant bits then 7 recessive bits.

A message 'filter' can be programmed to test the 11-bit identifier and one or two bytes of the data (In general up to 32 bits) to decide whether to accept the message and issue an interrupt. It could also look at all of the 29-bit identifier.

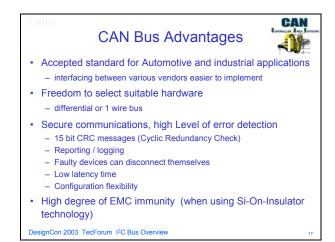

#### Slide 17

I<sup>2</sup>C products from many manufacturers are all compatible but CAN hardware will be selected and dedicated for each particular system design. Some CAN transceivers will be compatible with others, but that is more likely to be the exception than the rule. CAN designs are usually individual systems that are not intended to be modified. Philips parts greatly enhance the feature of reliability by their ability to use part-broken bus wiring and disconnect themselves if they are recording too many bus errors.

There are several aspects to reliability - availability of the bus when important data needs to be sent the possibility of bits in a message being corrupted by noise etc., and the consequences of electrical/mechanical failure modes in the wiring. All these aspects are treated seriously by the CAN specifications and the suppliers of the interface ICs - for example Philips believes conventional high voltage IC processes are not good enough and uses Silicon-on-insulator technology to increase ruggedness and avoid the alternative of using common-mode chokes for protection. To give an example of immunity, a transceiver on 5 V must be able to cope with jump-start and load-dump voltages on its supply or bus wires. That is 40 V on the supply and +/-40 V on the bus lines, plus transients of -150 V/+100 V capacitively coupled from a pulse generator in a test circuit!

#### **USB Overview**

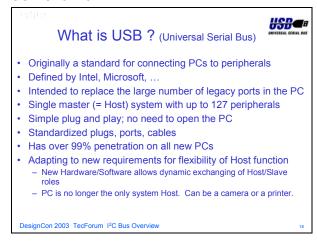

#### Slide 18

USB is the most complex of the buses presented here. While its hardware and transceivers are relatively simple, its software is complex and is able to efficiently service many different applications with very different data rates and requirements. It has a 12 Mbps rate (with 200 Mbps planned) over a twisted pair with a 4-pin connector (2 wires are power supply). It also is limited to short distances of at most 5 meters (depends on configuration). Linux supports the bus, although not all devices that can plug into the bus are supported. It is synchronous and transmits in special packets like a network. Just like a network, it can have several devices attached to it. Each device on it gets a time-slice of exclusive use for a short time. A device can also be guaranteed the use of the bus at fixed intervals. One device can monopolize it if no other device wants to use

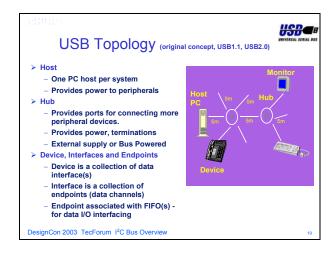

Slide 19

Slide 19 shows a typical USB configuration.

# USB Bus Advantages Hot pluggable, no need to open cabinets Automatic configuration Up to 127 devices can be connected together Push for USB to become THE standard on PCs standard for iMac, supported by Windows, now on > 99% of PCs Interfaces (bridges) to other communication channels exist USB to serial port (serial port vanishing from laptops) USB to IrDA or to Ethernet Extreme volumes force down IC and hardware prices Protocol is evolving fast DesignCon 2003 TecForum I²C Bus Overview 20

#### Slide 20

USB aims at mass-market products and design-ins may be less convenient for small users. The serial port is vanishing from the laptop and gone from iMac. There are hardware bridges available from USB to other communication channels but there can be higher power consumption to go this way. Philips is innovating its USB products to minimize power and offer maximum flexibility in system design.

#### Slide 21

For USB 1.1 and 2.0 the hardware is well established. The shape of the plug/socket at Host end is different from the shape at the peripheral end. USB is always a single point-to-point link over the cable. To allow connection of multiple peripherals a HUB is introduced. The Hub functions to multiplex the data from the 'downstream' peripherals into one 'upstream' data linkage to the Host. In Hi-Speed systems it is necessary for the system to start communicating as a normal USB 1.1 system and then additional hardware (faster transceivers etc) is activated to allow a higher speed. The Hi-Speed system is much more complex (hardware/software) than normal USB (1.1). For USB

and Hi-Speed the development of 'stand-alone' Host ICs such as ISP1161 and ISP1561 allowed the Host function to be embedded in products such as Digital Still Cameras or printers so that more direct transfer of data was possible without using the path Camera  $\rightarrow$  PC  $\rightarrow$  Printer under control of the PC as the host. That two step transfer involves connecting the camera to the PC (one USB cable) and also the PC to the printer (second USB cable). The goal is to do without the PC.

The next step involved the shrinking of the USB connector hardware, to make it more compatible with small products like digital cameras, and making provision (extra pin) for dynamic exchanging of Host and slave device functions without removing the USB cable for reversing the master/slave connectors. The new hardware and USB specification version is called "On The Go" (OTG). The OTG specification no longer requires the Host to provide the 1/2 A power supply to peripherals and indeed allows arbitration to determine whether Host or peripheral (or neither) will provide the system power.

#### 1394 Overview

#### What is IEEE1394?

- A bus standard devised to handle the high data throughput requirements of MPEG-2 and DVD

- Video requires constant transfer rates with guaranteed bandwidth

- Data rates 100, 200, 400 Mbits/sec and looking to 3.2 Gb/s

- Also known as "Firewire" bus (registered trademark of Apple)

- Automatically re-configures itself as each device is added

True plug & play

- Hot-plugging of devices allowed

- Up to 63 devices, 4.5 m cable 'hops', with max. 16 hops

- · Bandwidth guaranteed

DesignCon 2003 TecForum I<sup>2</sup>C Bus Overview

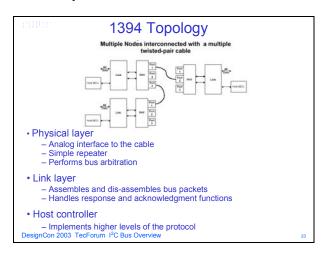

#### Slide 22

1394 may claim to be more proven or established than USB but both are 'emerging' specifications that are trying to out-do each other! Philips strongly supports BOTH. 1394 was chosen by Philips as the bus to link set-top boxes, DVD, and digital TVs. 1394 has an 'a' version taking it to 400 Mb/sec and more recently a 'b' version for higher speed and to allow longer cable runs, perhaps 100 meter hops!

1394 sends information over a PAIR of twisted pairs. One for data, the other is the clocking strobe. The clock is simply recovered by an Ex-Or of the data and strobe line signals. No PLL is needed. There is provision for lots of remote device powering via the cable if the 6-pin plug connection version is used. The power wires are

specified to well over 1A at 8-30 volts (approx) - leading to some unkind references to a 'fire' wire!

1394 software or message format consists of timeslots within which the data is sent in blocks or 'channels'. For real-time data transfer it is possible to guarantee the availability of one or more channels to guarantee a certain data rate. This is important for video because it's no good sending a packet of corrected data after a blank has appeared on the screen!

Microsoft says, "IEEE 1394 defines a single interconnection bus that serves many purposes and user scenarios. In addition to its adoption by the consumer electronics industry, PC vendors—including Compaq, Dell, IBM, Fujitsu, Toshiba, Sony, NEC, and Gateway—are now shipping Windows-based PCs with 1394 buses.

The IEEE 1394 bus complements the Universal Serial Bus (USB) and is particularly optimized for connecting digital media devices and high-speed storage devices to a PC. It is a peer-to-peer bus. Devices have more built-in intelligence than USB devices, and they run independently of the processor, resulting in better performance.

The 100-, 200-, and 400-Mbps transfer rates currently specified in the IEEE 1394a standard and the proposed enhancements in 1394b are well suited to meeting the throughput requirements of multiple streaming input/output devices connected to a single PC. The licensing fee for use of patented IEEE 1394 technology has been established at US \$0.25 per system.

With connectivity for storage, scanners, printers, and other types of consumer A/V devices, IEEE 1394 gives users all the benefits of a great legacy-free connector—a true Plug and Play experience and hassle-free PC connectivity."

Slide 23

#### I<sup>2</sup>C Overview

#### What is I<sup>2</sup>C? (Inter-IC)

- Originally, bus defined by Philips providing a simple way to talk between IC's by using a minimum number of pins

- A set of specifications to build a simple universal bus guaranteeing compatibility of parts (ICs) from different manufacturers:

- Simple Hardware standards

- Simple Software protocol standard

- No specific wiring or connectors most often it's just PCB tracks

- Has become a recognised standard throughout our industry and is used now by ALL major IC manufacturers

DesignCon 2003 TecForum I2C Bus Overview

#### Slide 24

Originally, the I<sup>2</sup>C bus was designed to link a small number of devices on a single card, such as to manage the tuning of a car radio or TV. The maximum allowable capacitance was set at 400 pF to allow proper rise and fall times for optimum clock and data signal integrity with a top speed of 100 kbps. In 1992 the standard bus speed was increased to 400 kbps, to keep up with the ever-increasing performance requirements of new ICs. The 1998 I<sup>2</sup>C specification, increased top speed to 3.4 Mbits/sec. All I<sup>2</sup>C devices are designed to be able to communicate together on the same two-wire bus and system functional architecture is limited only by the imagination of the designer.

But while its application to bus lengths within the confines of consumer products such as PCs, cellular phones, car radios or TV sets grew quickly, only a few system integrators were using it to span a room or a building. The I<sup>2</sup>C bus is now being increasingly used in multiple card systems, such as a blade servers, where the I<sup>2</sup>C bus to each card needs to be isolatable to allow for card insertion and removal while the rest of the system is in operation, or in systems where many more devices need to be located onto the same card, where the total device and trace capacitance would have exceeded 400 pF.

New bus extension & control devices help expand the I<sup>2</sup>C bus beyond the 400 pF limit of about 20 devices and allow control of more devices, even those with the same address. These new devices are popular with designers as they continue to expand and increase the range of use of I<sup>2</sup>C devices in maintenance and control applications.

#### I<sup>2</sup>C Features

• Only two bus lines are required: a serial data line (SDA) and a serial clock line (SCL).

- Each device connected to the bus is software addressable by a unique address and simple master/slave relationships exist at all times; masters can operate as master-transmitters or as master-receivers.

- It's a true multi-master bus including collision detection and arbitration to prevent data corruption if two or more masters simultaneously initiate data transfer

- Serial, 8-bit oriented, bi-directional data transfers can be made at up to 100 kbit/s in the Standardmode, up to 400 kbit/s in the Fast-mode, or up to 3.4 Mbit/s in the High-speed mode.

- On-chip filtering (50 ns) rejects spikes on the bus data line to preserve data integrity.

- The number of ICs that can be connected to the same bus segment is limited only by the maximum bus capacitive loading of 400 pF.

#### I<sup>2</sup>C Bus - Software

- Simple procedures that allow communication to start, to achieve data transfer, and to stop

- Described in the Philips protocol (rules)

- Message serial data format is very simple

- Often generated by simple software in general purpose micro

- Dedicated peripheral devices contain a complete interface

- Multi-master capable with arbitration feature

- Each IC on the bus is identified by its own address code

Address has to be unique

- The master IC that initiates communication provides the clock signal (SCI.)

- There is a maximum clock frequency but NO MINIMUM SPEED.

DesignCon 2003 TecForum I<sup>2</sup>C Bus Overview

#### Slide 25

#### I<sup>2</sup>C Communication Procedure

One IC that wants to talk to another must:

- 1) Wait until it sees no activity on the I<sup>2</sup>C bus. SDA and SCL are both high. The bus is 'free'.

- 2) Put a message on the bus that says 'its mine' I have STARTED to use the bus. All other ICs then LISTEN to the bus data to see whether they might be the one who will be called up (addressed).

- 3) Provide on the CLOCK (SCL) wire a clock signal. It will be used by all the ICs as the reference time at which each bit of DATA on the data (SDA) wire will be correct (valid) and can be used. The data on the data wire (SDA) must be valid at the time the clock wire (SCL) switches from 'low' to 'high' voltage.

- 4) Put out in serial form the unique binary 'address' (name) of the IC that it wants to communicate with

- 5) Put a message (one bit) on the bus telling whether it wants to SEND or RECEIVE data from the other chip. (The read/write wire is gone!)

- Ask the other IC to ACKNOWLEDGE (using one bit) that it recognized its address and is ready to communicate.

- 7) After the other IC acknowledges all is OK, data can be transferred.

- 8) The first IC sends or receives as many 8-bit words of data as it wants. After every 8-bit data word the sending IC expects the receiving IC to acknowledge the transfer is going OK.

- 9) When all the data is finished the first chip must free up the bus and it does that by a special message called 'STOP'. It is just one bit of information transferred by a special 'wiggling' of the SDA/SCL wires of the bus.

The bus rules say that when data or addresses are being sent, the DATA wire is only allowed to be changed in voltage (so, '1', '0') when the voltage on the clock line is LOW. The 'start' and 'stop' special messages BREAK that rule, and that is how they are recognized as special.

# How are the connected devices recognized?

- Master device 'polls' used a specific unique identification or "addresses" that the designer has included in the system

- Devices with Master capability can identify themselves to other specific Master devices and advise their own specific address and functionality

- Allows designers to build 'plug and play' systems

- Bus speed can be different for each device, only a maximum limit

- · Only two devices exchange data during one 'conversation'

DesignCon 2003 TecForum I<sup>2</sup>C Bus Overview

#### Slide 26

Any device with the ability to initiate messages is called a 'master'. It might know exactly what other chips are connected, in which case it simply addresses the one it wants, or there might be optional chips and it then checks what's there by sending each address and seeing whether it gets any response (acknowledge).

An example might be a telephone with a micro in it. In some models, there could be EEPROM to guarantee memory data, in some models there might be an LCD display using an I<sup>2</sup>C driver. There can be software written to cover all possibilities. If the micro finds a display then it drives it, otherwise the program is arranged to skip that software code. I<sup>2</sup>C is the simplest of the buses in this presentation. Only two chips are involved in any one communication - the Master that initiates the signals and the one Slave that responded when addressed.

But several Masters could control one Slave, at different times. Any 'smart' communications must be via the transferred DATA, perhaps used as address info. The I<sup>2</sup>C bus protocol does not allow for very complex systems. It's a 'keep it simple' bus. But of course system designers are free to innovate to provide the complex systems - based on the simple bus.

#### Serial Bus Comparison Summary

| UART                                     | CAN                                                                          | USB                                                                               | SPI                                                        | I <sup>2</sup> C                                                                                   |

|------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Well Known     Cost effective     Simple | • Secure<br>• Fast                                                           | Fast     Plug&Play HW     Simple     Low cost                                     | • Fast • Universally accepted • Low cost • Large Portfolio | Simple     Well known     Universally accepted     Plug&Play     Large portfoli     Cost effective |

| Limited functionality     Point to Point | Complex     Automotive oriented     Limited portfolio     Expensive firmware | Powerful master<br>required     No Plug&Play<br>SW - Specific<br>drivers required | No Plug&Play<br>HW     No "fixed"<br>standard              | Limited speed                                                                                      |

Slide 27

Most Philips CAN devices are not plug & play. That is because for MOST chips the system needs to be fixed and nothing can be added later. That is because an added chip is EXPECTED to take part in EVERY data conversation but will not know the clock speed and cannot synchronize. That means it falsely reports a bus timing error on every message and crashes the system.

Philips has special transceivers that allow them listen to the bus without taking part in the conversations. This special feature allows them to synchronize their clocks and THEN actively join in the conversations. So, from Philips, it becomes POSSIBLE to do some minor plug/play on a CAN system.

USB/SPI/MicroWire and mostly UARTS are all just 'one point to one point' data transfer bus systems. USB then uses multiplexing of the data path and forwarding of messages to service multiple devices.

Only CAN and I<sup>2</sup>C use SOFTWARE addressing to determine the participants in a transfer of data between two (I<sup>2</sup>C) or more (CAN) chips all connected to the same bus wires. I<sup>2</sup>C is the best bus for low speed maintenance and control applications where devices may have to be added or removed from the system.

#### I<sup>2</sup>C Theory Of Operation

#### I<sup>2</sup>C Introduction

- I2C bus = Inter-IC bus

- Bus developed by Philips in the 80's

- · Simple bi-directional 2-wire bus:

- serial data (SDA)

- serial clock (SCL)

- Has become a worldwide industry standard and used by all major IC manufacturers

- · Multi-master capable bus with arbitration feature

- Master-Slave communication; Two-device only communication

- · Each IC on the bus is identified by its own address code

- The slave can be a:

- receiver-only device

- transmitter with the capability to both receive and send data

DesignCon 2003 TecForum I2C Bus Overview

#### Slide 29

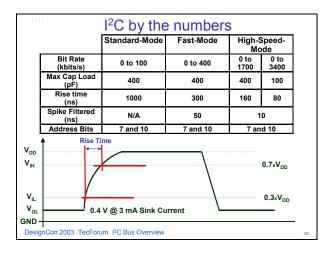

The  $I^2C$  bus is a very easy bus to understand and use. Slides 29 and 30 give a good explanation of bus specifics and the different speeds. Many people have asked where rise time is measured and the specification stipulates it's between 30% and 70% of  $V_{DD}$ . This becomes important when buffers 'distort' the rising edges on the bus. By keeping any waveform distortions below 30% of  $V_{DD}$ , that portion of the rising edge will not be counted as part of the formal rise time.

Slide 30

I<sup>2</sup>C is a low to medium speed serial bus with an impressive list of features:

- Resistant to glitches and noise

- Supported by a large and diverse range of peripheral devices

- A well-known robust protocol

- A long track record in the field

- A respectable communication distance which can be extended to longer distances with bus extenders

- Compatible with a number of processors with integrated I<sup>2</sup>C ports (micro 8,16,32 bits) in 8048, 80C51 or 6800 and 68xxx architectures

- Easily emulated in software by any microcontroller

- Available from an important number of component manufacturers

Slide 31

#### I<sup>2</sup>C Bus Terminology

- Transmitter the device that sends data to the bus. A transmitter can either be a device that puts data on the bus of its own accord (a 'master-transmitter'), or in response to a request from data from another devices (a 'slave-transmitter').

- Receiver the device that receives data from the bus.

- Master the component that initializes a transfer, generates the clock signal, and terminates the transfer. A master can be either a transmitter or a receiver.

- Slave the device addressed by the master. A slave can be either receiver or transmitter.

- **Multi-master** the ability for more than one master to co-exist on the bus at the same time without collision or data loss.

- Arbitration the prearranged procedure that authorizes only one master at a time to take control of the bus.

- Synchronization the prearranged procedure that synchronizes the clock signals provided by two or more masters.

- SDA data signal line (Serial DAta)

- SCL clock signal line (Serial CLock)

Slide 32

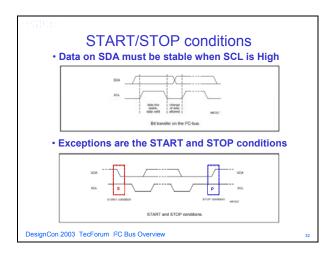

#### START and STOP Conditions

Within the procedure of the I<sup>2</sup>C bus, unique situations arise which are defined as START (S) and STOP (P) conditions.

START: A HIGH to LOW transition on the SDA line while SCL is HIGH

STOP: A LOW to HIGH transition on the SDA line while SCL is HIGH

The master always generates START and STOP conditions. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical. The S symbol will be used as a generic term to represent both the START and repeated START conditions, unless Sr is particularly relevant.

Detection of START and STOP conditions by devices connected to the bus is easy if they incorporate the necessary interfacing hardware. However, microcontrollers with no such interface have to sample the SDA line at least twice per clock period to sense the transition.

Slide 33

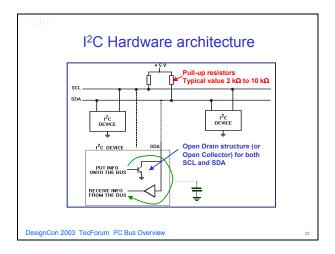

#### HARDWARE CONFIGURATION

Slide 33 shows the hardware configuration of the I<sup>2</sup>C bus. The 'bus' wires are named SDA (serial data) and SCL (serial clock). These two bus wires have the same configuration. They are pulled-up to the logic 'high' level by resistors connected to a single positive supply, usually +3.3 V or +5 V but designers are now moving to +2.5 V and towards 1.8 V in the near future.

All the connected devices have open-collector (open-drain for CMOS - both terms mean only the lower transistor is included) driver stages that can transmit data by pulling the bus low, and high impedance sense amplifiers that monitor the bus voltage to receive data. Unless devices are communicating by turning on the lower transistor to pull the bus low, both bus lines remain 'high'. To initiate communication a chip pulls the SDA line low. It then has the responsibility to drive the SCL line with clock pulses, until it has finished, and is called the bus 'master'.

#### **BUS COMMUNICATION**

Communication is established and 8-bit bytes are exchanged, each one being acknowledged using a 9th data bit generated by the receiving party, until the data transfer is complete. The bus is made free for use by other ICs when the 'master' releases the SDA line during a time when SCL is high. Apart from the two special exceptions of start and stop, no device is allowed to change the state of the SDA bus line unless the SCL line is low.

If two masters try to start a communication at the same time, arbitration is performed to determine a "winner" (the master that keeps control of the bus and continue the transmission) and a "loser" (the master that must abort its transmission). The two masters can even generate a few cycles of the clock and data that 'match', but eventually one will output a 'low' when the other tries for a 'high'. The 'low' wins, so the

'loser' device withdraws and waits until the bus is freed again.

There is no minimum clock speed; in fact any device that has problems to 'keep up the pace' is allowed to 'complain' by holding the clock line low. Because the device generating the clock is also monitoring the voltage on the SCL bus, it immediately 'knows' there is a problem and has to wait until the device releases the SCL line.

For full details of the bus capabilities refer to Philips Semiconductors Specification document 'The I<sup>2</sup>C bus specification' or 'The I<sup>2</sup>C bus from theory to practice' book by Paret and Fenger published by John Wiley & Sons.

The I<sup>2</sup>C specification and other useful application information can be found on Philips Semiconductors web site at

http://www.semiconductors.philips.com/i2c/

Slide 34

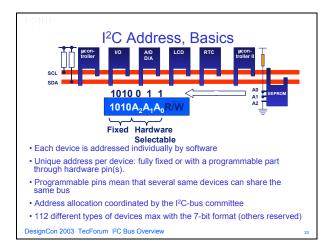

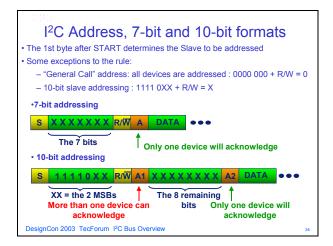

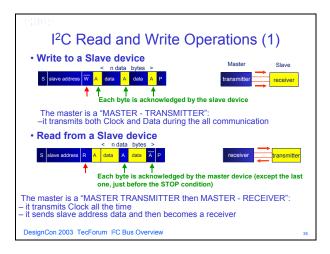

Slide 34 shows the I<sup>2</sup>C address scheme. Any I<sup>2</sup>C device can be attached to the common I<sup>2</sup>C bus and they talk with each other, passing information back and forth. Each device has a unique 7-bit or 10-bit I<sup>2</sup>C address. For 7-bit devices, typically the first four bits are fixed, the next three bits are set by hardware address pins (A0, A1, and A2) that allow the user to modify the I<sup>2</sup>C address allowing up to eight of the same devices to operate on the I<sup>2</sup>C bus. These pins are held high to V<sub>CC</sub>, sometimes through a resistor, or held low to GND.

The last bit of the initial byte indicates if the master is going to send (write) or receive (read) data from the slave. Each transmission sequence must begin with the start condition and end with the stop condition.

On the 8th clock pulse, SDA is set 'high' if data is going to be read from the other device, or 'low' if data is going to be sent (write). During its 9th clock, the

master releases SDA line to accomplish the Acknowledge phase. If the other device is connected to the bus, and has decoded and recognized its 'address', it will acknowledge by pulling the SDA line low. The responding chip is called the bus 'slave'.

Slide 35

#### Terminology for Bus Transfer

- **F** (**FREE**) the bus is free; the data line SDA and the SCL clock are both in the high state.

- S (START) or S<sub>R</sub> (Repeated START) data transfer begins with a start condition (not a start bit). The level of the SDA data line changes from high to low, while the SCL clock line remains high. When this occurs, the bus is 'busy'.

- C (CHANGE) while the SCL clock line is low, the data bit to be transferred can be applied to the SDA data line by a transmitter. During this time, SDA may change its state, as along as the SCL line remains low.

- D (DATA) a high or low bit of information on the SDA data line is valid during the high level of the SCL clock line. This level must be maintained stable during the entire time that the clock remains high to avoid misinterpretation as a Start or Stop condition.

- **P** (STOP) data transfer is terminated by a stop condition, (not a stop bit). This occurs when the level on the SDA data line passes from the low state to the high state, while the SCL clock line remains high. When the data transfer has been terminated, the bus is free once again.

Slide 36

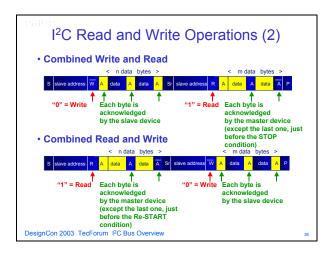

Slide 36 shows a combined read and write operation.

Slide 37

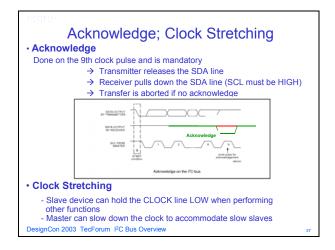

Slide 37 shows how the Acknowledge phase is done and how slave devices can stretch the clock signal. Most Philips slave devices do not control the clock line.

Slide 38

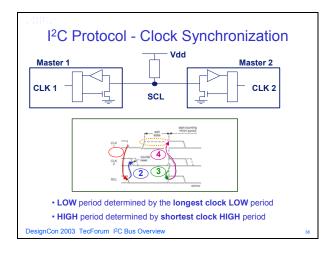

Slide 38 shows how multiple masters can synchronize their clocks, for example during arbitration. When bus capacitance affects the bus rise or fall times the master will also adjust its timing in a similar way.

Slide 39

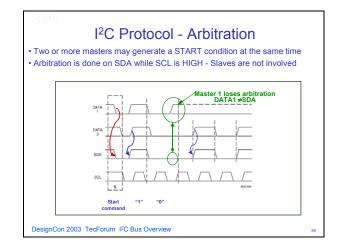

If there are two masters on the same bus, there are arbitration procedures applied if both try to take control of the bus at the same time. When two chips try to start communication at the same time they may even generate a few cycles of the clock and data that 'match', but eventually one will output a 'low' when the other tries for a 'high'. The 'low' wins, so the 'loser' device withdraws and waits until the bus is freed again. Once a master (e.g., microcontroller) has control, no other master can take control until the first master sends a stop condition and places the bus in an idle state.

Slide 40

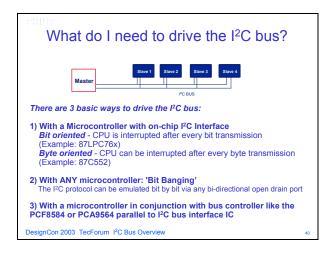

Slide 40 shows there are multiple ways to control I<sup>2</sup>C slaves.

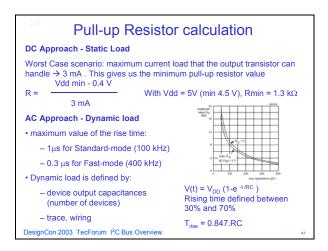

#### Slide 41

Slide 41 shows the typical resistor values needed for proper operation. C is the total capacitance on either SDA or SCL bus wire, with R as its pull-up resistor.

#### I<sup>2</sup>C Designer Benefits

- Functional blocks on the block diagram correspond with the actual ICs; designs proceed rapidly from block diagram to final schematic.

- No need to design bus interfaces because the I<sup>2</sup>C bus interface is already integrated on-chip.

- Integrated addressing and data-transfer protocol allow systems to be completely software-defined.

- The same IC types can often be used in many different applications.

- Design-time reduces as designers quickly become familiar with the frequently used functional blocks represented by I<sup>2</sup>C bus compatible ICs.

- ICs can be added to or removed from a system without affecting any other circuits on the bus.

- Fault diagnosis and debugging are simple; malfunctions can be immediately traced.

- Assembling a library of reusable software modules can reduce software development time.

#### I<sup>2</sup>C Manufacturers Benefits

- The simple 2-wire serial I<sup>2</sup>C bus minimizes interconnections so ICs have fewer pins and there are not so many PCB tracks; result smaller and less expensive PCBs

- The completely integrated I<sup>2</sup>C bus protocol eliminates the need for address decoders and other 'glue logic'

- The multi-master capability of the I<sup>2</sup>C bus allows rapid testing/alignment of end-user equipment via external connections to an assembly-line

- Increases system design flexibility by allowing simple construction of equipment variants and easy upgrading to keep design up-to-date

• The I<sup>2</sup>C bus is a de facto world standard that is implemented in over 1000 different ICs (Philips has > 400) and licensed to more than 70 companies

| I <sup>2</sup> C Bus recovery                                                                                          |

|------------------------------------------------------------------------------------------------------------------------|

| Typical case is when masters fails when doing a read operation in a slave                                              |

| SDA line is then non usable anymore because of the "Slave-Transmitter" mode.                                           |

| Methods to recover the SDA line are:                                                                                   |

| <ul> <li>Reset the slave device (assuming the device has a Reset pin)</li> </ul>                                       |

| <ul> <li>Use a bus recovery sequence to leave the "Slave-Transmitter" mode</li> </ul>                                  |

| Bus recovery sequence is done as following:     1 - Send 9 clock pulses on SCL line                                    |

| Ask the master to keep SDA High until the "Slave-Transmitter" releases the SDA line to perform the ACK operation       |

| 3 - Keeping SDA High during the ACK means that the "Master-Receiver"<br>does not acknowledge the previous byte receive |

| 4 - The "Slave-Transmitter" then goes in an idle state                                                                 |

| 5 - The master then sends a STOP command initializing completely the bus                                               |

| DesignCon 2003 TecForum I <sup>2</sup> C Bus Overview 42                                                               |

#### Slide 42

Slide 42 shows how a hung bus could be recovered. The bus can become hung for several reasons, e.g.....

- Incorrect power-up and/or reset procedure for ICs

- 2. Power to a chip is interrupted brown-outs etc

- 3. Noise on the wiring causes false clock or data signals

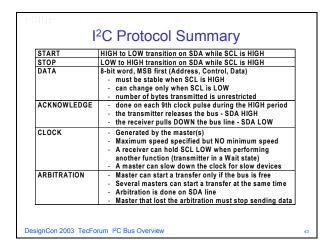

Slide 43

Slide 43 provides a summary of the I<sup>2</sup>C protocol.

#### I<sup>2</sup>C Summary - Advantages

- · Simple Hardware standard

- · Simple protocol standard

- Easy to add / remove functions or devices (hardware and software)

- Easy to upgrade applications

- Simpler PCB: Only 2 traces required to communicate between devices

- Very convenient for monitoring applications

- Fast enough for all "Human Interfaces" applications

- Displays, Switches, Keyboards

- Control, Alarm systems

- Large number of different I<sup>2</sup>C devices in the semiconductors business

- Well known and robust bus

DesignCon 2003 TecForum I<sup>2</sup>C Bus Overview

#### Slide 44

Slide 44 summarizes the advantages of the I<sup>2</sup>C bus.

#### **Overcoming Previous Limitations**

#### **Address Conflicts**

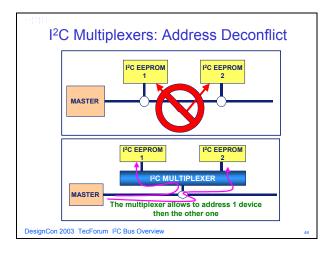

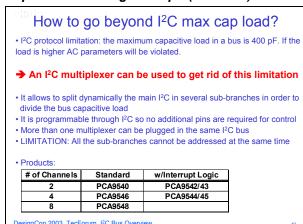

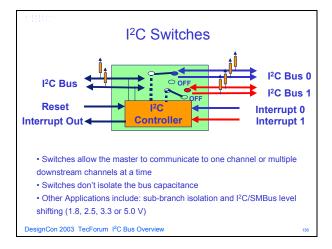

# How to solve I²C address conflicts? • I²C protocol limitation: when a device does not have its I²C address programmable (fixed), only one same device can be plugged in the same bus • An I²C multiplexer can be used to get rid of this limitation • It allows to split dynamically the main I²C in several sub-branches in order to talk to one device at a time • It is programmable through I²C so no additional pins are required for control • More than one multiplexer can be plugged in the same I²C bus • Products # of Channels Standard w/Interrupt Logic 2 PCA9540 PCA9542/43 4 PCA9546 PCA9544/45 8 PCA9548 • PCA9540 PCA9544/45 • PCA9540 PCA9544/45

#### Slide 47

A 7 or 10-bit address that is unique to each device identifies an I<sup>2</sup>C device.

This address can be:

- Partly fixed, part programmable (allowing to have more than one of the same device on the same bus)

- Fully fixed allowing to have only one single same device on the device.

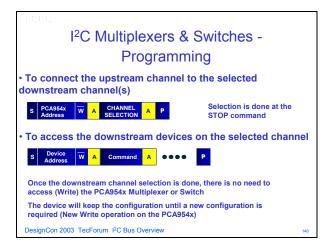

If more than one same "non programmable" device (fully fixed address) is required in a specific application, it is then necessary to temporarily remove the non-addressed device(s) from the bus when talking with the targeted device. I<sup>2</sup>C multiplexers allow to dynamically split the main I<sup>2</sup>C bus into 2, 4 or 8 sub-I<sup>2</sup>C buses. Each sub-bus (downstream channel) can be connected to the main bus (upstream channel) by a simple 2-byte I<sup>2</sup>C command.

For example, in an application where 4 identical I<sup>2</sup>C EEPROMs are used (EE1, EE2, EE3 and EE4), a four channel PCA9546 can be used. The master is plugged to the main upstream bus while the 4 EEPROMs are plugged to the 4 downstream channels (CH1, CH2, CH3 and CH4). If the master needs to perform an operation on EE3, it will have to:

- Connect the upstream channel to CH3

- Simply communicate with EE3.

EE1, EE2 and EE4 are electrically removed from the main I<sup>2</sup>C bus as long as CH3 is selected. Some of the I<sup>2</sup>C multiplexers offer an Interrupt feature, allowing collection of the different downstream Interrupts (generated by the downstream devices). An Interrupt output provides the information (transition from High to Low) to the master every time one or more Interrupt is generated (transition from High to Low) by any of the downstream devices.

Slide 48

The SCL/SDA upstream channel fans out to multiple SCx/SDx channels that are selected by the programmable control register. The I<sup>2</sup>C command is sent via the main I<sup>2</sup>C bus and is used to select or deselect the downstream channels.

The Multiplexers can select none or only one SCx/SDx channels at a time since they were designed primarily for address conflict resolution such as when multiple devices with the same I<sup>2</sup>C address need to be attached to the same I<sup>2</sup>C bus and you can only talk to one of the devices at a time.

These devices are used in video projectors and server applications. Other applications include:

- Address conflict resolution (e.g., SPD EEPROMs on DIMMs).

- I<sup>2</sup>C sub-branch isolation

• I<sup>2</sup>C bus level shifting (e.g., each individual SCx/SDx channel can be operated at 1.8 V, 2.5 V, 3.3 V or 5.0 V if the device is powered at 2.5 V).

Interrupt logic inputs for each channel and a combined output are included on every multiplexer and provide a flag to the master for system monitoring. These devices do not isolate the capacitive loading on either side of the device so the designer must take into account all trace and device capacitance on both sides of the device and on any active channels. Pull up resistors must be used on all channels

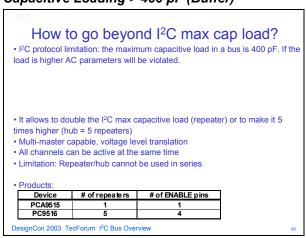

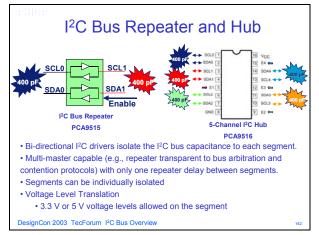

#### Capacitive Loading > 400 pF (isolation)

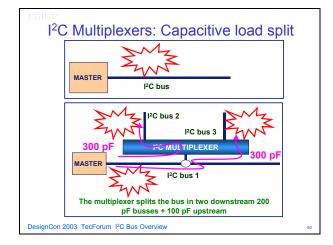

Slide 49

The I<sup>2</sup>C specification limits the maximum capacitive load in the bus to 400 pF. In applications where a higher capacitive load is required, 2 types of devices can be used:

- I<sup>2</sup>C multiplexers and switches

- I<sup>2</sup>C buffers and repeaters

Slide 50

Multiplexers allow dynamic splitting of the overloaded I<sup>2</sup>C bus into several sub-branches with a total capacitive load smaller than the specified 400 pF. Note that this method does not allow the master to access all the buses at the same time. Only part of the bus will be accessible at a time.

Multiplexers allow bus splitting but do not have a buffering capability. Buffers and repeaters allow increasing the total capacitive load beyond the 400 pF without splitting the bus in several branches. If a PCA9515 is used, the bus can be loaded up to 800 pF with 400 pF on each side of the device.

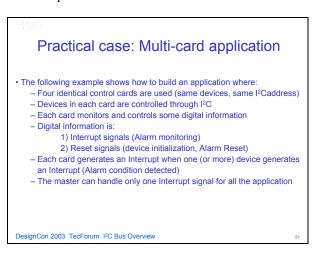

#### Slide 51

In this application, 4 identical cards are used. Identical means that the same devices are used, and that the I<sup>2</sup>C devices on each card have the same address. Each card monitors and controls some specific signal and those signals are controlled/monitored through the I<sup>2</sup>C bus by using a PCA9554 type device.

In this application, each card monitors some alarm system's sub system and controls some LEDs for visual status. Each alarm, when triggered, generates an Interrupt that is sent to the master for processing. PCA9554 collects the Interrupt signals and sends a "Card General Interrupt" to the master. When the master processes the alarm, it sends a Reset signal to the corresponding alarm to clear it. Master receives only an Interrupt signal, which is a combination of all the Interrupt signals in the cards. Since the cards are identical, it is then necessary to deconflict the different addresses and isolate the cards that are not accessed.

PCA9544 in this application has 2 functions:

- Deconflict the I<sup>2</sup>C addresses by creating 4 sub I<sup>2</sup>C busses that can be isolated

- Collect the Interrupt from each card and propagate a "General Interrupt" to the master

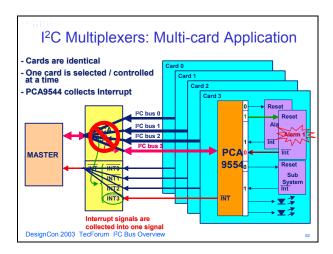

Slide 52

When one card in the application triggers an alarm condition, the PCA9554 collects it through one of its inputs and generates an Interrupt (at the card level). PCA9544 collects the Interrupts (from each card) and sends a "General Interrupt" to the master.

- Master then interrogates the PCA9544 Interrupt status register in order to determine which card is

- 2. Master then connects the corresponding sub I<sup>2</sup>C channel in order to interrogate the PCA9554 by reading its Input register.

- 3. Once 1) and 2) are done, Master knows which alarm has been triggered and can process it

When this is done, Master can then clear the corresponding alarm by accessing the corresponding card and programming the PCA9554 (write in the output register)

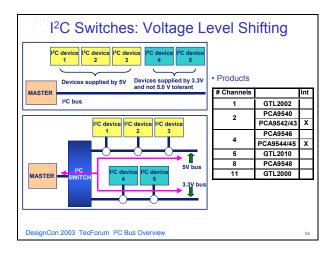

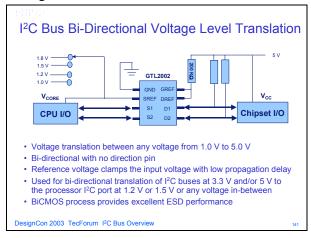

#### Voltage Level Translation

#### How to accommodate different I<sup>2</sup>C logic levels in the same bus?

- $\bullet$  I<sup>2</sup>C protocol: Due to the open drain structure of the bus, voltage level in the bus is fixed by the voltage connected to the pull-up resistor. If different voltage levels are required (e.g., master core at 1.8 V, legacy I2C bus at 5 V and new devices at 3.3 V), voltage level translators need to be used

- It allows to split dynamically the main I2C in several sub-branches and allow different supply voltages to be connected to the pull up resistors

- PCA devices are programmable through I2C bus so no additional pin is required to control which channel is active

- More than one channel can be active at the same time so the master does not have to remember which branch it has to address (broadcast)

- More than one switch can be plugged in the same I2C bus DesignCon 2003 TecForum I2C Bus Overview

#### Slide 53

Due to the open drain architecture of the I<sup>2</sup>C bus, pull up resistors to a specific voltage is required. Once this is done, all the devices in the bus will have the same high level voltage value, determined by the voltage applied to the pull up resistors. In applications where several voltage levels are required (e.g. accommodate legacy architecture at 5.0 V with newer devices working at 3.3 V only), I<sup>2</sup>C switches allow creating a bus with different high level voltage values at a minimum cost.

In this example, we have an existing 5.0 V I<sup>2</sup>C bus and we want to add some new features with devices "non 5.0 V tolerant". An I<sup>2</sup>C bus can be used. The master controlling the existing and new devices will be located in the upstream channel and the 2 downstream channels will be used with pull up resistors at 5.0 V in one and to 3.3 V in the other one. Software changes will include the drivers for the new 3.3 V devices and a simple 2byte command allows to program the I<sup>2</sup>C switch with the 2 downstream channels active all the time. The master then sees an I<sup>2</sup>C bus with new devices and does not have to take care of the high level voltage required to make them work correctly. It does not have to care either about the location of the device it needs to talk to (downstream channel 0 or channel 1) since both are active at the same time.

Slide 54

The SCL/SDA upstream channel fans out to multiple SCx/SDx channels that are selected by the programmable control register. The Switches can select individual SCx/SDx channels one at a time, all at once or in any combination through I<sup>2</sup>C commands and very primary designed for sub-branch isolation and level shifting but also work fine for address conflict resolution. Just make sure you do not select two channels at the same time.

Applications are the same as for the multiplexers but since multiple channels can be selected at the same time the switches are really great for I<sup>2</sup>C bus level shifting (e.g., individual SCx/SDx channels at 1.8 V, 2.5 V, 3.3 V or 5.0 V if the device is powered at 2.5 V). A

hardware reset pin has been added to all the switches. It provides a means of resetting the bus should it hang up, without rebooting the entire system and is very useful in server applications where it is impractical to reset the entire system when the I<sup>2</sup>C bus hangs up. The switches reset to no channels selected.

Interrupt logic inputs and output are available on the PCA9543 and PCA9545 and provide a flag to the master for system monitoring. The PCA9546 is a lower cost version of the PCA9545 without Interrupt Logic. The PCA9548 provides eight channels and are more convenient to use then dual 4 channel devices since the device address does not have to shift.

These devices do not isolate the capacitive loading on either side of the device so the designer must take into account all trace and device capacitance on both sides of the device (active channels only). Pull up resistors must be used on all channels.

#### Increase I<sup>2</sup>C Bus Reliability (Slave Devices)

# How to increase reliability of an I<sup>2</sup>C bus? (Slave devices)

- I<sup>2</sup>C protocol: If one device does not work properly and hangs the bus, then

no device can be addressed anymore until the rogue device is separated from

the bus or reset.

- → An I<sup>2</sup>C switch can be used to split the I<sup>2</sup>C bus in several branches that can be isolated if the bus hangs up.

- Switches allow the main I<sup>2</sup>C to be split dynamically in several sub-branches

- active all the time

that can be:

- deactivated if one device of a particular branch hangs the bus

- When a malfunctioning sub-branch has been isolated, the other sub branches are still available

- It is programmable through I2C so no additional pin is required to control it

- More than one switch can be plugged in the same I<sup>2</sup>C bus

DesignCon 2003 TecForum I<sup>2</sup>C Bus Overview

#### Slide 55

Due to the open drain architecture of the I<sup>2</sup>C bus, if a device fails in the bus and keeps the clock or data line at a high or low level, the bus is stuck in this configuration and no device can be controlled until the failed device is isolated from the I<sup>2</sup>C bus. Some architectures require a bus to still be operational even though one or more devices failed and can no longer operate normally.

An I<sup>2</sup>C switch with a Reset capability allows to:

- Split dynamically the I<sup>2</sup>C bus in several subbranches (with one or several devices on each)

- Disconnect all the devices in case the bus hangs

- Reprogram the bus and isolate one or more branch that is not working properly.

Slide 56

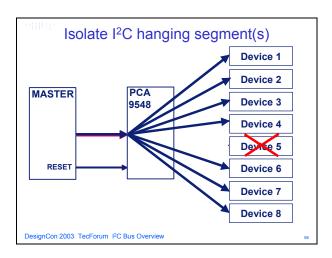

Let's take an example where 8 devices (DEV1 to DEV8) are used and where the functional devices need to be controlled even though one or more devices are failing.

Slave devices will be located on each downstream channel of the PCA9548 (8-channel switch with Reset) (CH1 to CH8). At power up, all the downstream channels are disabled. The master (located in the upstream channel) sends a 2 byte command enabling all the downstream channels. The I<sup>2</sup>C bus is then a normal bus with a master and 8 slave devices. Let's assume that DEV4 (in CH4) fails. The bus then hangs and cannot be normally controlled by the master anymore.

After detection of this condition, the master must go to a maintenance routine where:

- It resets the PCA9548, thus disabling all the downstream channels.

- It enables one by one all the downstream channels (CH1 to CH8) until the bus hangs again (CH4 active).

The master then knows that the device connected to CH4 is responsible of the failure

- It resets again the PCA9548 to take control of the I<sup>2</sup>C bus

- It programs all the functional channels active (CH1 to 3, CH5 to 8) and disables CH4

Note that this algorithm can also be applied if more than 1 channel hang the bus at the same time.

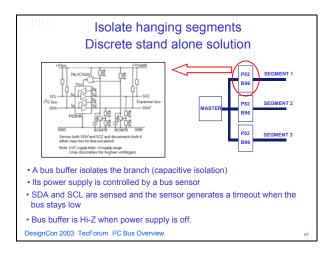

#### Slide 57

Slide 57 shows one discrete solution with option to set timing, by discrete capacitors, to isolate a bus segment.

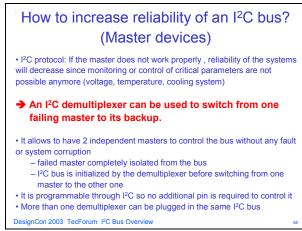

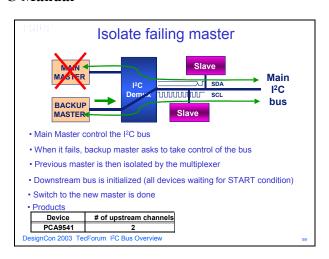

#### Increasing I<sup>2</sup>C Bus Reliability (Master Devices)

#### Slide 58

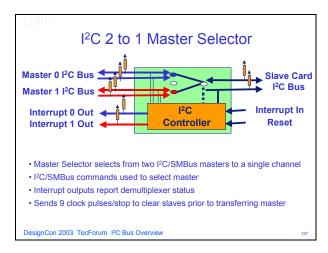

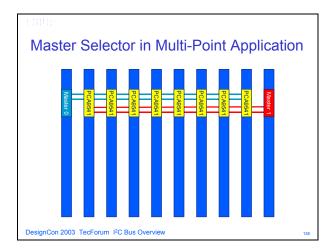

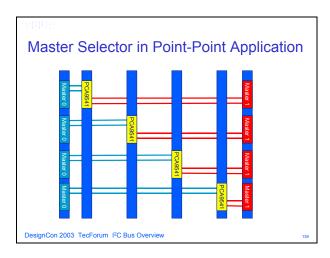

If the I<sup>2</sup>C master fails or does not work properly, reliability of applications will decrease since monitoring and control of essential parameters cannot be controlled anymore (e.g. temperature monitoring, voltage monitoring, cooling control). It is then often essential to have a backup I<sup>2</sup>C master to replace a mal functioning main I<sup>2</sup>C master. The I<sup>2</sup>C 2:1 master selector is then an essential device allowing switching between 2 masters.

#### It can be used in:

- A point to point application master and backup master control one card

- A multi point application master and backup master control several cards.

#### Slide 59

The 2:1 master selector allows switching between one master and its backup (and vice versa if the main master comes back on line). Before switching from one upstream channel to the other one, the device makes sure that the previous device is not on the bus anymore (fully isolated)

The switching is done after making sure that the downstream bus is in a "clean" configuration. All the downstream devices have been initialized again (essential when the previous master failed in the middle of a transaction and thus the bus is not well initialized) and the bus is in an idle configuration. This is done by converting the 2:1 master selector into a temporary master (just after isolating the failing master) allowing it to send the necessary I<sup>2</sup>C sequence (9 clock pulses on SCL while SDA is maintained high then a STOP command). While the sequence is done, the downstream I<sup>2</sup>C bus is well initialized and the switch to the new master can be performed automatically by the PCA9541.

#### Capacitive Loading > 400 pF (Buffer)

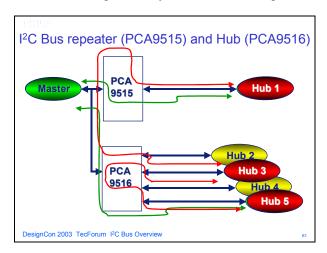

Slide 60

I<sup>2</sup>C bus repeaters and hubs allow increasing the maximum capacitive load on the bus without degrading the AC performances (rising and falling times) of the data and clock signals. They are multi-master capable.

Slide 61

- Repeaters allow doubling the capacitive load, 400 pF on each side of the device

- Hubs allow multiplying the load by 5 with 400 pF on each hub channel

In Slide 61, the possible communication paths are shown in green. No communication is possible over the red paths, no hub can communicate with any other hub. When communication between all hubs and the master is required then a multi-drop bus approach with P82B96 should be used.

Slide 62

There are some applications where more than 5 channels are required. Sub Masters on Server Blades Application - Main Master is able to isolate any blade with the hardware enable pin via  $I^2C$  & GPIO

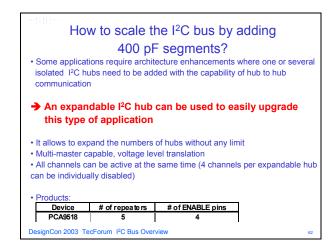

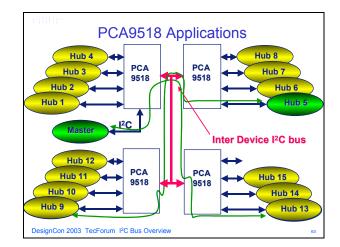

Using the PCA9516 in this application, the sub masters can only talk with sub masters on the same hub or the main master since a low signal can not be sent through two hubs. Sub masters will not be able to arbitrate for bus control if located on different hubs. That is not ideal and limits the designers' ability to expand their I<sup>2</sup>C bus. The PCA9515 and the PCA9516 can only be used one device (either the PCA9515 or PCA9516) per system since low levels will not be transmitted through the second device.

To overcome this limitation, the PCA9518 was released. Similar to the PCA9516 but with four extra open drain signal pins that allow the internal device logic to be interconnected into an unlimited number of segments with only one repeater delay between any two segments.

Slide 63

The PCA9518, like the PCA9515/16, is transparent to bus arbitration and contention protocols in a multi-master environment and any master can talk to any other master on any segment. The enable pins can be used to isolate four of the five segments per device. Place a pull up resistor on the un-isolatable segment and leave it unused if there is a requirement to enable or disable the segment.

Using the PCA9518 in this 15 hub application, any sub master can talk to any other sub master on any of the cards and the main master can talk with any sub master with only one repeater delay.

#### Slide 64

DesignCon 2003 TecForum I<sup>2</sup>C Bus Overv

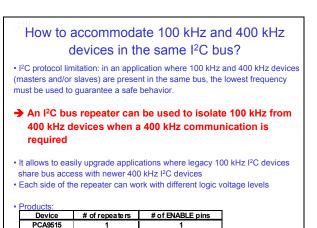

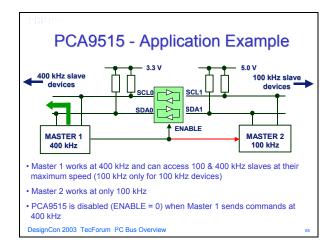

Due to the different I<sup>2</sup>C specification available (100 kHz, 400 kHz and now 3.4 MHz), devices designed for the 100 kHz specification are not suitable to work properly at 400 kHz, while the opposite is true. In applications where upgrades have been performed by using newer 400 kHz devices while keeping the 100 kHz legacy devices, it may become necessary to separate the 400 kHz devices from the 100 kHz devices when a 400 kHz I<sup>2</sup>C transfer is performed.

#### Slide 65

The PCA9515 can be used for this purpose. One side of the device will have all the devices running at 400 kHz while the other side will have all the devices running to 100 kHz.

Note that each side of the PCA9515 can work at different logic voltage levels. For example, the "older" 100 kHz devices can run at 5.0 V while the "newer" 400 kHz devices can work at 3.3 V.

There could also be more than one master in the bus:

- One main master with the ability of choosing between 100 kHz and 400 kHz depending on the devices it needs to talk to.

- Two masters, one working at 100 kHz only (can be part of the system legacy) and another one working at 400 kHz.

In the 1<sup>st</sup> case, the master located in the "400 kHz only" side has the capability to control the PCA9515's ENABLE pin in order to disable the device when a 400 kHz communication is initiated (the "100 kHz only" side will then not see the communication). During a 100 kHz communication, the PCA9515 is enabled to allow communication with the other side. In the 2<sup>nd</sup> case, both masters are located in each side of the PCA9515 and the control is basically the same as above for the 400 kHz devices.

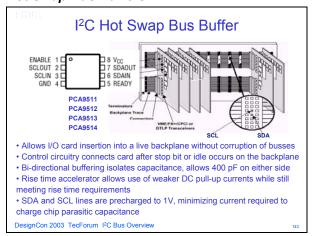

#### Live Insertion into the I2C Bus

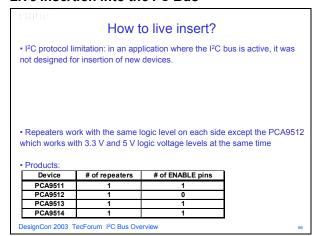

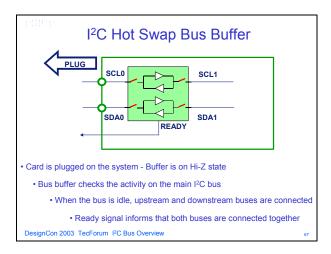

Slide 66

The I<sup>2</sup>C bus was never designed to be used in live insertion applications, but newer applications in for telecom cards that require 24/7 operation require the ability to be removed and inserted into an active system for maintenance and control applications.

#### Slide 67

The PCA9511/12/13/14 are designed for these types of live insertion applications.

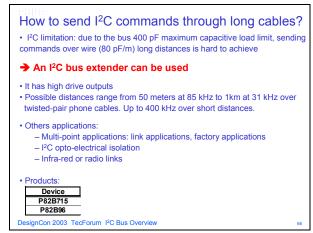

#### Long I2C Bus Lengths

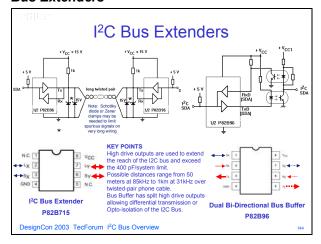

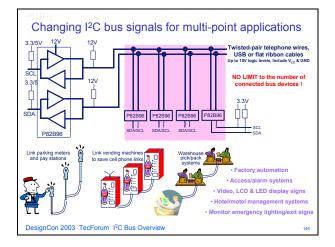

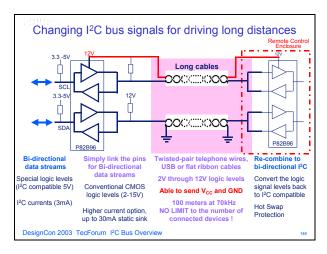

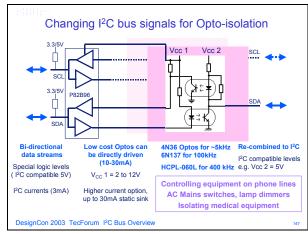

#### Slide 68

The P82B715 and P82B96 are designed for long distance transmission of the I<sup>2</sup>C bus

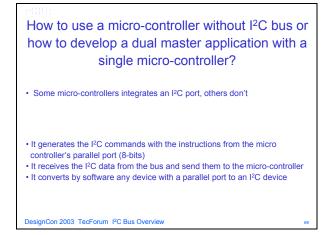

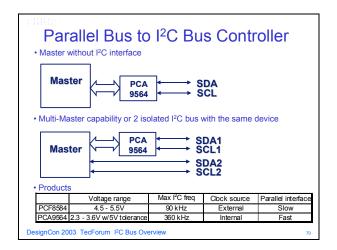

#### Parallel to I2C Bus Controller

#### Slide 69

There are many applications where there is a need to convert 8 bits of parallel data into an I<sup>2</sup>C bus port. The PCF8584 and PCA9564 allow building a single I<sup>2</sup>C master system using the parallel port of a 8051 type microcontroller that does not have an I<sup>2</sup>C interface. It also allows building a double master system with using the built-in I<sup>2</sup>C interface and the parallel port of the same micro-controller.

#### Slide 70

Philips offers two devices, the PCF8584 and PCA9564. The PCA9564 is similar to the PCF8584 but operates at 2.3 to 3.6 V  $V_{\rm CC}$  and up to 360 kHz with various enhancements added that were requested by engineers. The PCA9564 serves as an interface between most standard parallel-bus microcontrollers/ microprocessors and the serial  $I^2$ C bus and allows the parallel bus system to communicate bi-directionally with the  $I^2$ C bus. This commonly is referred as the bus master.

Communication with the I<sup>2</sup>C bus is carried out on a byte-wise basis using interrupt or polled handshake. It

controls all the I<sup>2</sup>C bus specific sequences, protocol, arbitration and timing. The internal oscillator in the PCA9564 is regulated to within +/- 10%.

|                                        | PCA9564  | PCF8584  | Comments                |

|----------------------------------------|----------|----------|-------------------------|

| <ol> <li>Voltage range</li> </ol>      | 2.3-3.6V | 4.5-5.5V | PCA9564 is 5V tolerant  |

| 2. Max I <sup>2</sup> C freq.          | 360 kHz  | 90 kHz   | Faster I <sup>2</sup> C |

| <ol><li>Clock source</li></ol>         | Internal | External | Less expensive and more |

| flexible                               |          |          |                         |

| <ol> <li>Parallel interface</li> </ol> | Fast     | Slow     | Compatible with faster  |

| processors                             |          |          |                         |

In addition, the PCA9564 has been made very similar to the Philips standard 80C51 microcontroller I<sup>2</sup>C hardware so existing code can be utilized with a few modifications.

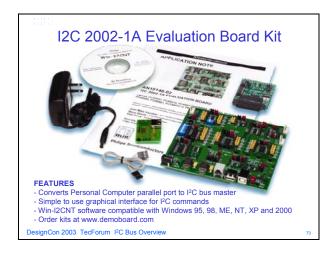

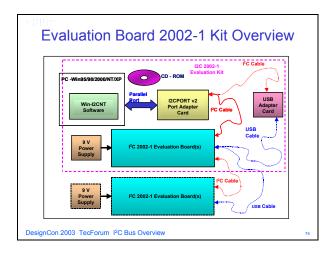

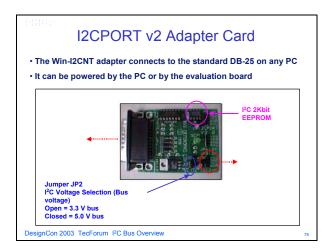

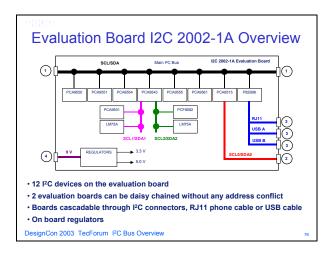

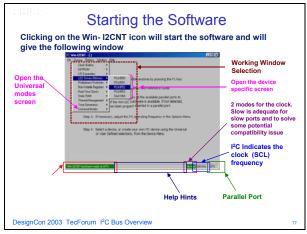

# **Development Tools and Evaluation Board Overview**

# Purpose of the Development Tool and I<sup>2</sup>C Evaluation Board

To provide a low cost platform that allows Field Application Engineers, designers and educators to easily test and demonstrate I<sup>2</sup>C devices in a platform that allows multiple operations to be performed in a setting similar to a real system environment.

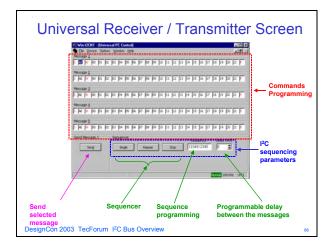

Slide 73

The I2C 2002-1A I2C evaluation board can be purchased from http://www.demoboard.com for \$199.

Demo boards include at demoboard.com include:

I2C-Trace: I<sup>2</sup>C Bus Tracer Kit - I<sup>2</sup>C Monitor captures and displays I<sup>2</sup>C bus messages on any PC

WIN-SMBUS: SMBUS Protocol S/W-H/W Kit - Supports SMBus ICs and the SMBus v1.0 protocol

WIN-I2CNTDLL: 32-bit Win-I2CNT kit including DLL driver and docs - Developer Kit for 32-bit embedded I<sup>2</sup>C applications

WIN-I2CNT: 32-bit I<sup>2</sup>C Software/Adapter kit for Win 95/98/ME/2000, NT 4.x - Enhanced kit for I2C control. Free updates from the Website