### CSE 140L Instructor: C.K. Cheng Oct. 26, 2005

Courtesy of Jianhua Liu

### Agenda

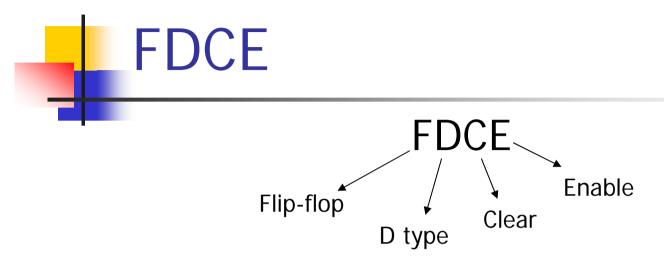

- D flip-flops in Xilinx

- Introduction to Lab 2 assignment

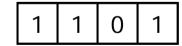

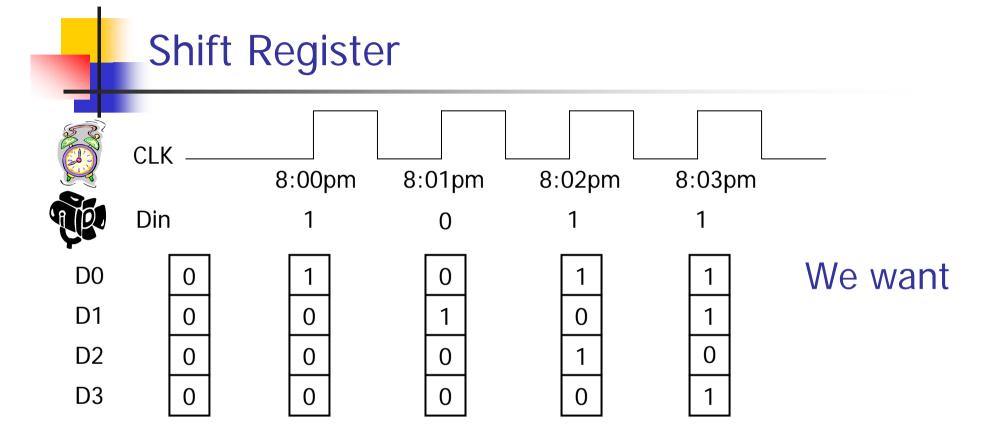

- Shifter register

- Asynchronous counter

- Synchronous counter

- Gray Counter

- Pseudo random sequencer

- A complete example of 4-bit binary counter design

So it's a D flip-flop with Clear and Enable signals, and Clear has priority over Enable.

# FDPED flip-flop with Preset and Enable

| PRE      | -    |       |

|----------|------|-------|

| D<br>CE  | FDPE | •     |

| <u> </u> | >    | X3721 |

|     | Inputs |   |   |        |  |

|-----|--------|---|---|--------|--|

| PRE | CE     | D | с | Q      |  |

| 1   | х      | Х | х | 1      |  |

| 0   | 0      | Х | Х | No Chg |  |

| 0   | 1      | 0 | 1 | 0      |  |

| 0   | 1      | 1 | 1 | 1      |  |

# FTCE T flip-flop with Clear and Enable

|           |     | Inp | uts |   | Outputs |

|-----------|-----|-----|-----|---|---------|

|           | CLR | CE  | т   | с | Q       |

|           | 1   | х   | Х   | Х | 0       |

|           | 0   | 0   | Х   | Х | No Chg  |

| CLR X3764 | 0   | 1   | 0   | Х | No Chg  |

|           | 0   | 1   | 1   | ↑ | Toggle  |

8:03pm

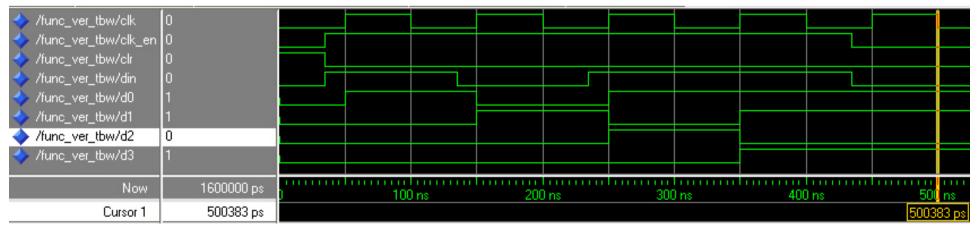

### Verification

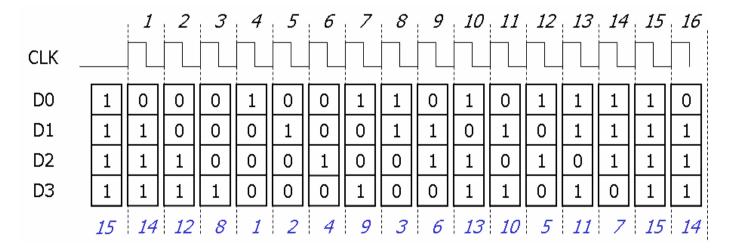

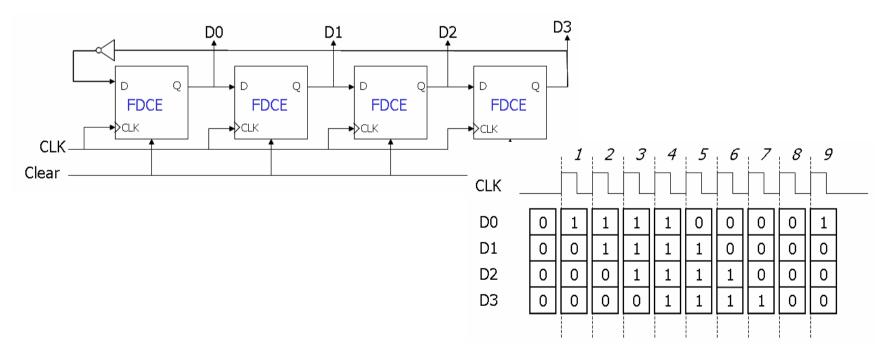

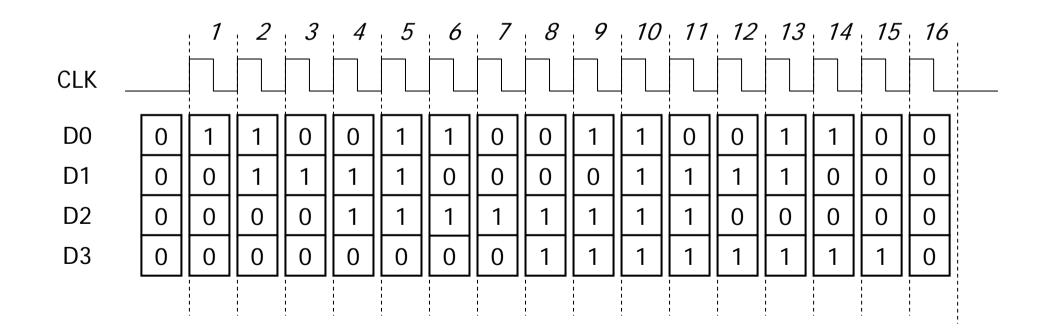

### Counters A counter counts the number of clock cycles 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 CLK D0 D1 D2 D3

### **Counter Styles**

- Synchronous counter

- All flip-flops are governed by a universal global clock signal

- Asynchronous counter

- No universal global clock signal;

- Less area

- You have more flexibility in designing FSMs

- Less power

- Eliminates simultaneous D flip-flop switching during clock transitions

- High speed

- In terms of throughput

- But ...hard to design and error prone

- Complicate protocol for inter-module communication

- Timing!

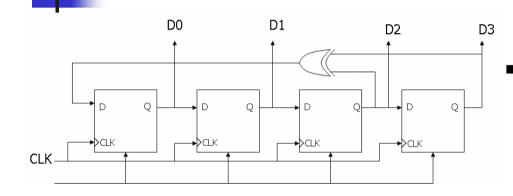

## Asynchronous Counter Do DI DI Design CLR

### Verification

| <ul> <li>/func_ver_tbw/clk</li> <li>/func_ver_tbw/clr</li> <li>/func_ver_tbw/c0</li> <li>/func_ver_tbw/c1</li> <li>/func_ver_tbw/c2</li> <li>/func_ver_tbw/c3</li> </ul> | 1<br>0<br>1<br>0<br>0 |                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|

| Now                                                                                                                                                                      | 2010000 ps            | on and a second and a second |

| Cursor 1                                                                                                                                                                 | 165100 ps             | 165100 ps                                                                                                        |

### Synchronous counter

- Binary counter

- We'll see a design example of this

- Johnson counter

- Gray counter

### Johnson Counter

Last output inverted and feed back to the first input.

also called Mobius counter because it resembles the famous Mobius band.

### **Gray Counter**

- Every two neighboring states differ only in one bit

- Good for reducing hazards in the circuit

### Pseudo Random Sequencer

- A pseudo random sequencer generates a sequence of pseudo random bits.

- Pseudo means it's not complete random, it's actually a cyclic bit sequence with a large period.

- Usually implemented using Linear Feedback shifter Register (LFSR).

### Random Sequencer

- The length of the cycle depends on

- The feedback network

- The initial state