#### **Experiment-5**

# **Feedback Circuits and Other Applications**

# Introduction The objectives of this experiment are to examine the characteristics of several feedback amplifier configurations. Voltage regulators are a rudimentary form of feedback amplifier where the input signal is a DC reference voltage which gets current amplified and passed onward to the load. These are examined first, followed by feedback circuits for short-circuit protection, class-AB output booster stages, and sinewave oscillators.

In addition to the performance measurements, you should also pay attention to how the biasing of each amplifier stage is achieved, how the signal is coupled from stage to stage, and what design strategy has been adopted to desensitize the circuit performance to variations in the transistor parameters. For each circuit in this experiment, try to answer the question: "What has been achieved by connecting the transistors in this configuration?" To begin to answer this question, first identify whether a particular transistor is providing bias stabilization for other transistors, or is a gain stage in the signal path. Some transistors may simultaneously function in both roles. Then try to determine what components set the voltage gain of the circuit. Track the path of the signal through the different stages of the circuit and try to understand how much voltage gain is produced across each stage, how big the signal is at each node along the path, and what limits the signal swing at each node. For each circuit that uses feedback, you should be able to follow a closed path through the circuit corresponding to the feedback loop. Draw a schematic of the amplifier in your lab notebook and mark it up extensively to show the DC bias voltage at each node, the path that the signal takes from input to output, any feedback loops, and any thing else that is of interest to you.

The feedback circuits described in this experiment are not as simple as those previously used in this lab. While all of the component values are fairly close to the values needed to make the circuits work, normal variations in transistor parameters will require that each circuit be "tuned-up" slightly to center the signal swings or trim out the gain. This is left for you to do without any explicit instructions and is intended to force you to understand how the circuits work and to gain skill in electronic troubleshooting. Similarly, the procedures will only ask you to measure certain performance parameters without giving explicit instructions. Procedure 1 Series-pass zener diode positive voltage regulator

Comment The purpose of a voltage regulator is to maintain a constant output voltage across an arbitrary load, independent of the current that is drawn by the load, and independent of the input supply voltage. The simplest form uses a zener diode to provide a reference voltage and then this reference voltage is amplified by a common-collector (CC) or emitter-follower (EF) amplifier stage to provide a low output resistance voltage source. The voltage regulation of this circuit is poor, because the zener diode and base-emitter voltage of the series pass transistor both vary with the load current. Nevertheless, it is a simple circuit to start with. It will be successively improved in procedures 2 and 3 with the addition of various feedback paths.

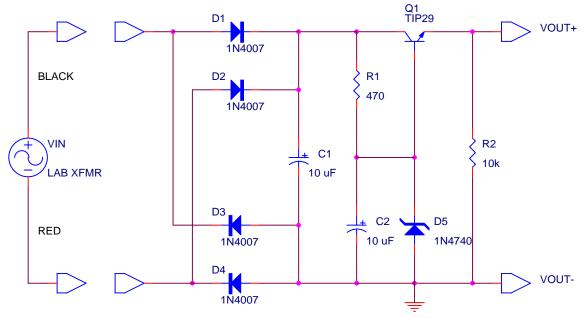

Set-Up Using a solderless breadboard, construct the circuit shown in Fig. E5.1 using the following components:

R1 = 470  $\Omega$  5% 1/4 W R2 = 10 k $\Omega$  5% 1/4 W C1, C2 = 10  $\mu$ F electrolytic D1, D2, D3, D4 = 1N4007 D5 = 1N3518 or 1N4740 zener (10.0 V) Q1 = TIP-29 npn power transistor

Figure E5.1

Configure the laboratory transformer to supply a 20 V peak sinewave to the input of the circuit by connecting the black and red output terminals to the inputs of the regulator circuit.

| Comment       | Diodes D1-D4 create a full-wave bridge rectifier and capacitor C1 provides the initial filtering of its output. R1, C2, and D5 bias the zener diode into its breakdown region, establishing a reference voltage at the base of Q1. Q1 operates as an emitter-follower, with R2 serving as a minimal load. This circuit is sometimes called a "zener-follower" and is perhaps the simplest way to produce a somewhat regulated output voltage. |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement-1 | Turn ON the lab transformer and use a bench DMM to monitor the output voltage across R2. Record the output voltage under these conditions of minimal loading.                                                                                                                                                                                                                                                                                 |

|               | Use an oscilloscope to monitor the voltage waveform across filter capacitor C1, across the zener diode D5, and across the load resistor R2. Record a sketch of each waveform in your lab notebook.                                                                                                                                                                                                                                            |

|               | Attach a 100 $\Omega$ 5% 1 Watt load resistor in parallel with R2 to simulate a heavier load. Measure and record the new output voltage applied to the load. Record in your lab notebook a sketch of the voltage waveforms across C1, D5, and R2 under these conditions.                                                                                                                                                                      |

|               | Keep this circuit set up as is. It will be only slightly modified in procedures 2 and 3.                                                                                                                                                                                                                                                                                                                                                      |

| Question-1    | (a) Calculate the load regulation of this circuit as $\Delta V_{out}/\Delta I_{load}$ . This is effectively the Thevenin output resistance of the voltage regulator.<br>(b) Calculate the maximum load current that this regulator would be able to deliver without dropping the output voltage below 8.5 Volts.<br>(c) Explain what causes the voltage to drop as the load current is increased.                                             |

Procedure 2 Series-pass positive voltage feedback regulator

| Comment         | In the previous regulator, $V_{out} = V_{zener} - V_{BE1,on}$ . Temperature and load current both affect $V_{BE1,on}$ and produce poor regulation. Using feedback to directly sample the output voltage overcomes this limitation.                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

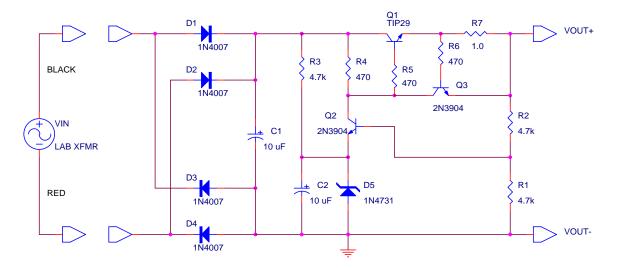

| Set-Up          | Modify the circuit of Fig. E5.1 to that of Fig. E5.2a by inserting<br>another BJT, shown as Q2, whose base samples the output voltage<br>through R1 and R2 and whose collector drives the series pass<br>transistor Q1. Note that D5 is changed to a 1N3509 or 1N4731 (4.3<br>V) zener diode.<br>R1, R2, R3 = 4.7 k $\Omega$ 5% 1/4 W<br>R4 = 470 $\Omega$ 5% 1/4 W<br>C1, C2 = 10 $\mu$ F electrolytic<br>D1, D2, D3, D4 = 1N4007<br>D5 = 1N3509 or 1N4731 zener (4.3 V)<br>Q1 = TIP-29 npn power BJT<br>Q2 = 2N3904 npn BJT |  |  |  |

|                 | D1 Q1<br>TIP29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 | VOUT+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| BLACK           | D2<br>1N4007<br>R3<br>R4<br>4.7k<br>470<br>R2<br>4.7k                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VIN<br>LAB XFMR | 4 C1<br>10 uF<br>Q2<br>2N3904                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| RED             | $ \begin{array}{c}  D3 \\  \hline  1N4007 \end{array} $ $ \begin{array}{c}  + \\  C2 \\  10 uF \end{array} $ $ \begin{array}{c}  D5 \\  1N4731 \end{array} $ $ \begin{array}{c}  R1 \\  4.7k \end{array} $                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

Figure E5.2a

Measurement-2a Turn ON the lab transformer and use a bench DMM to monitor the output voltage across R1+R2. Record the output voltage under these conditions of minimal loading.

Use an oscilloscope to monitor the voltage waveform across filter capacitor C1, across the zener diode D5, and across the load resistors R1+R2. Record a sketch of each waveform in your lab notebook.

Attach a 100  $\Omega$  5% 1 Watt load resistor in parallel with R1+R2 to simulate a heavier load. Measure and record the new output voltage applied to the load. Record in your lab notebook a sketch of the voltage waveforms across C1, D5, and R1+R2 under these conditions.

- Question-2a (a) Calculate the load regulation of this circuit as  $\Delta V_{out}/\Delta I_{load}$ , and comment on how it has been improved by the feedback loop. (b) Explain how Q2 provides a negative feedback loop to help stabilize the output voltage.

- Comment Both of the previous voltage regulators are subject to destruction by shorting the output. In practice, either the fuse on the lab transformer will blow, or the series pass transistor Q1 will fail due to the current overload. Short-circuit protection can be implemented by the addition of another feedback loop. In this case, however, the feedback loop is only effective when the output current reaches a certain value; for the remainder of the time, the short-circuit protection circuit does not affect the operation of the circuit. Because the short-circuit feedback only turns on when needed, it forms a very nonlinear, although darned useful, circuit configuration.

- More Set-Up Modify the circuit of Fig. E5.2a to that of Fig. E5.2b by adding Q3, R5, R6, and R7.

R1, R2, R3 = 4.7 k $\Omega$  5% 1/4 W R4, R5, R6 = 470  $\Omega$  5% 1/4 W R7 = 1.0  $\Omega$  5% 1/4 W C1, C2 = 10  $\mu$ F electrolytic D1, D2, D3, D4 = 1N4007 D5 = 1N3509 or 1N4731 zener (4.3 V) Q1 = TIP-29 npn power BJT Q2, Q3 = 2N3904 npn BJT

Figure E5.2b

Measurement-2b Turn ON the lab transformer and use a bench DMM to monitor the output voltage across R1+R2. Record the output voltage under these conditions of minimal loading; it should be very similar to that measured earlier for Fig. E5.2a.

> Connect a bench DMM to monitor the current flowing out of the voltage regulator, and insert a 10 k $\Omega$  5% 1/4 W resistor to verify that about 0.9 mA flows with this size load. Be careful with the connections when the DMM is used as an ammeter!

Using a piece of hook-up wire, short-circuit the output of the regulator and record the current measured by the DMM. Do not leave the output short-circuited for an extended period of time, as several components may get overheated. The voltage and current output of the voltage regulator should return to their normal values following this test.

Question-2b (a) Explain what determines when Q3 turns on and how this limits the output current.

(b) Explain what function R5 and R6 serve.

*Procedure 3 Opamp positive voltage regulator*

| Comment         | Increasing the gain of<br>regulation of the vol<br>to accomplish this, a<br>voltage regulators.                                                                                                                                       | tage regulator. An                                                                                                                                      | opamp is most co | mmonly used |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|

| Set-Up          | Modify the circuit of<br>feedback transistor (<br>R1, R2, R3 = 4.7<br>R4, R5, R6 = 47<br>R7 = $1.0 \Omega 5\% 1$<br>C1, C2 = $10 \mu$ F<br>D1, D2, D3, D4<br>D5 = $1N3509$ or<br>Q1 = TIP-29 npr<br>Q2 = $2N3904$ np<br>U1 = UA741C b | Q2 with an opamp U<br>7 k $\Omega$ 5% 1/4 W<br>0 $\Omega$ 5% 1/4 W<br>1/4 W<br>electrolytic<br>= 1N4004<br>• 1N4731 zener (4.3<br>n power BJT<br>on BJT | J1.              | placing the |

|                 | D1 .                                                                                                                                                                                                                                  |                                                                                                                                                         | Q1<br>TIP29 R7   |             |

|                 | 1N4007                                                                                                                                                                                                                                |                                                                                                                                                         | R6 1.0           | VOUT+       |

| BLACK           | D2                                                                                                                                                                                                                                    | R3                                                                                                                                                      | R5 470           |             |

| BLACK           | 1N4007                                                                                                                                                                                                                                | 4.7k                                                                                                                                                    | 470 Q2           |             |

| UIN<br>LAB XFMR | - + C1<br>10 uF                                                                                                                                                                                                                       | 3 U1<br>2 UA7                                                                                                                                           | R4 2N3904<br>470 | R2<br>4.7k  |

| RED             |                                                                                                                                                                                                                                       | L+ C2 D5                                                                                                                                                |                  |             |

|                 | 1N4007                                                                                                                                                                                                                                |                                                                                                                                                         |                  | R1<br>4.7k  |

|                 | D4                                                                                                                                                                                                                                    |                                                                                                                                                         |                  |             |

|                 | 1N4007                                                                                                                                                                                                                                | ÷                                                                                                                                                       |                  |             |

Measurement-3 Turn ON the lab transformer and use a bench DMM to monitor the output voltage across R1+R2. Record the output voltage under these conditions of minimal loading; it should be very similar to that measured earlier for Figs. E5.2a and E5.2b.

Attach a 100  $\Omega$  5% 1 Watt load resistor in parallel with R1+R2 to simulate a heavier load. Measure and record the new output voltage applied to the load.

Question-3 (a) Calculate the load regulation of this circuit as  $\Delta V_{out}/\Delta I_{load}$ , and comment on how it has been improved by the opamp in the feedback loop.

(b) If R1+R2 were replaced by a 10 k $\Omega$  potentiometer with the wiper terminal connected to the (–) input of the opamp, over what range of output voltage could the voltage regulator operate? How high could the output voltage rise and still have the regulator regulate?

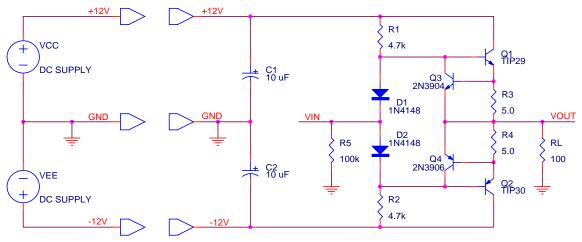

# Procedure 4 Complementary class-AB output stage

Comment Emitter followers (or common-collector) stages were shown to be a nice means for increasing the output current level of an amplifier and buffering voltage gain stages. However, when a large bias current runs continuously through such a stage, it dissipates far more power than it delivers to the load, resulting in poor power efficiency. One way to correct this is to only operate the transistor when it is delivering current to the load, termed class-AB operation. Using two transistors of opposite sex but driven by the same input signal is termed a complementary output stage and provides a power efficient configuration for output buffering or current boosting. This circuit can be used to boost the output current of an opamp. Putting the output stage inside the feedback loop causes the gain of the opamp to linearize the characteristics of the output stage.

Set-Up Construct the circuit shown in Fig. E5.4a on a solderless breadboard using the following components:

R1, R2 = 4.7 k $\Omega$  5% 1/4 W R3, R4 = 5.0  $\Omega$  5% 1/4 W R5 = 100 k $\Omega$  5% 1/4 W RL = 100  $\Omega$  5% 1/4 W C1, C2 = 10  $\mu$ F electrolytic D1, D2 = 1N914 or 1N4148 Q1 = TIP-29 npn power BJT Q2 = TIP-30 pnp power BJT Q3 = 2N3904 npn BJT Q4 = 2N3906 pnp BJT

Figure E5.4a

|                | Configure a dual DC power supply to implement the VCC = $+12.0$ V and VEE = $-12.0$ V DC power supply rails, as shown in Fig. E5.4a. Use three squeeze-hook test leads to connect the outputs of the power supply to your breadboard. Turn the DC power supply ON and initially adjust its outputs to $\pm 12.0$ V, measured relative to the center ground terminal. This center ground terminal is the system ground. If any fuses or transistors blow or overheat, replace either D1 or D2 with a short-circuit. |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Configure a signal generator to produce a 1.0 kHz 5.0 Vpp amplitude sinewave and apply this sinewave across the input resistor R5.                                                                                                                                                                                                                                                                                                                                                                                 |

| Measurement-4a | Use an oscilloscope to monitor the input and output voltage<br>waveforms. Record sketches of the input and output waveforms in<br>your lab notebook.                                                                                                                                                                                                                                                                                                                                                               |

|                | Increase the amplitude of the input signal until the output voltage<br>waveform is clipped on both the positive and negative peaks. Measure<br>and record the output voltage clipping levels.                                                                                                                                                                                                                                                                                                                      |

|                | Restore the input signal to a 1.0 kHz 5.0 Vpp amplitude sinewave and increase the frequency until the output voltage waveform falls to 70 percent of its previous amplitude. This is the -3 dB bandwidth of the output stage.                                                                                                                                                                                                                                                                                      |

| Question-4a    | <ul><li>(a) Calculate the voltage gain for this output stage.</li><li>(b) Comment on any distortion that is seen in the output voltage waveform.</li><li>(c) Calculate the limited value of output current when the short-circuit</li></ul>                                                                                                                                                                                                                                                                        |

|                | protection becomes active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

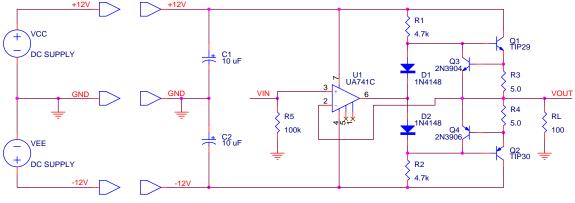

| More Set-Up    | Modify the circuit of Fig. E5.4a to that of Fig. E5.4b by adding an opamp and a feedback loop.<br>R1, R2 = 4.7 k $\Omega$ 5% 1/4 W<br>R3, R4 = 5.0 $\Omega$ 5% 1/4 W<br>R5 = 100 k $\Omega$ 5% 1/4 W<br>RL = 100 $\Omega$ 5% 1/4 W<br>C1, C2 = 10 $\mu$ F electrolytic<br>D1, D2 = 1N914 or 1N4148<br>Q1 = TIP-29 npn power BJT<br>Q2 = TIP-30 pnp power BJT<br>Q3 = 2N3904 npn BJT<br>Q4 = 2N3906 pnp BJT<br>U1 = UA741C opamp                                                                                    |

Figure E5.4b

Measurement-4b Apply a 1.0 kHz 5.0 Vpp sinewave to the input and use an oscilloscope to monitor the input and output voltage waveforms. Record sketches of the input and output waveforms in your lab notebook.

Increase the amplitude of the input signal until the output voltage waveform is clipped on both the positive and negative peaks. Measure and record the output voltage clipping levels.

Restore the input signal to a 1.0 kHz 5.0 Vpp amplitude sinewave and increase the frequency until the output voltage waveform falls to 70 percent of its previous amplitude. This is the -3 dB bandwidth of the overall circuit.

Question-4b

(a) Calculate the voltage gain of the overall circuit.

(b) Compare the clipping levels and bandwidth of the circuit to that of the output stage without the opamp.

(c) Compare the distortion of the opamp circuit to that of the output stage without the opamp. What are the tradeoffs?