# AN10273

# Power MOSFET single-shot and repetitive avalanche ruggedness rating Rev. 02 — 27 March 2009 Applie

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Keywords | ords Power MOSFET, single-shot, avalanche, ruggedness, safe operating condition                                                                                                                                                                                                          |  |

| Abstract | Power MOSFETs are normally measured based on single-shot Unclamped Inductive Switching (UIS) avalanche energy. This note describes in detail the avalanche ruggedness performance, fundamentals of UIS operation and appropriate quantification method for the safe operating condition. |  |

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

#### **Revision history**

| Rev            | Date     | Description                                                                                                                                 |  |  |

|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 02             | 20090327 | Updated                                                                                                                                     |  |  |

| Modifications: |          | <ul> <li>The format of this data sheet has been redesigned to comply with the new identity<br/>guidelines of NXP Semiconductors.</li> </ul> |  |  |

|                |          | <ul> <li>Legal texts have been adapted to the new company name where appropriate.</li> </ul>                                                |  |  |

| 01             | 20030901 | Initial version                                                                                                                             |  |  |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

#### 1. Introduction

Electronic applications have progressed significantly in recent years and have inevitably increased the demand for an intrinsically rugged power MOSFET. Device ruggedness is defined by the capacity of a device to sustain an avalanche current during an unclamped inductive load switching event. However, the avalanche ruggedness performance of a power MOSFET is normally measured within the industry as a single-shot Unclamped Inductive Switching (UIS) avalanche energy or  $E_{AS}$ . Whilst this provides an easy and quick method of quantifying the robustness of a MOSFET in avalanche, it does not necessarily reflect the true device avalanche capability (see Ref. 1, Ref. 2 and Ref. 3) in an application.

This note explains the fundamentals of UIS operation and reviews the appropriate method of quantifying the safe operating condition for a power MOSFET subjected to UIS operating condition. The note also covers the much-discussed repetitive avalanche ruggedness capability and how this operation can be quantified to operate safely.

# 2. Understanding power MOSFET single-shot avalanche events

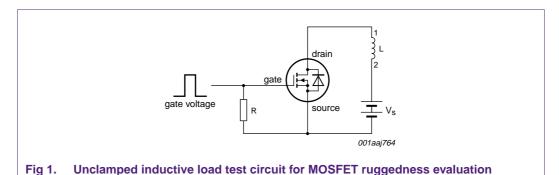

Single-shot avalanche capability of a device has been well established by both researchers and the industry (see <u>Ref. 1</u>, <u>Ref. 2</u> and <u>Ref. 3</u>). The test can be carried out on a simple unclamped inductive load switching circuit as shown in Figure 1.

#### 2.1 Single-shot UIS operation

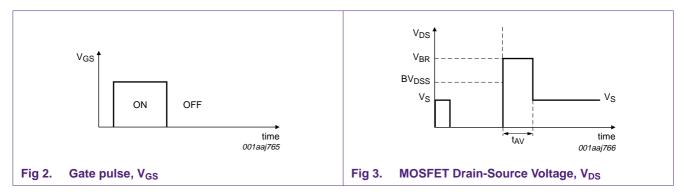

A voltage pulse is applied to the gate to turn the MOSFET ON as shown in <u>Figure 2</u>. This allows the load current to ramp up according to the inductor value (L) and the drain supply voltage ( $V_S$ ) as shown in <u>Figure 3</u> and <u>Figure 4</u>. At the end of the gate pulse, the MOSFET is turned OFF. The current in the inductor continues to flow causing the voltage across the MOSFET to rise sharply. This overvoltage is clamped at breakdown voltage ( $V_{BR}$ ) until the load current reaches zero as illustrated in <u>Figure 3</u>. Typically  $V_{BR}$  is:

$$V_{BR} \approx 1.3 \times BV_{DSS} \tag{1}$$

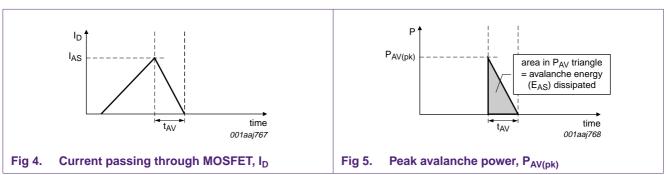

The peak load current passing through the MOSFET before turn OFF will be the single-shot avalanche current (I<sub>AS</sub>) of the UIS event as illustrated in <u>Figure 4</u>. The rate at which the avalanche current decays is dependent on inductor value and can be determined by:

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

$$\frac{dI_{AS}}{dt_{AV}} = -\frac{V_{BR} - V_S}{L} \tag{2}$$

The peak avalanche power  $(P_{AV(pk)})$  dissipated in the MOSFET shown in <u>Figure 5</u> is a product of the breakdown voltage  $(V_{BR})$  and the avalanche current  $(I_{AS})$  as shown in <u>Figure 3</u> and <u>Figure 4</u>, respectively. The avalanche energy dissipated is the area under the  $P_{AV}$  waveform and can be estimated from the following expression:

$$E_{AS} = \frac{P_{AV(pk)} \times t_{AV}}{2} \tag{3}$$

or

$$E_{AS} = \frac{1}{2} \cdot \frac{V_{BR}}{V_{BR} - V_S} \cdot LI_{AS}^2 \tag{4}$$

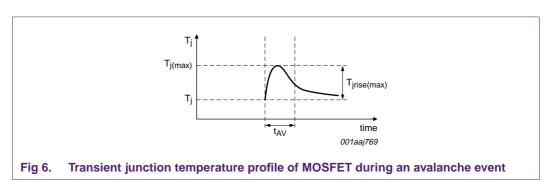

Another crucial parameter involved in a MOSFET avalanche event is the junction temperature. The transient junction temperature rise during device avalanching at a time after the beginning of the avalanche event  $(\tau)$  can be determined by the following expression:

$$T_{jrise}(\tau) = \int_{0}^{\tau} P_{AV}(t) \frac{dZ_{th(\tau - t)}}{dt} dt$$

(5)

where  $Z_{th}$  is the power MOSFET transient thermal impedance. Alternatively, the maximum  $T_{jrise}$  can be approximated by:

$$T_{jrise(max)} \approx \frac{2}{3} P_{av(pk)} Z_{th(t_{AV}/2)} \tag{6}$$

Assuming T<sub>i(max)</sub> occurs at t<sub>AV</sub>/2

where  $Z_{th(t_{AV}/2)}$  is the device transient thermal impedance at half the  $t_{AV}$  period.

The maximum junction temperature resulting from the avalanche event will therefore be:

$$T_{j(max)} \approx T_{jrise(max)} + T_{j} \tag{7}$$

where T<sub>i</sub> refers to the junction temperature prior to turn OFF.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

#### 2.1.1 Single-shot UIS waveforms

## 2.2 Single-shot avalanche ruggedness rating

The failure mechanism for a single-shot avalanche event in a power MOSFET is known to be due to the junction exceeding a maximum temperature above which catastrophic damage is done to the MOSFET. If the transient temperature resulting from an avalanche event, as illustrated in <a href="Figure 6">Figure 6</a>, rises beyond a recommended rated value, the device risks being degraded. The recommended rated value is derated from the maximum temperature for optimum reliability.

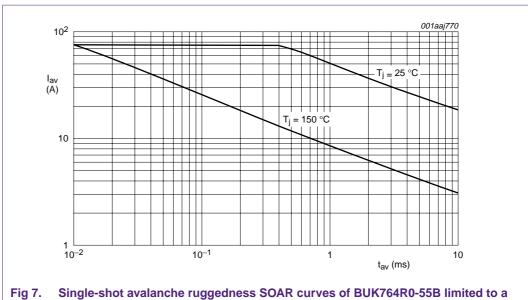

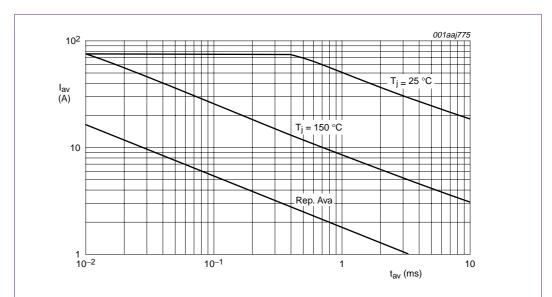

Blackburn (see Ref. 2) has discussed a general guideline in detail on the appropriate method of quantifying the single-shot avalanche capability of a device by taking avalanche current and initial junction temperature into consideration. Safe operation for a device single-shot UIS event can be defined by a maximum allowed avalanche current as a function of avalanche time. The maximum allowed avalanche current is set so that a safe maximum junction temperature,  $T_{j(max)}$  of 175 °C, is never exceeded. Using Equation 7, Figure 7 can be plotted.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

Fig 7. Single-shot avalanche ruggedness SOAR curves of BUK764R0-55B limited to a T<sub>j(max)</sub> of 175 °C

<u>Figure 7</u> shows the SOAR curves of a device single-shot avalanche capability. The 25 °C junction temperature curve shows the maximum allowable  $I_{AS}$  for a given  $t_{AV}$  at an initial  $T_j$  of 25 °C. This maximum  $I_{AV}$  will give rise to a maximum junction temperature,  $T_{jrise(max)}$  of 150 °C resulting in a  $T_{j(max)}$  of 175 °C.

The area under the SOAR curve will be the safe operating area (SOA). Similarly the 150 °C junction temperature curve will be the maximum operating limit for an initial  $T_j$  of 150 °C. The  $I_{AS(max)}$  will induce a  $T_{jrise(max)}$  of 25 °C resulting in a  $T_{j(max)}$  of 175 °C. Again the area under the curve will be the SOA.

The maximum junction temperature resulting in catastrophic device avalanche failure is approximately 380 °C, which is well in excess of the rated  $T_{j(max)}$  of 175 °C. However, operating beyond the rated  $T_{j(max)}$  may induce long-term detrimental effects to the power MOSFET and is not recommended.

# 3. Understanding power MOSFET repetitive avalanche events

Repetitive avalanching simply refers to an operation involving repeated single-shot avalanche events as discussed earlier. Until recently, most manufacturers have avoided the issues pertaining to the power MOSFET repetitive avalanche capability. This is primarily due to the complexity in such operation and the difficulties in identifying the underlying physical degradation process in the device.

Due to the traumatic nature of the avalanche event, a repetitive avalanche operation can be hazardous for a MOSFET, even when individual avalanche events are well below the single-shot UIS rating. This type of operation involves additional parameters such as the frequency, duty cycle and the thermal resistance ( $R_{th}$ ) of the application during the repetitive avalanche event. However, it is possible to derate the single-shot rating to define a repetitive avalanche safe operating area.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

#### 3.1 Repetitive UIS operation

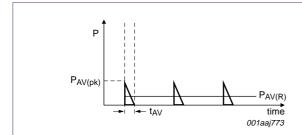

Referring to Figure 1, in a repetitive UIS test the gate is fed with a train of voltage pulses at frequency, f for a duty cycle as shown in Figure 8. The resulting breakdown voltage ( $V_{BR}$ ) and current passing through the load ( $I_D$ ) are the same as for a single-shot UIS except that the peak  $I_D$  will now be denoted as repetitive avalanche current ( $I_{AR}$ ) as shown in Figure 9.

To obtain the average repetitive avalanche power dissipated  $(P_{AV(R)})$  resulting from the repetitive UIS operation as shown in <u>Figure 10</u>. It is necessary to first calculate the E<sub>AS</sub> for a single avalanche event using <u>Equation 3</u>. Subsequently substituting E<sub>AS</sub> into the expression gives:

$$P_{AV(R)} = E_{AS} \times f \tag{8}$$

#### 3.1.1 Repetitive UIS waveforms

Fig 10. Repetitive avalanche power PAV(R)

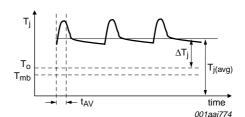

Fig 11. Transient junction temperature components of MOSFET during repetitive avalanching

#### 3.2 Temperature Components

The temperature rise from the repetitive avalanching mode in the power MOSFET can be defined as shown in Figure 11.

The temperature  $(T_o)$  comprises the mounting base temperature  $(T_{mb})$  and the temperature rise resulting from any ON state conduction  $(T_{cond})$ .

$$T_O = T_{mb} + T_{cond} \tag{9}$$

In addition there is a steady-state average junction temperature rise  $(\Delta T_j)$  resulting from the average repetitive avalanche power loss.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

$$\Delta T_j = P_{AV(R)} \times R_{th(j-amb)} \tag{10}$$

where  $R_{th(j\text{-amb})}$  is the thermal resistance of the device in the application. The summation of equations  $\underline{\text{Equation 9}}$  and  $\underline{\text{Equation 10}}$  will give the average junction temperature,  $T_{j(avg)}$  of a power MOSFET in repetitive UIS operation.

$$T_{j(avg)} = T_O + \Delta T_j \tag{11}$$

# 4. Repetitive avalanche ruggedness rating

Following extensive investigation, it is clear that there is more than one failure or wear-out mechanism involved in repetitive avalanching. Temperature is **not** the only limiting factor to a repetitive avalanche operation. However, by limiting the temperature together with the repetitive avalanche current (I<sub>AR</sub>) it is possible to define an operating environment such that the avalanche conditions do not activate any device degradation. This allows the power MOSFET to operate under repetitive UIS conditions safely.

<u>Figure 12</u> shows the avalanche SOAR curves for BUK764R0-55B where 'Rep. Ava' represents the repetitive avalanche SOAR curve.

Fig 12. Single-shot (initial  $T_j = 25~^{\circ}C$  and 150  $^{\circ}C$ ) and repetitive (Rep. Ava) avalanche ruggedness SOAR curves of BUK764R0-55B limited to a  $T_{j(max)}$  of 175  $^{\circ}C$  and  $T_{j(avg)}$  of 170  $^{\circ}C$ , respectively

The two conditions which must be satisfied for safe operation of a power MOSFET under repetitive avalanching mode are as follows:

- 1. IAR should **not** exceed the Repetitive Avalanche SOAR Curve

- 2. T<sub>i(avg)</sub> should **not** exceed 170 °C

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

#### 5. Conclusion

Power MOSFETs can sustain single-shot and repetitive avalanche events. Simple design rules and SOAR regions have been provided.

## 6. Examples

The following examples examine cases of avalanche operation acceptance evaluation.

#### 6.1 Single-shot avalanche case

- Device: BUK764R0-55B refer to Figure 12

- L = 2 mH

- I<sub>AS</sub> = 40 A

- R<sub>th(j-amb)</sub> = 5 K/W

#### 6.1.1 Calculation steps

- 1. Using the above information,  $t_{AV}$  can be determined using Equation 2, which in this case is 1.11 ms. Transferring the  $I_{AV}$  and  $t_{AV}$  conditions onto Figure 12. The operating point is under the  $T_j = 25$  °C SOAR curve but over the  $T_j = 150$  °C SOAR curve suggesting the operating condition maybe feasible.

- 2. To check, calculate the  $T_{jrise(max)}$  using Equation 6, where  $Z_{th(556 \, \mu s)}$  on the data sheet is approximately 0.065 K/W. This will give a  $T_{jrise(max)}$  of 124.8 °C.

Based upon the above calculations, the operating condition is acceptable if the device  $T_i$  < 50 °C.

#### 6.2 Repetitive avalanche case

- Device: BUK764R0-55B refer to Figure 12

- L = 0.5 mH

- I<sub>AR</sub> = 6 A

- f = 3 kHz

- R<sub>th(j-amb)</sub> = 5 K/W

- T<sub>O</sub> = 100 °C

#### 6.2.1 Calculation steps

- t<sub>AV</sub> can be determined from the above information using <u>Equation 2</u> which in this case is ~0.042 ms. Transferring the I<sub>AV</sub> and t<sub>AV</sub> conditions onto <u>Figure 12</u>. The operating point is under the boundary of the 'Rep. Ava' SOAR curve suggesting the operating condition is acceptable. Therefore, condition 1 is achieved.

- 2. Calculate the Single-shot avalanche energy dissipation ( $E_{AS}$ ) using Equation 3 ( $E_{AS} = 9 \text{ mJ}$ ).

- Calculate the average repetitive avalanche power (P<sub>AV(R)</sub>) using <u>Equation 8</u> (P<sub>AV(R)</sub> = 27 W).

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

- 4. Calculate the average  $\Delta T_j$  rise from repetitive avalanche ( $\Delta T_j$ ) using Equation 10 ( $\Delta T_j = 135$  °C).

- 5. Determine the average junction maximum temperature in repetitive avalanche operation ( $T_{j(avg)}$ ) using Equation 11 ( $T_{j(avg)} = 235$  °C). Therefore, condition 2 is not achieved.

Based on the above calculations, the operating conditions satisfied the first but not the second requirement for safe repetitive avalanche operation. This was because the maximum  $T_{j(avg)}$  exceeded 170 °C.

To make the above operation viable, the design engineer has to achieve the  $2^{nd}$  condition by reducing the  $T_{j(avg)}$ . This can be achieved simply by improving the heat sinking of the device. Reducing the  $R_{th(j-amb)}$  from 5 K/W to 2.5 K/W will give a  $T_{j(avg)}$  of 167.5 °C satisfying condition 2 for safe repetitive avalanche operation.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

# 7. Appendix A

The following table describes the symbols used throughout this application note.

Table 1. Description of symbols

| Table 1.                | Description of symbols                        |                                       |

|-------------------------|-----------------------------------------------|---------------------------------------|

| Symbol                  | Description                                   | Remark                                |

| $BV_{DSS}$              | device rated breakdown voltage                |                                       |

| E <sub>AS</sub>         | single-shot avalanche energy                  |                                       |

| I <sub>D</sub>          | MOSFET drain current                          |                                       |

| I <sub>AS</sub>         | single-shot avalanche current                 |                                       |

| I <sub>AR</sub>         | repetitive avalanche current                  |                                       |

| I <sub>AV</sub>         | avalanche current                             |                                       |

| L                       | inductor                                      |                                       |

| P <sub>AV(pk)</sub>     | peak avalanche power                          |                                       |

| P <sub>AV(R)</sub>      | average repetitive avalanche power            |                                       |

| R <sub>th</sub>         | device thermal resistance                     |                                       |

| R <sub>th(j-amb)</sub>  | device junction to ambient thermal resistance |                                       |

| To                      | initial temperature                           | summation of $T_{mb}$ and $T_{cond}$  |

| T <sub>cond</sub>       | ON-state conduction temperature               |                                       |

| Tj                      | junction temperature                          |                                       |

| T <sub>jrise</sub>      | junction temperature rise                     |                                       |

| T <sub>jrise(max)</sub> | maximum junction temperature rise             |                                       |

| T <sub>j(max)</sub>     | maximum Junction temperature                  |                                       |

| $T_{j(avg)}$            | average junction temperature                  | for repetitive avalanche              |

| T <sub>mb</sub>         | mounting base/case temperature                |                                       |

| $\Delta T_{j}$          | average temperature rise from average         |                                       |

| t <sub>AV</sub>         | avalanche period/duration                     |                                       |

| $V_{BR}$                | breakdown voltage                             |                                       |

| $V_{DS}$                | MOSFET drain-source voltage                   |                                       |

| $V_{GS}$                | MOSFET gate-source voltage                    |                                       |

| Z <sub>th</sub>         | device Transient thermal impedance            |                                       |

| $Z_{th(t_{AV}/2)}$      | device transient thermal impedance            | measured at half the avalanche period |

| Vs                      | supply voltage                                |                                       |

#### 8. References

- [1] Turn-off Failure of Power MOSFETs D.L. Blackburn, Proc. 1985 IEEE Power Electronics Specialists Conference, pp 429-435, June 1985.

- [2] Power MOSFET Failure Revisited D.L. Blackburn, Proc. 1988 IEEE Power Electronics Specialists Conference, pp 681-688, April 1988.

- [3] Boundary of Power-MOSFET, Unclamped Inductive-Switching (UIS)

Avalanche-Current Capability Rodney R. Stoltenburg, Proc. 1989 Applied

Power Electronics Conference, pp 359-364, March 1989.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

# 9. Legal information

#### 9.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 9.2 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

#### 9.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### Power MOSFET single-shot/repetitive avalanche ruggedness rating

# 10. Figures

| Fig 1. | Unclamped inductive load test circuit for MOSFET ruggedness evaluation | Fig 8.<br>Fig 9. | Gate pulse, V <sub>GS</sub>                          |

|--------|------------------------------------------------------------------------|------------------|------------------------------------------------------|

| Fig 2. | Gate pulse, V <sub>GS</sub>                                            | -                | avalanche current, I <sub>AR</sub>                   |

| Fig 3. | MOSFET Drain-Source Voltage, V <sub>DS</sub> 5                         | Fig 10.          | Repetitive avalanche power P <sub>AV(R)</sub>        |

| Fig 4. | Current passing through MOSFET, I <sub>D</sub> 5                       | Fig 11.          | Transient junction temperature components of         |

| Fig 5. | Peak avalanche power, P <sub>AV(pk)</sub> 5                            |                  | MOSFET during repetitive avalanching7                |

| Fig 6. | Transient junction temperature profile of MOSFET                       | Fig 12.          | Single-shot (initial $T_j = 25$ C and 150 C) and     |

|        | during an avalanche event                                              |                  | repetitive (Rep. Ava) avalanche ruggedness SOAR      |

| Fig 7. | Single-shot avalanche ruggedness SOAR curves of                        |                  | curves of BUK764R0-55B limited to a $T_{j(max)}$ of  |

|        | BUK764R0-55B limited to a $T_{j(max)}$ of 175 $C6$                     |                  | 175 C and T <sub>j(avg)</sub> of 170 C respectively8 |

|        |                                                                        |                  |                                                      |

## 11. Contents

| 1     | Introduction 3                            |  |

|-------|-------------------------------------------|--|

| 2     | Understanding power MOSFET single-shot    |  |

|       | avalanche events                          |  |

| 2.1   | Single-shot UIS operation                 |  |

| 2.1.1 | Single-shot UIS waveforms 5               |  |

| 2.2   | Single-shot avalanche ruggedness rating 5 |  |

| 3     | Understanding power MOSFET repetitive     |  |

|       | avalanche events 6                        |  |

| 3.1   | Repetitive UIS operation 7                |  |

| 3.1.1 | Repetitive UIS waveforms 7                |  |

| 3.2   | Temperature Components 7                  |  |

| 4     | Repetitive avalanche ruggedness rating 8  |  |

| 5     | Conclusion                                |  |

| 6     | Examples                                  |  |

| 6.1   | Single-shot avalanche case 9              |  |

| 6.1.1 | Calculation steps 9                       |  |

| 6.2   | Repetitive avalanche case 9               |  |

| 6.2.1 | Calculation steps 9                       |  |

| 7     | Appendix A 11                             |  |

| 8     | References                                |  |

| 9     | Legal information                         |  |

| 9.1   | Definitions                               |  |

| 9.2   | Disclaimers                               |  |

| 9.3   | Trademarks12                              |  |

| 10    | Figures                                   |  |

| 11    | Contents 13                               |  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2009.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 27 March 2009 Document identifier: AN10273\_2