# **INTEGRATED CIRCUITS**

# DATA SHEET

# P82B715 I<sup>2</sup>C bus extender

Product data Supersedes data of 2003 Feb 20 2003 Dec 02

I<sup>2</sup>C bus extender P82B715

#### **DESCRIPTION**

The P82B715 is a bipolar IC intended for application in  $I^2C$  bus systems. While retaining all the operating modes and features of the  $I^2C$  system it permits extension of the practical separation distance between components on the  $I^2C$  bus by buffering both the data (SDA) and the clock (SCL) lines.

The I<sup>2</sup>C bus capacitance limit of 400 pF restricts practical communication distances to a few meters. Using one P82B715 at each end of a long cable (connecting Lx/Ly to Lx/Ly) reduces the cable loading capacitance on the I2C bus by a factor of 10 times and allows the total system capacitance load (all devices, connectors, traces and wires that are connected to the I2C bus) to be around 3000 pF. That means longer cables or lower cost general purpose wiring may be used to connect two separate I<sup>2</sup>C based systems without worrying about the special voltage levels associated with other I<sup>2</sup>C bus buffers. Multiple P82B715s can be connected together in a star or multi-point architecture by their Lx/Ly ports without limit as long as the total capacitance of the system remains less than about 3000 pF (400 pF or less when referenced to any Sx/Sy connection). In that arrangement the master and/or slave devices are attached to the Sx/Sy port of each P82B715. The P82B715 alone does not support voltage level translation but it simplifies the application of low cost transistors for this purpose. There is no restriction on interconnecting the Sx/Sy I/Os and those I/Os are also fully compatible with bus buffers that use voltage level offsets (i.e., PCA9511, PCA9515, Sx/Sy side of P82B96) because it duplicates and transmits the offset voltage.

#### **FEATURES**

- Dual, bi-directional, unity voltage gain buffer with no external directional control required.

- I2C Bus compatible

- Logic signal levels may include (but not exceed) both supply and ground

- Logic signal input voltage levels are output without change and are independent of V<sub>CC</sub>

- X10 impedance transformation, but does not change logic voltage levels.

- Supply voltage range 3 V to 12 V

- Clock speeds to at least 100 kHz and 400 kHz when other system delays permit

- ESD protection exceeds 2500 V HBM per Mil. Std 883C-3015.7 and 400 V MM per JESD22-A115. (I/Os have diodes to V<sub>CC</sub> and GND)

- Latch-up free (bipolar process with no latching structures)

#### TYPICAL APPLICATIONS

- Increase the total connected capacitance of an I<sup>2</sup>C system to around 3000 pF (see AN255 appendix 2)

- Drive I<sup>2</sup>C signals over long cables to approximately 50 meters or 3000 pF

- When used in pairs allows, for example, 200 pF on each Sx/Sy I/O plus 2000 pF on the linked Lx/Ly I/Os

- Drives x10 lower impedance bus wiring for improved noise immunity

- Multi-drop distribution of I<sup>2</sup>C signals using low cost twisted-pair cables

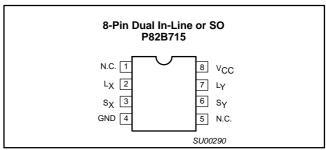

#### PIN CONFIGURATIONS

#### **PINNING**

| PIN | SYMBOL          | FUNCTION                         |

|-----|-----------------|----------------------------------|

| 1   | N.C.            | No connection                    |

| 2   | L <sub>X</sub>  | Buffered Bus, LDA or LCL         |

| 3   | S <sub>X</sub>  | I <sup>2</sup> C Bus, SDA or SCL |

| 4   | GND             | Negative Supply                  |

| 5   | N.C.            | No connection                    |

| 6   | S <sub>Y</sub>  | I <sup>2</sup> C Bus, SCL or SDA |

| 7   | L <sub>Y</sub>  | Buffered Bus, LCL or LDA         |

| 8   | V <sub>CC</sub> | Positive Supply                  |

#### ORDERING INFORMATION

| PACKAGES                            | TEMPERATURE RANGE | ORDER CODE | TOPSIDE MARK | DRAWING NUMBER |

|-------------------------------------|-------------------|------------|--------------|----------------|

| 8-pin plastic dual In-line package  | -40 to +85 °C     | P82B715PN  | P82B715PN    | SOT97-1        |

| 8-pin plastic small outline package | -40 to +85 °C     | P82B715TD  | P82B715      | SOT96-1        |

#### NOTES:

- For applications requiring lower voltage operation, or additional buffer performance, see AN255 I<sup>2</sup>C and SMBus Repeaters, Hubs and Expanders Application Note.

- 2. Standard packing quantities and other packaging data are available at www.philipslogic.com/packaging.

I<sup>2</sup>C bus extender P82B715

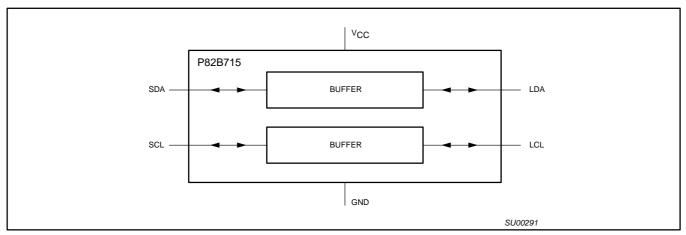

Figure 1. Block Diagram: P82B715

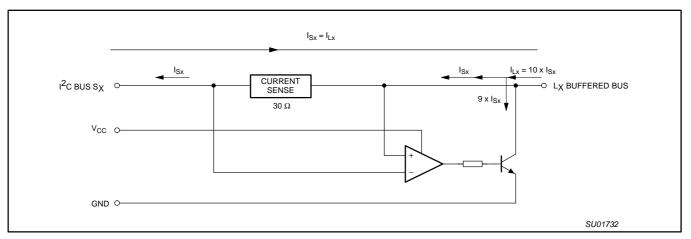

Figure 2. Equivalent Circuit: One Half P82B715

# Sx, Sy, I<sup>2</sup>C-Bus, SDA or SCL

On the normal side, because the two buffer circuits in the P82B715 are identical, either the Sx or Sy input pins can be used as the  $\rm I^2C$  Bus SDA data line, or the SCL clock line.

### Lx, Ly, Buffered Bus, LDA or LCL

On the special low impedance or buffered line side, the corresponding output becomes the LDA data line or LCL clock line.

# V<sub>CC</sub>, GND — Positive and Negative Supply Pins

In normal use the power supply voltages at each end of the low impedance buffered bus line should be the same. If these differ by a significant amount, noise margin is sacrificed.

I<sup>2</sup>C bus extender P82B715

#### **FUNCTIONAL DESCRIPTION**

The P82B715 bipolar integrated circuit is a dual bi-directional logic signal driver that increases the allowable total I<sup>2</sup>C system wiring capacitance. It contains identical circuits, one for each bus signal, and requires no external directional control. It uses unidirectional analog current amplification to increase the current sink capability of I<sup>2</sup>C chips by a factor 10 and to change the 400 pF I<sup>2</sup>C bus specification limit into a 4nF bus wiring capacitance limit. This allows I<sup>2</sup>C, or similar bus systems, to be extended over long distances without degradation of system performance or the use of special cables.

P82B715 provides current amplification from its I<sup>2</sup>C bus to its low impedance or buffered bus. Whenever current is flowing out of Sx, into an I<sup>2</sup>C chip driving the I<sup>2</sup>C bus low, its amplifier will sink ten times that current into Lx to drive the buffered bus low (see Figure 2).

To minimize interference and ensure stability, the current rise and fall times of the Lx drive amplifier are internally controlled.

The P82B715 does not amplify signal currents flowing into Sx on the I²C bus, driven by currents flowing out of Lx on the buffered side. A buffered bus logic low signal at Lx passes via the internal 30  $\Omega$  resistor to drive the I²C bus low.

This signal current amplification, dependent on its direction, preserves the multi-master, bi-directional, open-collector/open-drain, characteristic of any connected I $^2$ C bus lines and the new low impedance bus. Bus logic signal voltage levels will be clamped at (Vcc + 0.7 V) but otherwise are independent of the supply voltage

#### **APPLICATION NOTES**

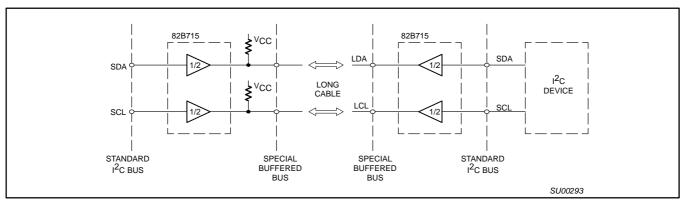

By using two (or more) P82B715 ICs, a sub-system can be built that retains the interface characteristics of a normal  $I^2C$  device so that the sub-system may be included in, or added onto, any  $I^2C$  or related system.

The sub-system features a low impedance or buffered bus, capable of driving large wiring capacitance (see Figure 3).

The P82B715 will operate with a supply voltage from 3 V to 12.5 V but the logic signal levels at Sx/Lx are independent of the chip's supply. They remain at the levels presented to the chip by the attached ICs. The maximum static I²C bus sink current, 3 mA, flowing in either direction in the internal current sense resistor, causes a difference less than 100 mV in the bus logic low levels at Sx and Lx. This makes P82B715 fully compatible with all logic signal drivers, including TTL. The P82B715 cannot modify the bus logic signal voltage levels but it contains internal diodes connected between Lx/Sx and Vcc that will conduct and limit the logic signal swing if the applied logic levels would have exceeded the supply voltage by more than 0.7 V.

In normal applications external pull-up resistors will pull the connected buses up to the desired voltage high level. Usually this will be the chip supply, Vcc, but for very low logic voltages it is necessary to use a Vcc of at least 3.3 V and preferably higher. Note that full performance over temperature is only guaranteed from 4.5 V. Specification de-ratings apply when its supply voltage is reduced below 4.5 V. The absolute minimum Vcc is 3 V.

# I<sup>2</sup>C Systems

As in standard  $I^2C$  systems, pull-up resistors are required to provide the logic high levels on the buffered bus. (The standard open-collector configuration is retained). The size and number of pull-up resistors depends on the system.

If P82B715 ICs are to be permanently connected into a system, the circuit may be configured with only one pull-up resistor on the buffered bus and none on the  $I^2C$  buses, but the system design will be simplified and performance improved by fitting separate pull-ups on each section of the bus. When a sub-system using P82B715 may be optionally connected to an existing  $I^2C$  system that already has a pull-up then the effects of the sub-system pull-ups acting in parallel with the existing  $I^2C$  bus pull-up must be considered.

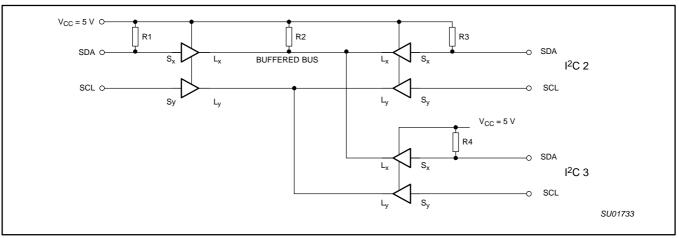

Figure 3. Minimum Sub-System with P82B715

#### **Pull-Up Resistance Calculation**

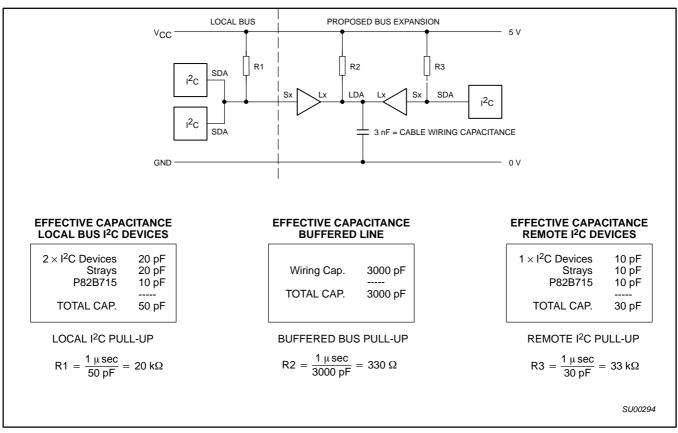

When calculating the pull-up resistance values the gain of the buffer introduces scaling factors which must be applied to the system components. In practical systems the pull-up resistance value is calculated to meet the rise time limit for I<sup>2</sup>C systems. As an approximation, this limit will be satisfied in a 100 kHz system if the time constant of the total system (product of the net resistance and net capacitance) is set to 1 microsecond or less.

In systems using the P82B715 it is convenient to set the total system time constant by considering each bus node separately (i.e., the I<sup>2</sup>C nodes and the buffered bus node)and selecting a separate pull-up resistor for each node to provide time constants of less than 1 microsecond. If each node complies then the system requirement is also met.

2003 Dec 02

I<sup>2</sup>C bus extender P82B715

This arrangement, using multiple pull-ups as in Fig 4, provides the best system performance and allows stand-alone operation of individual I<sup>2</sup>C buses if parts of the extended system are disconnected or re-connected. For each bus section the pull-up resistor is calculated as follows:

$$R = \frac{1\mu s}{C \text{ device} + C \text{ wiring}}$$

Where: C device = sum of any connected device capacitances, and C wiring = total wiring and stray capacitance on the bus section.

[The 1  $\mu s$  is an approximation, with a safety factor, to the theoretical time-constant necessary to meet the specified 1  $\mu s$  bus rise-time specification in a system with variable logic thresholds where the CMOS limits of 30% and 70% of Vcc apply. The calculated value is 1.18  $\mu s$ .]

If these capacitances cannot be measured or calculated then an approximation can be made by assuming that each device presents

10 pF of load capacitance and 10 pF of trace capacitance and that cables range from 50 to 100 pF per metre.

If only a single pull-up must be used then it must be placed on the buffered bus (as R2 in Fig 4) and the associated total system capacitance calculated by combining the individual bus capacitances into an equivalent capacitive loading on the buffered bus.

This equivalent capacitance is the sum of the capacitance on the buffered bus plus 10 times the sum of the capacitances on all the connected  $l^2C$  nodes. The calculated value should not exceed 4 nF. The single buffered bus pull-up resistor is then calculated to achieve the 1  $\mu s$  risetime and it then provides the pull-up for the buffered bus and for all other connected  $l^2C$  bus nodes included in the calculation.

Figure 4. Single Pull-up Buffered Bus

#### Calculating bus drive currents

Figure 4 shows three P82B715s connected to a common buffered bus. The associated bus capacitances are omitted for clarity but assume the resistors have been selected to give R-C products of less than 1 μs so the bus rise time requirement is satisfied. An I<sup>2</sup>C chip connected at I<sup>2</sup>C 1 and holding the SDA bus low must sink the current flowing in its local pull-up R1 plus, with assistance from the P82B715, the currents in R2, R3 and R4. Because the resistors R3 and R4 act to pull the bus nodes I2C 2 and I2C 3, and their corresponding Sx pins, to a voltage higher than the voltage at the Lx pins their buffer amplifiers will be inactive. The SDA at Sx of I<sup>2</sup>C 2 and I<sup>2</sup>C 3 is pulled low by the low at Lx via the internal 30 ohm resistor that links Lx to Sx. So the effective current that must be sunk by the P82B715 buffer on I<sup>2</sup>C 1, at its Lx pin, is the sum of the currents in R2, R3 and R4. The Sx current that must be sunk by an I<sup>2</sup>C chip at I<sup>2</sup>C 1, due to the buffer gain action, is 1/10 of the Lx current. So the effective pull-up, determining the current to be sunk by an I<sup>2</sup>C chip at I<sup>2</sup>C 1, is R1 in parallel with resistors 10 times the values of R2, R3 and R4. If R1 = R3 = R4 = 10k, and R2 = 1k, the effective pull-up load at  $I^2C$  1 is 10k||10k||100k||100k = 4.55 k ohms

The same calculation applies for I<sup>2</sup>C 2 or I<sup>2</sup>C 3.

To calculate the current sunk by the Lx pin of the buffer at  $I^2C$  1 note that the current in R1 is sunk directly by the IC at  $I^2C$  1. The buffer therefore sinks only the currents flowing in R2, R3, and R4 so the effective pull-up is R2 in parallel with R3 and R4.

In this example that's 1k||10k||10k = 833 ohms. For a 5.5 V supply and 0.4 V low that means the buffer is sinking 16.3 mA.

The P82B715 has a static sink rating of 30 mA at Lx. The requirement is that the pull-up on the buffered bus, in parallel with all other pull-ups that it is indirectly pulling low on Sx pins of other P82B715 ICs, will not cause this 30 mA limit to be exceeded.

The minimum pull-up resistance in a 5 V +/-10% system is 170 ohms.

The general requirement is:

$$\frac{V_{CC} \max - 0.4}{R_{D}} < 30 \text{ mA}$$

Where: Rp = parallel combination of all pull-up resistors driven by the Lx pin of the P82B715.

Figure 5 shows calculations for an expanded I<sup>2</sup>C bus with 3 nF of cable capacitance.

I<sup>2</sup>C bus extender P82B715

Figure 5. Typical Loading Calculation: Adding An Extension Bus with P82B715

# **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134). Voltages with respect to pin GND (DIL-8 pin 4).

|                        |                                                | LIM  | ITS             |      |

|------------------------|------------------------------------------------|------|-----------------|------|

| SYMBOL                 | PARAMETER                                      | MIN. | MAX.            | UNIT |

| V <sub>CC</sub> to GND | Supply voltage range V <sub>CC</sub>           | -0.3 | +12             | V    |

| V <sub>bus</sub>       | Voltage range I <sup>2</sup> C Bus, SCL or SDA | 0    | V <sub>CC</sub> | V    |

| $V_{buff}$             | Voltage range Buffered Bus                     | 0    | V <sub>CC</sub> | V    |

| 1                      | DC current (any pin)                           | _    | 60              | mA   |

| P <sub>tot</sub>       | Power dissipation                              | _    | 300             | mW   |

| T <sub>stg</sub>       | Storage temperature range                      | -55  | +125            | °C   |

| T <sub>amb</sub>       | Operating ambient temperature range            | -40  | +85             | °C   |

I<sup>2</sup>C bus extender P82B715

#### **CHARACTERISTICS**

At  $T_{amb}$  = +25 °C and  $V_{CC}$  = 5 Volts, unless otherwise specified.

| SYMBOL                                                                                      | PARAMETER                                                                                                                                                                                          | MIN. | TYP. | MAX.     | UNIT |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|

| Power Supply                                                                                |                                                                                                                                                                                                    |      | •    | •        |      |

| V <sub>CC</sub>                                                                             | Supply voltage (operating) (Note 1)                                                                                                                                                                | 4.5  | _    | 12       | V    |

| I <sub>CC</sub>                                                                             | Supply current                                                                                                                                                                                     | _    | 14   | <u> </u> | mA   |

| I <sub>CC</sub>                                                                             | Supply current at V <sub>CC</sub> = 12 V                                                                                                                                                           | _    | 15   | _        | mA   |

| I <sub>CC</sub>                                                                             | Supply current, both I <sup>2</sup> C inputs LOW, both buffered outputs sinking 30 mA.                                                                                                             | _    | 22   | _        | mA   |

| Drive Currents                                                                              |                                                                                                                                                                                                    |      |      |          |      |

| I <sub>Sx</sub> , I <sub>Sy</sub>                                                           | Output sink on I <sup>2</sup> C bus, $V_{CC} > 3$ V $V_{Sx}$ , $V_{Sy}$ LOW = 0.4 V $V_{Lx}$ , $V_{Ly}$ LOW on Buffered bus = 0.3 V and $I_{LX}$ , $I_{LY}$ = -3 mA (Note 2)                       | 3    | _    | _        | mA   |

| I <sub>Lx</sub> , I <sub>Ly</sub>                                                           | Output sink on Buffered bus $V_{Lx}$ , $V_{Ly}$ LOW = 0.4 V $V_{Sx}$ , $V_{Sy}$ LOW on I <sup>2</sup> C-bus = 0.3 V                                                                                | 30   | _    | _        | mA   |

| De-rated Dynam                                                                              | nic Drive Currents for V <sub>CC</sub> < 4.5 V (Note 1)                                                                                                                                            |      | •    | •        |      |

| I <sub>Lx</sub> , I <sub>Ly</sub>                                                           | Output sink on Buffered bus, $V_{CC} > 3 \text{ V}$<br>$V_{Lx}$ , $V_{Ly}$ LOW = 0.4 V to 1.5 V<br>$I_{SX}$ , $I_{Sy}$ sinking on $I^2C$ -bus < -4 mA                                              | 24   | _    | _        | mA   |

| I <sub>Lx</sub> , I <sub>Ly</sub>                                                           | Output sink on Buffered bus, $V_{CC} > 3 V$<br>$V_{Lx}$ , $V_{Ly}$ LOW = 1.5 V to $V_{CC}$<br>$I_{Sx}$ , $I_{Sy}$ sinking on $I^2C$ -bus = -7 mA                                                   | 24   | _    | _        | mA   |

| Input Currents                                                                              |                                                                                                                                                                                                    | •    | •    | •        | •    |

| I <sub>Sx</sub> , I <sub>Sy</sub>                                                           | Input current from I <sup>2</sup> C bus when $I_{Lx}$ , $I_{Ly}$ sink on Buffered bus = 30 mA                                                                                                      | _    | _    | -3       | mA   |

| I <sub>Lx</sub> , I <sub>Ly</sub>                                                           | Input current from Buffered bus ( $V_{CC} > 3 \text{ V}$ ) when $I_{Sx}$ , $I_{Sy}$ sink on $I^2C$ bus = 3 mA (Note 2)                                                                             | _    | _    | -3       | mA   |

| I <sub>Lx</sub> , I <sub>Ly</sub>                                                           | Leakage current on Buffered bus, $V_{CC} = 3 \text{ V}$ to 12 V $V_{Lx}$ , $V_{Ly} = V_{CC}$ , and $V_{Sx}$ , $V_{Sy} = V_{CC}$                                                                    | _    | _    | 200      | μΑ   |

| Impedance Tran                                                                              | sformation                                                                                                                                                                                         |      |      |          |      |

| Z <sub>in</sub> /Z <sub>out</sub>                                                           | Input/Output impedance V <sub>SX</sub> < V <sub>LX</sub> and buffer is active                                                                                                                      | 8    | 10   | 13       |      |

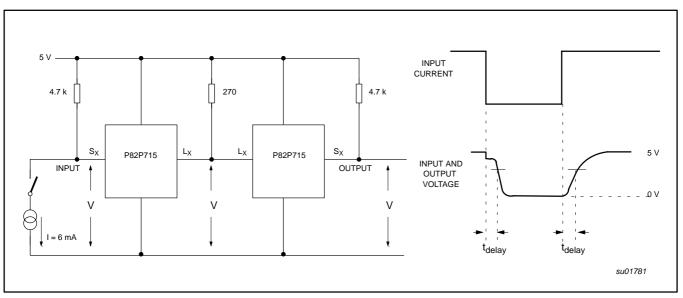

| Buffer Delay Tin                                                                            | nes                                                                                                                                                                                                |      |      |          |      |

| rise/fall delay<br>Sx to V <sub>Lx</sub><br>Sy to V <sub>Ly</sub>                           | Time delay to $V_{Lx}$ voltage crossing $V_{CC}/2$ for input drive current step $I_{SX}$ at $S_X$ , see Figure 6 (Note 3).<br>$R_{Lx}$ pull up = 270 $\Omega$ , no capacitive load, $V_{CC}$ = 5 V | _    | 250  |          | ns   |

| rise/fall delay<br>/ <sub>Lx</sub> to V <sub>Sx</sub><br>/ <sub>Ly</sub> to V <sub>Sy</sub> | Buffer time delay of switching edges, between $V_{Lx}$ input and $V_{Sx}$ output (Note 4).<br>$R_{Sx}$ pull up = 4700 $\Omega$ , no capacitive load, $V_{CC}$ = 5 V                                | _    | 0    | _        | ns   |

#### NOTES:

- Operation with reduced performance is possible down to 3 V. Typical static sinking performance is not degraded at 3 V, but the dynamic sink

currents while the output is being driven through V<sub>CC</sub>/2 are reduced and can increase fall times. Timing-critical designs should accommodate

the guaranteed minimums.

- 2. Buffer is passive in this test. The S<sub>X</sub>/S<sub>Y</sub> sink current flows via an internal resistor to the driver connected at the L<sub>X</sub>/L<sub>Y</sub> I/O.

- 3. A conventional input-output delay will not be observed in the S<sub>X</sub>/L<sub>X</sub> voltage waveforms because the input and output pins are internally tied with a 30 Ω resistor so they show equal logic voltage levels, to within 100 mV. When connected in an I<sup>2</sup>C system an S<sub>X</sub>/S<sub>Y</sub> input pin cannot rise/fall until the buffered bus load at the output pin has been driven by the internal amplifier. This test measures the bus propagation delay caused to falling or rising voltages at the L<sub>X</sub>/L<sub>Y</sub> output (as well as the S<sub>X</sub>/S<sub>Y</sub> input) by the amplifier's response time. The figure given is measured with a drive current as shown in Figure 6. Because this is a dynamic bus test, in which a corresponding bus driving IC has an output voltage well above 0.4 V, 6 mA is used instead of the static 3 mA.

- The signal; path L<sub>χ</sub> to S<sub>χ</sub> and L<sub>γ</sub> to S<sub>γ</sub> is passive, via the internal 30 Ω resistor. There is no amplifier involved and essentially no signal propagation delay.

I<sup>2</sup>C bus extender P82B715

Figure 6. Test circuit for delay times

I<sup>2</sup>C bus extender P82B715

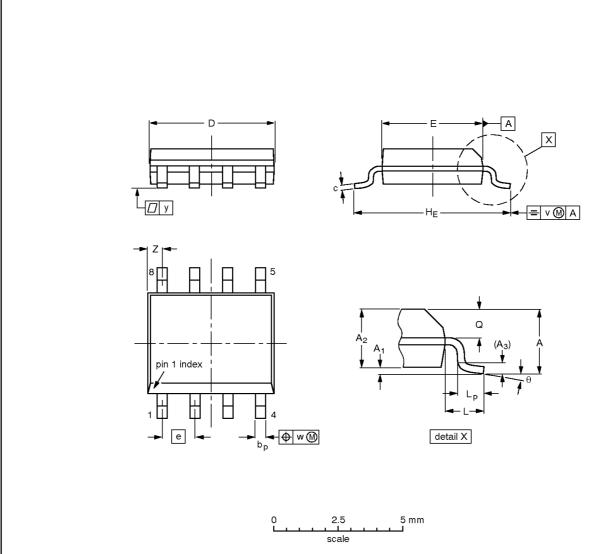

# SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bр           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | e    | HE             | L     | Lp             | Q              | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27 | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.05 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 | 0.028<br>0.024 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE |        | REFER  | EUROPEAN | ISSUE DATE |                                 |

|---------|--------|--------|----------|------------|---------------------------------|

| VERSION | IEC    | JEDEC  | JEITA    | PROJECTION | 1350E DATE                      |

| SOT96-1 | 076E03 | MS-012 |          |            | <del>99-12-27</del><br>03-02-18 |

I<sup>2</sup>C bus extender P82B715

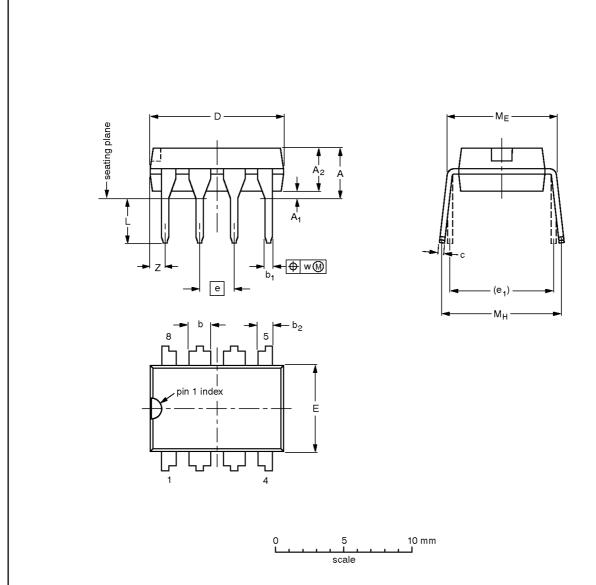

# DIP8: plastic dual in-line package; 8 leads (300 mil)

SOT97-1

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | e    | e <sub>1</sub> | L            | ME           | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|--------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.14   | 0.53<br>0.38   | 1.07<br>0.89   | 0.36<br>0.23   | 9.8<br>9.2       | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3  | 0.254 | 1.15                     |

| inches | 0.17      | 0.02                   | 0.13                   | 0.068<br>0.045 | 0.021<br>0.015 | 0.042<br>0.035 | 0.014<br>0.009 | 0.39<br>0.36     | 0.26<br>0.24     | 0.1  | 0.3            | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33 | 0.01  | 0.045                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE |        | REFEF  | EUROPEAN | ISSUE DATE |            |                                 |

|---------|--------|--------|----------|------------|------------|---------------------------------|

| VERSION | IEC    | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                      |

| SOT97-1 | 050G01 | MO-001 | SC-504-8 |            |            | <del>99-12-27</del><br>03-02-13 |

I<sup>2</sup>C bus extender P82B715

# **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                     |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------|

| _6  | 20031202 | Product data (9397 750 12452); ECN 853-2240 01-A14516 of 14 November 2003; supersedes data of 2003 Feb 20 (9397 750 11094).     |

|     |          | Modifications:                                                                                                                  |

|     |          | <ul> <li>Description and application information was added and limits on the devices<br/>preformance were pulled in.</li> </ul> |

| _5  | 20030220 | Product data (9397 750 11094); ECN 853-2240 29410 of 22 January 2003; supersedes data of 2001 Mar 06 (9397 750 08163).          |

| _4  | 20010306 | Product data (9397 750 08163); ECN 853-2240 25757 of 2001 Mar 06.                                                               |

I<sup>2</sup>C bus extender P82B715

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ı     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- [2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- [3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to:

sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2003 All rights reserved. Printed in U.S.A.

Date of release: 12-03

Document order number: 9397 750 12452

Let's make things better.

Philips Semiconductors