# SINEWAVE OSCILLATORS

## 1. OSCILLATION MECHANISM

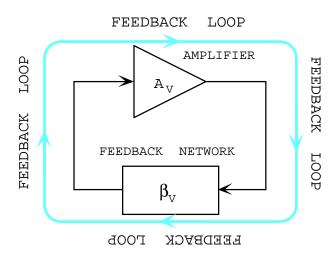

An amplifier with feedback is shown above.  $A_V$  and  $\beta_V$  are normally frequency dependant gains which have complex values - magnitude and phase or real and imaginary parts. At some frequency feedback can become <u>re-generative</u> (an initial train of oscillations will be regenerated by the feedback loop) if phaseshift introduced by  $A_V$  and  $\beta_V$  becomes 360° and the loop may produce sustained sinewave oscillations.

#### BARKHAUSEN OSCILLATION CRITERION

## 1. Transient starting condition

Upon application of power to the oscillator circuit, the output amplitude is 0V, therefore one must initiate the oscillations by injecting some energy at some point in the circuit - this is usually done by inputing a single pulse at the appropriate point. Once the oscillations have started, their amplitude must grow until it reaches the desired level and then stay constant. For this to happen, the loop gain must be greater than  $1/0^{\circ}$  initially.

Loop gain

$$L(S) = \beta_V A_V \ \rangle \ 1 \ \underline{/0^{\circ}}$$

for growing oscillations

# 2. Steady state running condition

Once the oscillations have reached the desired level, the loop gain must be exactly  $1\underline{/0^{\circ}}$  to maintain constant amplitude oscillations. The oscillations will occur at the frequency where the phaseshift of the loop gain is exactly  $0^{\circ}$  or  $\pm N \times 360^{\circ}$ .

gain is exactly 0° or ±N × 360°.

Loop gain

$$L(S) = \beta_V A_V = 1 \, \underline{/0^\circ}$$

for constant amplitude oscillations

Frequency

$$\hat{L}(S) = \pm N \times 360^{\circ}$$

where N = 0, ±1, ±2, ±3, etc.

#### **LOOP GAIN**

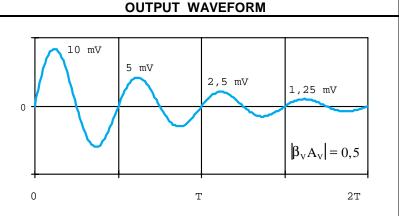

# CASE#1 De-generative feedback

$$|L(j\omega)|\langle 1$$

$$\hat{L}(j\omega) = \pm 360^{\circ}$$

Decreasing amplitude, oscillations are damped. This is the condition desired for a stable amplifier, the faster the oscillations are damped (less loop gain), the more stable the amplifier is.

Let's assume  $|\beta_V A_V| = 0.5$  and that a 10 mV<sub>P</sub> sinewave is initiated at the output. Every time the oscillation goes around the loop it will be amplified by a loop gain of 0.5, or attenuated 2 times (i.e. attenuation = 1 / gain (v/v) or attenuation (dB) = -gain (dB)). Therefore the output sinewave will be damped out and will not be sustained

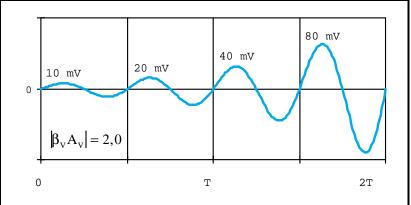

# CASE#2 Re-generative feedback

$$|L(j\omega)\rangle 1$$

$$\hat{L}(j\omega) = \pm 360^{\circ}$$

Increasing amplitude until non-linearity of circuit limits the amplitude or saturation of circuit occurs - sustained oscillations.

Oscillator startup - the larger the loop gain is, the faster the oscillations grow.

Assuming a loop gain of two, the amplitude doubles every time they go around the loop, therefore the amplitude grows exponentially until non-linearity or saturation limits the amplitude.

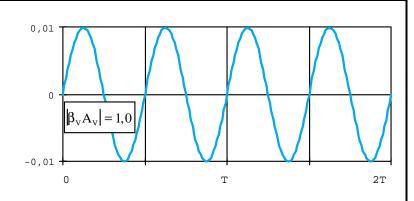

## CASE#3 Re-generative feedback

$$|L(j\omega)| \equiv 1$$

$$\hat{L}(j\omega) = \pm 360^{\circ}$$

Constant amplitude, sustained oscillations. Oscillator has reached a steady state operation. The oscillations are amplified by a gain of 1 every time they go around the loop, therefore their amplitude stays perfectly constant.

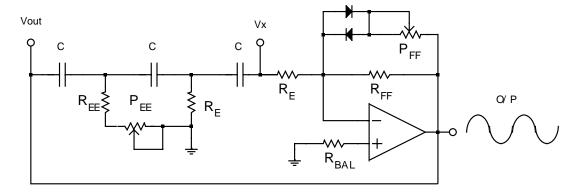

# 2. PHASESHIFT OSCILLATOR

#### Description

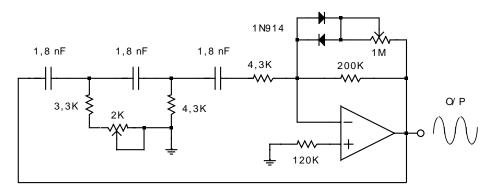

This circuit provides a low-frequency sinewave with a THD around 0,2% for large amplitudes and a THD around 2% for small amplitudes. The frequency can be trimmed within a narrow range but this will also vary the output amplitude which can be re-adjusted with  $P_{\rm FF}$ . Amplitude is adjustable.

Diodes: form a non-linear resistor that will stabilise the loop gain to one when the amplitude of the oscillations has reached the proper level.

P<sub>FF</sub>: adjustment of the output amplitude.

P<sub>EE</sub>: trimming of the frequency of oscillation - narrow range.

R<sub>E</sub> and C: determine the frequency of oscillation

$R_F$  and  $R_E$ : determine the gain of the inverting amplifier, that is  $A_V = -R_F/R_E$ .

Loop gain and frequency of oscillation

$$L(S) = \beta_{V} A_{V} = \left( \frac{(SRC)^{3}}{(SRC)^{3} + 6(SRC)^{2} + 5(SRC) + 1} \right) \times \left( -\frac{R_{F}}{R_{F}} \right) \quad \text{where} \quad R_{F} = R_{FF} \| (P_{FF} + r_{d}) \| (P_{FF} + r_$$

If we replace S with  $j\omega$  and simplify, we obtain:

$$L(j\omega) = \left[ \left( 1 - \frac{5}{(\omega RC)^2} \right) - j \left( \frac{6}{(\omega RC)} - \frac{1}{(\omega RC)^3} \right) \right]^{-1} \times \left( -\frac{R_F}{R_E} \right) = 1 \frac{\sqrt{360^\circ}}{180^\circ}$$

real imaginary  $\frac{\sqrt{180^\circ}}{1}$

The first term must have an angle of 180° for a total of 360° and this will occur only if its imaginary part is <u>zero</u> and its real part is negative.

$$\left(\frac{6}{(\omega RC)} - \frac{1}{(\omega RC)^3}\right) = 0 \quad \Rightarrow \quad \omega_n = \left(\sqrt{6} \times R_E C\right)^{-1} \quad \Rightarrow \quad L(j\omega_n) = \left[-\frac{1}{29}\right] \times \left(-\frac{R_E}{R_E}\right)$$

## Practical considerations

### Starting conditions:

V<sub>out</sub> low amplitude, diodes are OFF.

$R_F = R_{FF} \parallel \infty$ , therefore make  $R_F > 29 R_E$  for a loop gain > 1. Use a loop gain of at least 1,5 to ensure proper start of oscillations.

Vout large amplitude, diodes are ON.

$R_F = R_{FF} \mid \mid (P_{FF} + r_d)$  therefore make  $R_F = 29 R_E$  for a loop gain = 1. Assuming that the diodes resistance is negligible, aim for an approximate pot setting of  $P_{FF} / 3$ .

$$L(j\omega_n) = \left[-\frac{1}{29}\right] \times \left(-\frac{R_{FF}}{R_F}\right) \rangle 1,5$$

$$R_F = 29R_E = R_{FF} || (P_{FF} / 3)$$

### Design example

Design a phaseshift oscillator with a frequency of 10 kHz. Frequency should be trimmable because frequency determining components have % tolerances.

#### Final circuit

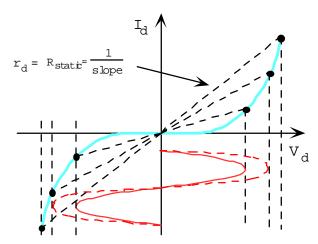

#### Loop Gain Stabilisation

The diodes are non-linear and can be represented as a non-linear resistor. As the amplitude of the output sinewave increases, the diodes will conduct more current and their static resistance will decrease as shown beside. The final amplitude of the signal will stabilise when the diode resistance makes the loop gain exactly equal to one,

$$R_{FF} | (P_{FF} + r_d) = 29 R_E$$

$$\beta_{V}A_{V} = \beta_{V} \left( -\frac{R_{FF} \| (P_{FF} + r_{d})}{R_{E}} \right)$$

Back to back diodes characteristics

# 3. BASIC WIEN BRIDGE OSCILLATOR

#### Basic circuit

$$R_2 = R_{2A} + P_{2A}$$

$R_E = R_{EE} + P_{EE}$

$R_1C_1$  and  $R_2C_2$  form a frequency dependant voltage divider that feeds the output back to V+ of the op amp which amplifies V+ by the non-inverting gain of  $1 + R_{\text{F}}/R_{\text{E}}$ . Since the non-inverting gain has a phaseshift of 0°, the circuit will oscillate when V+ is in phase with the output.

The VVR is a voltage variable resistor that is used to adjust the loop gain automatically to one when it is used in an AGC loop (Automatic Gain Control). The AGC loop will generate the proper DC voltage that will set the VVR resistance to its desired value.

#### Loop gain

$$L(S) = \beta_{V} A_{V} = \left(\frac{\frac{S}{R_{1}C_{2}}}{S^{2} + \left(\frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{2}} + \frac{1}{R_{1}C_{2}}\right)S + \frac{1}{R_{1}C_{1}R_{2}C_{2}}}\right) \times \left(1 + \frac{R_{F}}{R_{E}}\right)$$

$$\beta_{V} = V^{+}/V_{OUT}$$

Replacing S with  $j_{\omega}$  we obtain the loop gain L( $j_{\omega}$ ) as a function of frequency. One can show that the loop gain will have a phase angle of 0° at the following frequency:

$$\omega_n = \frac{1}{\sqrt{R_1 C_1 R_2 C_2}}$$

where  $\beta_V A_V = \left(1 + \frac{R_1}{R_2} + \frac{C_2}{C_1}\right)^{-1} \times \left(1 + \frac{R_F}{R_E}\right)$

The circuit will oscillate at  $\omega_n$  if the loop gain is appropriate and the starting conditions are respected.

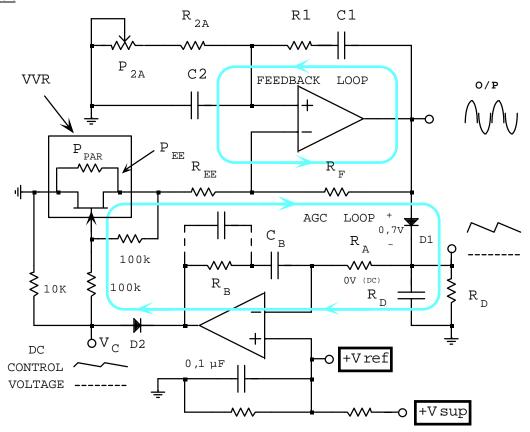

### Actual circuit

## Description of AGC loop

The envelope detector produces a DC voltage that is approximately equal to the peak O/P voltage minus the 0,7V lost across the diode - this assumes negligible  $\Delta V_D \approx \frac{V_{O(\textit{peak})} - 0,7}{R_D C_D \, F}$  ripple voltage across C<sub>D</sub>.

The reference op amp is actually an error amplifier which generates the proper  $V_C$  to correct the output amplitude.  $V_C = A_d \times V_d = A_d (V_{REF} - (V_{oP} - 0.7))$ .  $V_d$  is very small since  $A_d$  of op amp is very large. If  $V_{OP} \downarrow$ , then  $V_d \uparrow$ ,  $V_C \uparrow$ ,  $R_{EO} \downarrow$  and  $A_V \uparrow$ , which increases  $V_{OP}$  that will stabilise at  $V_{REF}$ -0.7.

The error amp will force the two inputs equal, that is  $V_D(DC) = V_{REF}$ . Notice that there is no DC current through  $R_A$ , therefore 0V DC across it.  $R_A$ ,  $R_B$  and  $C_B$  stabilise the AGC feedback loop and determine the speed of this loop - that is  $\tau = R_A$   $C_B$ . For a stable AGC loop, make  $R_A$   $C_B$ . <  $R_D$  and do not choose  $R_D$  too large. Also make  $(2\pi R_B C_B)^{-1}$  <  $F_{OSC}$  to make  $A_V(AC)$ =- $R_B$  / $R_A$  at ripple frequency.

The diode at the O/P of the error amp prevents positive voltages to appear on the gate of the JFET because forward biasing of the gate-channel junction is a NO NO. At start up  $V_{OP}$  is 0V,  $V_2^-$  = 0V,  $V_2^+$  =  $V_{REF}$  which will saturate the error amp O/P positively, D2 will be OFF and  $V_C$  = 0V and  $V_C$  = 0V and  $V_C$  = R<sub>ON</sub>|| R<sub>PAR</sub> which will cause maximum loop gain to build up O/P amplitude until  $V_{OP}$  - 0,7 surpasses  $V_{REF}$ , then  $V_C$  becomes negative and D2 will turn ON and  $V_C$  will go negative to increase  $V_C$  and reduce the loop gain to stabilise the O/P amplitude.

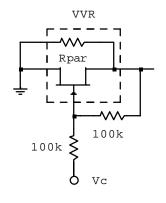

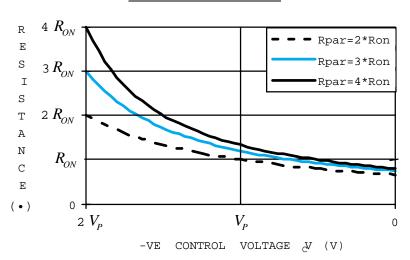

## JFET-VVR characteristics

$$r_{ds} \approx \frac{R_{ON}}{1 - \frac{V_C}{2V_P}} \Rightarrow R_{EQ} = R_{PAR} || r_{ds}$$

$R_{ON}$ : JFET channel ON resistance  $V_P$ : channel pinchoff voltage For an N channel JFET both  $V_C$  and  $V_P$  must be negative ( for P-JFET, both positive)

$R_{EQ}$  in the above expression assumes that the two 100K resistors are much larger than  $R_{PAR} \| r_{ds}$

The two 100K resistors provide 50% feedback (optimum %) from the drain to the gate in order to reduce the distortion introduced by the non-linear resistance of the JFET channel. It can also be shown that minimum distortion is obtained if we bias the JFET at  $V_{GS} = V_P/2$  or  $V_C = V_P$ . The lower the AC signal across drain and source, the less distortion is encountered. JFETs with larger  $V_P$  values will produce less distortion with same amplitude AC signals.

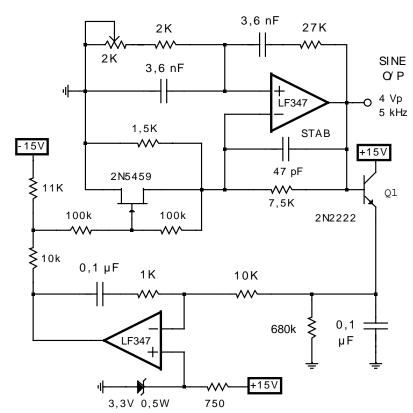

**DESIGN EXAMPLE:** Design a Wien bridge oscillator that produces a 5 kHz/4V<sub>P</sub> sinewave with a THD less than 0,1%. Frequency must be trimmable. Use a 2N5459 as the VVR :  $V_P = -5.8V$ ,  $I_{DSS} = 9$  mA,  $r_{ds(ON)} = 500\Omega$  (typical values)

1. Calculation of  $R_{\text{E}}$  and  $R_{\text{F}}$  for low THD and loop gain variation

For  $C_1 = C_2$ , we have:

$$\beta_{V}A_{V} = \frac{\left(1 + \frac{R_{E}}{R_{E}}\right)}{\left(1 + \frac{R_{1}}{R_{2}} + \frac{C_{2}}{C_{1}}\right)} = \frac{\left(1 + \frac{R_{F}}{R_{E}(VAR)}\right)}{\left(2 + \frac{R_{1}}{R_{2}(VAR)}\right)} = 1 \frac{10^{\circ}}{10^{\circ}}$$

R<sub>E</sub> ranges from R<sub>ON</sub>||R<sub>PAR</sub> to R<sub>PAR</sub> that is  $\frac{R_E \max}{R_E \min} = \frac{R_{PAR}}{R_{PAR}} = 1 + \frac{R_{PAR}}{R_{ON}} = 4 \Rightarrow R_{PAR} = 3R_{ON}$

$R_{PAR} = 3 \times 500 = 1,5 \text{K}$  therefore  $R_{E \text{ min}} = 500 \text{ | | } 1500 = 375 \text{ and } R_{E \text{ max}} = \infty \text{ | | } 1500 = 1500 \text{ | } 1500 = 15000 \text{ | } 15000 = 15000 \text{ | } 1500 = 15000 \text{ | } 15000 = 15000 \text{ | } 15000 = 15000 \text{ | }$

For a good range of L(s) values above and below 1, make  $R_E = \sqrt{R_{E_{\rm max}} \times R_{E_{\rm min}}} = \sqrt{375 \times 1500} = 750$  at (L(s)=1, which corresponds to  $r_{\rm ds}$  = 1500 $\Omega$  and

$$V_C = 2V_P (1 - (R_{ON}/r_{ds})) = 2 \times (-5.8) \times (1 - (500/1500)) = -7.73V$$

Let  $R_F = 10 \times R_E = 10 \times 750 = 7,5$ K to keep V<sup>+</sup> and the JFET operating at low  $v_{ds} = V^+$  to keep the distortion down. We sould use  $v_{ds} < 0,5$ V if possible to maintain a low THD.

$$V^{+} = v_{ds} = V_{out} \times R_{E} / (R_{E} + R_{E}) = 4 \times 750 / (750 + 7500) = 0.364 V_{P}$$

2. Calculation of R<sub>1</sub>, C<sub>1</sub>, R<sub>2</sub> and C<sub>2</sub> for frequency and loop gain.

$$\left(1 + \frac{R_F}{R_E(VAR)}\right) = \left(1 + \frac{C_2}{C_1} + \frac{R_1}{R_2(VAR)}\right) = \left(2 + \frac{R_1}{R_2(VAR)}\right) \quad for \quad C_1 = C_2 \quad therefore \quad \frac{R_1}{R_2(VAR)} = \frac{R_F}{R_E(VAR)} - 1$$

$$\frac{R_1}{R_2(VAR)} = \frac{7500}{750} - 1 = 9 \quad \Rightarrow \quad R_1 = 9R_2 \quad \omega_n^2 = \frac{1}{R_1 R_2 C_1 C_2} = \frac{1}{9C^2 R_2^2} \quad \Rightarrow \quad CR_2 = \frac{1}{3\omega_n}$$

$$CR_2 = \frac{1}{3\omega_n} = \frac{1}{3 \times 2\pi \times 5000} = 10,61 \, \mu s \qquad R_2 = 3K, \, C = 10,61 \, \mu/3K = 3,54 \, nF \, (3,6 \, nF \, std)$$

$R_1 = 9 * 3K = 27K$  (std)  $R_2 = 2K$  fixed + 2K pot for trimming of frequency.

Calculation of R<sub>D</sub>, C<sub>D</sub>, R<sub>A</sub>, R<sub>B</sub> and C<sub>B</sub> for ripple voltage, time constant and stability 3.

Let the ripple

$$\Delta V_{\rm d}$$

= 10 mV<sub>pp</sub> for low THD of O/P sinewave:

$$R_{\rm D}C_{\rm D} = \frac{V_{\rm REF}}{F\Delta V_{\rm PID}} = \frac{3.3}{5000\times 10m} = 66~ms \qquad {\rm C_D} = 0.1~\mu{\rm F, R_D} = 660{\rm K}~(680{\rm K~std})$$

$R_AC_B < R_DC_D/25$  = 2,72 ms for a "stable" AGC loop and  $(2\pi R_B~C_B)^{\text{-1}} < F_{\mbox{OSC}}$  or  $R_B~C_B > 31.8~\mu s$ Let  $C_B = 0.1 \mu F$ ,  $R_B > 31.8 \mu / 0.1 \mu = 318$  and  $R_A < 2.72 m / 0.1 \mu = 27.2 K$ Let  $R_A = 10K$  and  $R_B = 1K$  which will attenuate the ripple 10X going through the error amplifier.

#### Zener Reference

Bias Zener at 10% of I<sub>z</sub>max, that is I<sub>z</sub>= 0,1\*0,5W/3,3V =15,15mA to operate past the "knee" of the I-V curve.  $R_1 = (15-3,3)/15,15m = 772$

5. The 10K-11K voltage divider limits VGS to a range of -7,25V to +0,1V typical-assume V<sub>sat</sub>=±14V

#### **Final Circuit**

The AGC loop may not be stable, if this occurs, change time constants  $R_dC_d$  and/or  $R_AC_B$  for a stable loop.

The design has not been optimised for lowest THD, this can be done by biasing the JFET at  $V_{GS} = V_p/2$  where  $r_{ds} = 2 R_{on} - modify R_{par} \text{ or } R_F \text{ to do}$

The 47 pF cap stabilises the upper op amp when Q1 is ON because the 0,1 µF load seen by the op amp destabilises -ve feedback. Q1 lessens the capacitive load seen by the op amp O/P by (hfe +1) times which makes it easier to stabilise with a smaller cap (47 pF).

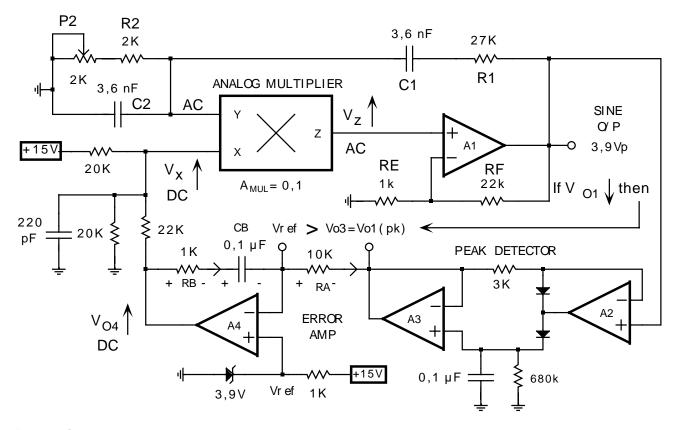

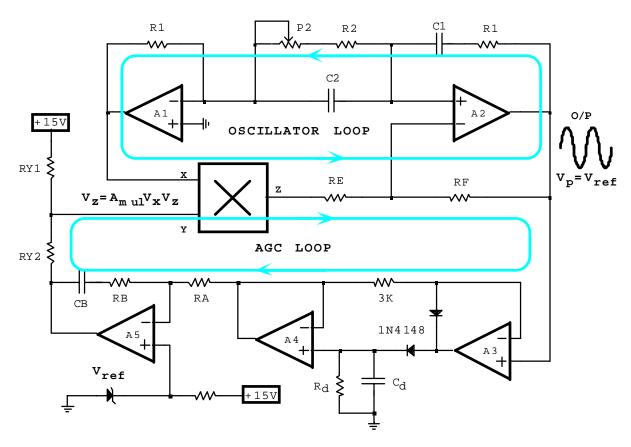

#### AGC LOOP WITH ANALOG MULTIPLIER

#### Loop gain

$$L(S) = \beta_{V} A_{V} = \left( \frac{\frac{S}{R_{1}C_{2}}}{S^{2} + \left(\frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{2}} + \frac{1}{R_{1}C_{2}}\right)S + \frac{1}{R_{1}C_{1}R_{2}C_{2}}} \right) \times \left(A_{MUL}V_{Y}\right) \times \left(1 + \frac{R_{F}}{R_{E}}\right) \qquad \beta_{V} = V_{X}/V_{O}$$

Replacing S with  $j_{\omega}$  we obtain the loop gain  $L(j_{\omega})$  as a function of frequency. One can show that the loop gain will have a phase angle of 0° at the following frequency:

$$\omega_n = \frac{1}{\sqrt{R_1 C_1 R_2 C_2}} \quad where \quad \beta_V A_V = \left(1 + \frac{R_1}{R_2} + \frac{C_2}{C_1}\right)^{-1} \times \left(A_{MUL} V_X\right) \times \left(1 + \frac{R_F}{R_E}\right)$$

The circuit will oscillate at  $\omega_n$  if the loop gain is appropriate and the starting conditions are respected. The AGC loop gain is regulated by adjusting  $V_X$  which is a DC voltage that sets the AC gain of the analog multipler, that is  $V_Z = (A_{\text{MUL}} \ V_{X(DC)})^* \ V_{Y(AC)}$ . Now  $V_X$  is adjusted automatically such as to force  $V^- = V^+$  in op amp A4.  $V^- = V_{O1}(\text{pk})$  and  $V^+ = V_{\text{ref}}$  of the zener diode. If  $V_{O1}$  goes down for some reason or another, then  $V_{\text{ref}} > V_{O1}$  and  $I_{\text{RA}} = (V_{\text{ref}} - V_{O1})/R_A$  will charge  $C_B$  up and automatically increase  $V_{O4}$  which in turn will increase  $V_X(DC)$  and the loop gain will rise above 1V/V thereby increasing  $V_{O1}$  until  $V_{O3}$  (which equals  $V_{O1}$ ) reaches the  $V_{\text{ref}}$  level and knock  $I_{\text{RA}}$  back to 0A and  $V_{O1}$  has stabilised at  $V_{O1} = V_{\text{ref}} = V_{\text{zener}}$ .  $V_X(DC)$  should be chosen as the midrange value of the  $V_X$  range.  $V_X$  min should not be too close to 0V because one risks  $V_X$  going -ve which would add an extra 180° to the oscillator loop and kill the oscillations right away. The

two 20K and the 22K resistors at the O/P of A4 set the range of  $V_X$  to +0,78V to +9,5V assuming  $V_{sat}$  = ±14V for A4. The maximum of +9,5V was picked not to go too close to  $V_X$ (max) specified for the analog multiplier. Therefore  $V_X$  mid = (0,78+9,5)/2 = 5,14V should be used to set the AGC loop gain to 1V/V which results in a loop gain ranging from 0,15 to 1,85 V/V. When  $V_{01}$  is too large one wants a loop gain less than one to lower  $V_{01}$  and when  $V_{01}$  is too small one wants a loop gain greater than one to increase  $V_{01}$ .

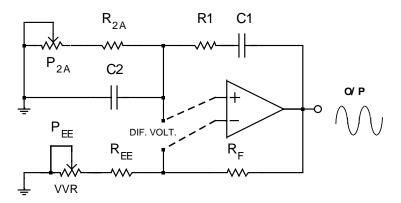

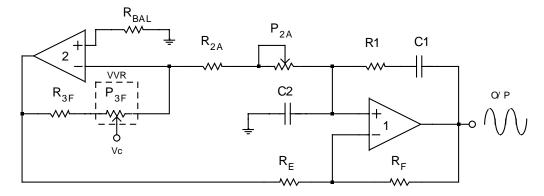

#### 4. WIDE RANGE WIEN BRIDGE OSCILLATOR

## Basic circuit

$P_{2A}$  allows wide range frequency tuning which cannot be obtained with the basic Wien bridge oscillator because of the loop gain variation occurring when  $P_{2A}$  is varied - loop gain variation causes amplitude variation of output and stops the oscillations when loop gain falls below unity.

The above circuit compensates for loop gasin variations encountered in the basic Wien oscillator. As  $P_{2A}$  decreases,  $\beta_V$  goes down but op amp #2 amplifies the feedback voltage ( $V_1^- = \beta_V V_{o1}$ ) by a gain of  $A_{V2} = -R_3/R_2$  which increases as  $R_2 = R_{2A} + P_{2A}$  goes down thus keeping the loop gain constant in spite of  $R_2$  variations.

$$L(S) = \beta_{V} A_{V} = \left( \frac{\frac{S}{R_{1}C_{2}}}{S^{2} + \left(\frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{2}} + \frac{1}{R_{1}C_{2}}\right)S + \frac{1}{R_{1}C_{1}R_{2}C_{2}}} \right) \times \left[ 1 + \left(\frac{R_{F}}{R_{E}} \times \left(1 + \frac{R_{3}}{R_{2}}\right)\right) \right] \qquad \beta_{V} = V_{1}^{+} / V_{O1}$$

Replacing S with  $j\omega$  we obtain the loop gain  $L(j\omega)$  as a function of frequency. One can show that the loop gain will have a phase angle of 0° at the following frequency:

$$\omega_{n} = \frac{1}{\sqrt{R_{1}C_{1}R_{2}C_{2}}} \quad where \quad \beta_{V}A_{V} = \left(1 + \frac{R_{1}}{R_{2}} + \frac{C_{2}}{C_{1}}\right)^{-1} \times \left[1 + \left(\frac{R_{F}}{R_{E}} \times \left(1 + \frac{R_{3}}{R_{2}}\right)\right)\right]$$

To simplify the design, make  $C_1 = C_2$  and  $R_E = R_F$ , then you find that for a loop gain of one, one must have  $R_3 = R_1$ .

**NOTE:** The output sinewave has a very low THD ( < 0,05%) that depends mainly on the linearity of the analog multiplier which usually exhibits better linearity with smaller signals. The second factor affecting THD is the ripple voltage at the O/P of the peak detector which feeds back into the Y input of the multiplier thereby distorting the sine wave.

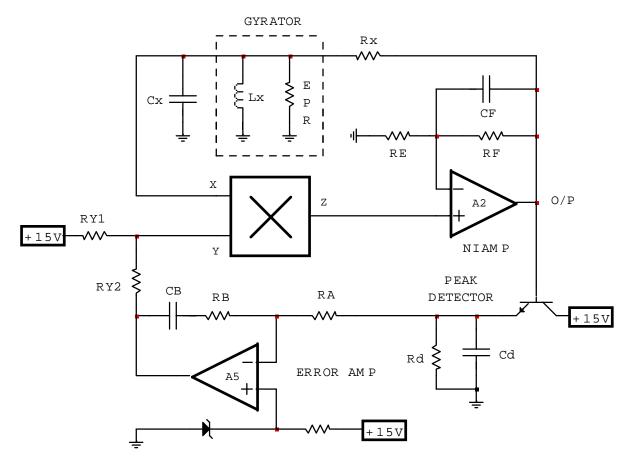

# 5. LC OSCILLATOR WITH AGC LOOP

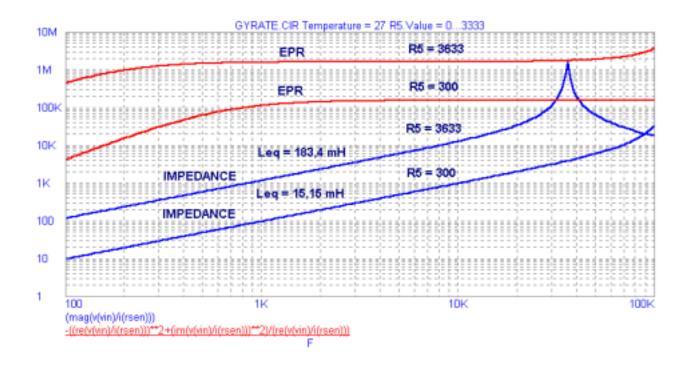

The loop gain at resonance of  $L_x$  and  $C_X$  is given by the following:

$$L(j\omega_n) = \frac{EPR}{EPR + R_X} \times \left(1 + \frac{R_F}{R_E}\right) \times A_{MUL}V_Y = 1 / 0^o \quad and \quad \omega_n = \frac{1}{L_X C_X}$$

The Equivalent Parallel Resistance (EPR) of the gyrator that simulates the inductor  $L_X$  using the op amp circuit shown on the next page has to be determined by simulation as shown on the next page. If the op amps were ideal, the EPR would be infinite and the inductor would be ideal - no losses.

Note: The EB junction reverse breakdown voltage is normally low, between 5V and 10V, for most transistors, thereforeif there is a risk that the EB junction goes into avalanche breakdown, add a diode in series with the emitter or simply replace the transistor for one that has a high breakdown voltage.

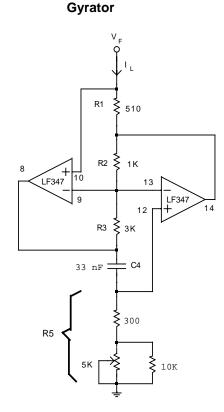

## Simulation of inductor with gyrator

## **Gyrator equations**

Assuming <u>ideal op amps</u>, we can derive the following equation for the gyrator:

$$Z_{GYR(ideal)} = \frac{Z_1Z_3Z_5}{Z_2Z_4} = \frac{R_1R_3R_5}{R_2\left(\frac{1}{j\omega C_4}\right)} \quad \text{Unideal Gyrator}$$

$$Z_{GYR(actual)} = j\omega\left(\frac{R_1R_3R_5C_4}{R_2}\right) \|EPR$$

$$Z_{GYR(actual)} = \left(j\omega\ L_{EQ}\right) \|EPR$$

$$where \quad L_{EQ} = \frac{R_1R_3R_5C_4}{R_2}$$

Theoretically, the gyrator simulates a pure inductor in the present application. However, in practice, as frequency increases, the op amps' voltage gain decreases and is no longer ideal and this implies that  $Z_{\rm GYR}$  is not purely inductive but has some Equivalent Parallel Resistance (EPR) at high frequency.

### 6. L-C REACTANCE COUPLED OSCILLATORS

### **Basic equations**

FEEDBACK IMPEDANCE

To a serious process of the serious process of t

$Z_1$ ,  $Z_2$  and  $Z_3$  will be reactive components, that is capacitors, inductors, combination of both or a crystal. The above amplifier model is used to derive a single formula that will apply to both inverting and non-inverting amplifiers.  $Z_3$  is the feedback impedance and  $Z_2$  will be assumed much smaller than  $R_0$  of the amplifier.

$$\begin{split} V_{o} &= -A_{i} \times i_{in} \times \left[ R_{o} \| Z_{2} \| \left( Z_{3} + Z_{1} \| R_{in} \right) \right] \approx -A_{i} \times \frac{V_{in}}{R_{in}} \times \left[ Z_{2} \| \left( Z_{3} + Z_{1} \| R_{in} \right) \right] \\ A_{V} &= \frac{V_{o}}{V_{in}} = -\frac{A_{i}}{R_{in}} \times \left[ Z_{2} \| \left( Z_{3} + Z_{1} \| R_{in} \right) \right] \quad or \quad A_{V} &= \frac{V_{o}}{V_{in}} = -Y_{m} \times \left[ Z_{2} \| \left( Z_{3} + Z_{1} \| R_{in} \right) \right] \\ \beta_{V} &= \frac{V_{F}}{V_{o}} = \frac{Z_{1} \| R_{in}}{\left( Z_{3} + Z_{1} \| R_{in} \right)} \quad \Rightarrow \quad L(S) = \beta_{V} A_{V} = -\frac{A_{i}}{R_{in}} \times \frac{Z_{2} \left( Z_{1} \| R_{in} \right)}{\left( Z_{1} \| R_{in} \right) + Z_{2} + Z_{3}} \end{split}$$

Simplifying we obtain the following expression:

The circuit will oscillate very near the series resonant frequency of  $Z_1$ ,  $Z_2$  and  $Z_3$ .

$$L(S) = \beta_{V} A_{V} = -\frac{A_{i} Z_{1} Z_{2}}{R_{in} (Z_{1} + Z_{2} + Z_{3}) + Z_{1} (Z_{2} + Z_{3})}$$

$$L(S) = \beta_{V} A_{V} = -\frac{Y_{m} R_{in} Z_{1} Z_{2}}{R_{in} (Z_{1} + Z_{2} + Z_{3}) + Z_{1} (Z_{2} + Z_{3})}$$

For lossless components, we have  $Z_1 + Z_2 + Z_3 = 0 \Longrightarrow Z_2 + Z_3 = -Z_1$

For lossy components, we have  $Z_1 + Z_2 + Z_3 = ESR_{tot} \Rightarrow Z_2 + Z_3 = ESR_{tot} - Z_1$

#### For BJT transistors

With lossless components:  $L(S) = \frac{A_i Z_2}{Z_1}$

With lossy components:

$$L(S) = \frac{-A_{i} Z_{1}Z_{2}}{R_{in}ESR_{tot} + Z_{1}(ESR_{tot} - Z_{1})}$$

## For FET transistors

With lossless components:  $L(S) = \frac{Y_m R_{in} Z_2}{Z_1}$

With lossy components: (and Rin very large)

$$Z_{1} + Z_{2} + Z_{3} = ESR_{tot} \Rightarrow Z_{2} + Z_{3} = ESR_{tot} - Z_{1}$$

$$L(S) = \frac{-Y_{m}Z_{1}Z_{2}}{ESR_{tot} + Z_{1}(ESR_{tot} - Z_{1})/R_{in}} \approx \frac{-Y_{m}Z_{1}Z_{2}}{ESR_{tot}}$$

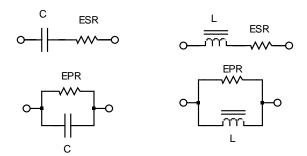

#### Lossy reactances

Actual capacitors and inductors have losses which are often defined with a Q factor. Losses can be represented either by an equivalent series resistor (ESR) or an equivalent parrallel resistor (EPR).

$$Q_{SER} = \frac{X_{SER}}{ESR} \Longleftrightarrow Q_{PAR} = \frac{EPR}{X_{PAR}}$$

# Types of oscillators

1st case

A<sub>i</sub> or  $Y_m$  is +ve  $Z_1$  and  $Z_2$  must be the same type of reactance (both capacitive or both inductive) in order to obtain 0° phaseshift in the loop gain. This also means that  $Z_3$  must be the opposite type of reactance in order to have series resonance  $Z_1+Z_2+Z_3=0$

2nd case

$A_i$  or  $Y_m$  is -ve  $Z_1$  and  $Z_2$  must be opposite types of reactance (one capacitive and the other inductive) in order to obtain  $0^\circ$  phaseshift in the loop gain.  $Z_3$  can be either type of inductance to series resonate  $Z_1+Z_2+Z_3=0$

# Impedance configuration for +ve A<sub>i</sub> or Y<sub>m</sub>

| Туре         | Z1 (input) | Z2 (output) | Z3 (feedback)  |  |  |

|--------------|------------|-------------|----------------|--|--|

| Colpitts     | C1         | C2          | L3             |  |  |

| Hartley      | L1         | L2          | C3             |  |  |

| Clapp        | C1         | C2          | Series L3-C3   |  |  |

| Ultra-Audion | C1         | C2          | Parallel L3-C3 |  |  |

| Pierce       | C1         | C2          | Crystal        |  |  |

# Impedance configuration for -ve A<sub>i</sub> or Y<sub>m</sub>

| Туре         | Z1 (input) | Z2 (output) | Z3 (feedback)  |

|--------------|------------|-------------|----------------|

| Colpitts     | C1         | L2          | C3             |

| Hartley      | L1         | C2          | L3             |

| Clapp        | C1         | L2          | Series L3-C3   |

| Ultra-Audion | C1         | L2          | Parallel L3-C3 |

| Pierce       | C1         | Crystal     | C3             |

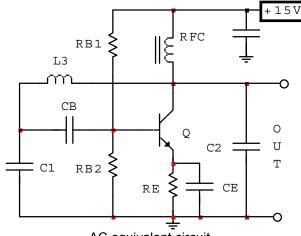

## **Example: Common emitter Colpitts oscillator**

Design a Colpitts oscillator for a frequency of 1MHz. Bias transistor at  $I_C$  = 2 mA,  $V_{CE}$  =10,6V

Transistor data:  $h_{ib}$  at 1 mA = 28 $\Omega$ ,  $h_{fe}$  > 75  $C_{in}$  = 10 pF,  $C_{out}$  = 5 pF

**Solution:**  $R_{B1} = 20K$ ,  $R_{B2} = 10K$ ,  $R_F = 2.2K$

Assuming lossless reactances, we have:

$$L(S) = A_i \frac{Z_2}{Z_1} = A_i \frac{C_1}{C_2} = \frac{C_1}{C_2} \times \frac{h_{fe}}{1 + \frac{h_{ie}}{R_{BI} \| R_{B2}}}$$

$$A_{i} = \frac{i_{o}}{i_{in}} = \frac{i_{c}}{\frac{V_{F}}{R_{in}}} = \frac{i_{c}}{\frac{V_{be}}{R_{in}}} = \frac{i_{c}}{\frac{i_{b}h_{ie}}{R_{in}}} = \frac{i_{c}R_{in}}{i_{b}h_{ie}}$$

$$A_{i} = h_{fe} \times \frac{R_{B1} \| R_{B2} \| h_{ie}}{h_{ie}} = \frac{h_{fe}}{1 + \frac{h_{ie}}{R_{B1} \| R_{B2}}}$$

$$h_{ie} = (h_{fe} + 1)h_{ib} = 76 \times 28 / 2 = 1024 \text{ min}$$

AC equivalent circuit

The circuit will oscillate at the series resonant frequency where  $Z_1+Z_2+Z_3=0$ . Stray capacitance  $C_{in}$  of transistor must be lumped with  $Z_1$  and  $C_0$  with  $Z_2$ .

$$\frac{1}{j\omega(C_1 + C_{in})} + \frac{1}{j\omega(C_2 + C_o)} + j\omega L_3 = 0 \Rightarrow j\omega L_3 = \frac{-1}{j\omega} \left( \frac{1}{(C_1 + C_{in})} + \frac{1}{(C_2 + C_o)} \right)$$

$$\omega_n = \sqrt{\frac{1}{L_3} \left( \frac{1}{(C_1 + C_{in})} + \frac{1}{(C_2 + C_o)} \right)}$$

Let us use  $C_1$  and  $C_2$  values that are much higher than the stray capacitances of the transistor in order to desensitise the resonant frequency with respect to the stray capacitances. We must also consider the Q factor of the resonant circuit in the design. The larger the Q, the less noisy the oscillator will be which results in narrower spectral rays. The Q of  $C_1$ ,  $C_2$  and  $C_3$  can be selected high (given in data sheets) but if  $C_3$  of the amplifier is too low, then the circuit Q will be too low. Let  $C_3$  and  $C_4$  or  $C_5$  of or a good sinewave at  $C_7$  of the amplifier is too low, then the circuit Q will be too low.

$$C_{1} \rangle (2\pi \times 1M \times 887, 7/10)^{-1} = 1,79 \text{ nF}$$

$$L(S) = \frac{C_{1}}{C_{2}} \times \frac{h_{fe}(\min)}{1 + \frac{h_{ie}}{R_{ni} \parallel R_{mi}}} \rangle 1 \frac{0}{0} \Rightarrow L(S) = \frac{C_{1}}{C_{2}} \times \frac{75}{1 + \frac{1064}{20 \text{ k} \parallel 10 \text{ k}}} = 64,7 \times \frac{C_{1}}{C_{2}}$$

Let L(S) =3 to make sure there is enough loop gain - losses not accounted for in above formula.

**NOTE:** The higher L(S) is, the higher  $v_C$  is and the higher the distortion is in the  $v_C$  waveform.

Let

$$C_1 = 3,3nF$$

$L(S) = 64,7 \times \frac{C_1}{C_2} = 3 \Rightarrow C_2 = \frac{64,7 \times 3,3n}{3} = 71,2 \ nF \Rightarrow 68 \ nF \ std$

NOTE: Decreasing ratio  $C_2/C_1$  by factor of N will make loop gain N times larger.

$$L_{3} = \frac{1}{\omega_{n}^{2}} \left( \frac{1}{(C_{1} + C_{in})} + \frac{1}{(C_{2} + C_{o})} \right) = \frac{1}{(2 \times \pi \times 1M)^{2}} \left( \frac{1}{(3,3n+10p)} + \frac{1}{(68n+5p)} \right) = 8,05 \,\mu\text{H}$$

Let us calculate the output impedance and the circuit Q assuming a Q = 150 for the inductor and Q = 300 for the capacitors. ESR of components is given by X / Q.

$$Z_{out} = 3,02\Omega \ \underline{/-52,1^{\circ}} \ , \ \ Q_{CIR} = X_{L}/ESR_{tot} = X_{C}/ESR_{tot} = 50,58/(3,025+0,008) = 16,7 > 10 - OK!$$

RFC: Make  $X_L > 100$  x  $Z_{out}$  so that the resonant circuit is not loaded by the RF choke.  $X_L = 100$  x 3,02 = 302Ω, L > 302/(2\*π\*1M) = 48 μH, let L = 100 μH

Bypass cap: make  $X_C < (X_{Ch}/100) = 6,28$  to attenuate HF so it does not cause stray feedback on supply rail.  $C > 1/(2^* \pi^* 1 M^* 6,28) = 25.3$  nF let  $C = 0.22 \mu F$

<u>Emitter bypass cap:</u> Make  $X_C < h_{ib} / 10 = 1.4\Omega$ ,  $C > 1/(2*\pi*1M*1.4) = 0.11 \mu F$  let  $C_E = 0.22 \mu F$

Base coupling cap: Make  $X_C < R_{in}$  / 10 = 88.8,  $C > 1/(2^*\pi^*1M^*91.7)$  = 1.75 nF let  $C_E = 0.01~\mu F$

Final circuit: 1 MHz Colpitts oscillator

Exact loop gain check

$$L(S) = \frac{-A_i Z_1 Z_2}{R_{in}ESR_{tot} + Z_1 \left(ESR_{tot} - Z_1\right)} \Rightarrow \frac{-64,7 (0,161 - j48,23)(7,8m - j2,34)}{917,5 \times 0,506 + (0,161 - j48,23)(0,506 - (0,161 - j48,23)(0,5$$

This is lower than the design value of 3 because of the losses in the components - we used the approximate loop gain equation for the design. Non-linearity of the EB junction will regulate the loop gain to one.

$C_E$  and the RF choke (100  $\mu$ H) are critical for stability of the loop gain regulation mechanism and may have to be changed for a stable output amplitude. The amplitude of the output voltage is proportional to the loop gain. If  $R_E$  is decreased, L(S) increases and  $V_O$  goes up with a higher THD.

# **Example: Common source Colpitts oscillator**

Design a Colpitts oscillator for a frequency of 1MHz. Bias transistor at  $V_{GS}$  = 0V for maximum transistor gain ( $Y_{fs}$  max).

Transistor 2N5486 data (typical)

$$\begin{split} I_{DSS} &= 10 \text{ mA, V}_{P} = -3.5 \text{V} \\ Y_{fs} &= 5.5 \text{ mS at V}_{GS} = 0 \text{V,} \\ C_{iss} &= 3.5 \text{ pF, } C_{oss} = 1.5 \text{ pF} \end{split}$$

$$L(S) = \beta_{V} A_{V} = -Y_{m} \times \frac{Z_{2}(Z_{1} || R_{in})}{(Z_{1} || R_{in}) + Z_{2} + Z_{3}} \approx -Y_{m} \times \frac{Z_{1} Z_{2}}{Z_{1} + Z_{2} + Z_{3}} = \frac{-Y_{m} Z_{1} Z_{2}}{ESR_{tot}}$$

$Z_1$ ,  $Z_2$  and  $Z_3$  will resonate, total series reactance will be zero and we are left with the total ESR that accounts for losses of the three impedances.

$$\omega_n = \sqrt{\frac{1}{L_3} \left( \frac{1}{(C_1 + C_{in})} + \frac{1}{(C_2 + C_o)} \right)}$$

$$\frac{1}{j\omega(C_1+C_{in})} + \frac{1}{j\omega(C_2+C_o)} + j\omega L_3 = 0 \Rightarrow j\omega L_3 = \frac{-1}{j\omega} \left( \frac{1}{(C_1+C_{in})} + \frac{1}{(C_2+C_o)} \right)$$

$$L(S) = \frac{-Y_m Z_1 Z_2}{ESR_{tot}} = \frac{Y_{fs}}{\omega_n^2 C_1 C_2 ESR_{tot}} \quad but \quad \omega_n^2 C_1 C_2 = \frac{C_1+C_2}{L_3} \quad therefore \quad L(S) = \frac{Y_{fs} L_3}{\left(C_1+C_2\right) ESR_{tot}} \times \frac{\omega_n}{\omega_n}$$

$$L(S) = \frac{Y_{fs}}{\omega_n \left(C_1+C_2\right)} \times \frac{\omega_n L_3}{ESR_{tot}} = \frac{Y_{fs} Q_{tot}}{\omega_n \left(C_1+C_2\right)} \rangle 1 / \frac{0^o}{\omega} \Rightarrow \left(C_1+C_2\right) \left\langle \frac{Y_{fs} Q_{tot}}{\omega_n} \right\rangle$$

$$worst \quad case \quad \left(C_1+C_2\right) \left\langle \frac{Y_{fs} (\min) Q_{tot} (\min)}{\omega_n} \right\rangle$$

$$(C_1 + C_2) \left\langle \frac{Y_{fs}(\min)Q_{tot}(\min)}{\omega_n} \right| = \frac{1m \times 50}{2\pi \times 1M} = 8 \ nF \quad let \quad C_1 + C_2 \approx 4nF \quad and \quad C_2 / C_1 \approx 10$$

$$C_1 + C_2 = 11 \ C_1 \approx 4 \ nF \quad C_1 = 364 \ pF \ (330 \ pF \ std) \quad and \quad C_2 = 3,3 \ nF$$

**NOTE**: A larger C<sub>2</sub> value entails a low Z<sub>0</sub> and less "frequency pulling" by the load.

$$\mathbf{\omega}_{n}^{2} = \frac{1}{L_{3}} \left( \frac{1}{(C_{1} + C_{in})} + \frac{1}{(C_{2} + C_{o})} \right) \approx \frac{1}{L_{3}} \left( \frac{1}{C_{1}} + \frac{1}{C_{2}} \right)$$

$$L_{3} = \frac{1}{\mathbf{\omega}_{n}^{2}} \left( \frac{1}{C_{1}} + \frac{1}{C_{2}} \right) = \frac{1}{(2\pi \times 10^{6})^{2}} \left( \frac{1}{330 p} + \frac{1}{3,3 n} \right) = 84,4 \,\mu H$$

Again if we assume a Q of 150 for the inductors and 300 for the capacitors, the resonant circuit Q is 95,9 also taking into account the 1M resistor losses. This is a lot higher than the BJT oscillator and yields a less noisy O/P.

## 7. Crystal Oscillators

### **Crystal Characteristics**

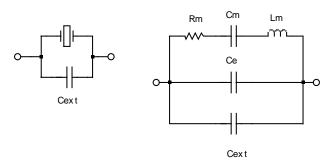

Rm5 Cm/5 Lm/5

Rm3 Cm/3 Lm/3

R + jx

Rm Cm Lm

Rm Cm Lm

N

Ce

Ce

C -jx

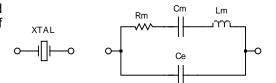

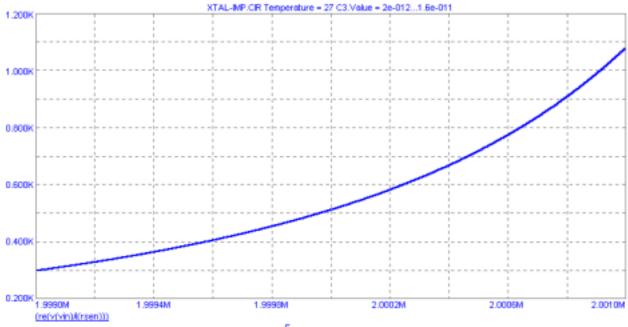

$L_M$ ,  $C_M$  and  $R_M$  are the electrical equivalents of the crystal mechanical resonator at the fundamental resonant frequency. The values of  $L_M$ ,  $C_M$  amd  $R_M$  depend on the mechanical properties of the crystal and the way it has been cut.  $C_e$  accounts for the electrical capacitance of the crystal electrodes and its holder parasitic capacitance.  $R_M$  represents the energy losses in the crystal. A mechanical resonator can also resonate at odd harmonic frequencies (or overtones) of the fundamental frequency - the equivalent  $C_M$  and  $L_M$  values are not necessarily divided exactly by a factor of N.

## Simplified model for fundamental mode operation

The equivalent circuit of the crystal can be reduced to two branches to study the fundamental mode of operation.

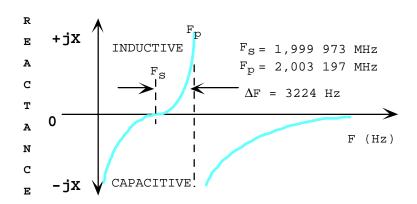

#### Crystal impedance

$$\frac{1}{SC_{e}} \left\| \left[ R_{m} + SL_{m} + \frac{1}{SC_{m}} \right] \frac{1}{to} \left( \omega_{p}^{2} c_{e}^{2} R_{m} \right)^{-1} \right\| \\

\frac{1}{SC_{e}} \times \left[ \frac{S^{2} + \frac{R_{m}}{L_{m}} S + \frac{1}{L_{m}C_{m}}}{S^{2} + \frac{R_{m}}{L_{m}} S + \frac{1}{L_{m}} \left( \frac{1}{C_{m}} + \frac{1}{C_{e}} \right) \right] \qquad 0^{\frac{R_{m}}{2}} \\

= \frac{1}{SC} \times \left[ \frac{S^{2} + 2\zeta_{S}\omega_{S}S + \omega_{S}^{2}}{S^{2} + 2\zeta_{S}\omega_{S}S + \omega_{S}^{2}} \right] \qquad -ve$$

Series resonance:

$$\omega_{\rm S} = 1/\sqrt{L_{\rm m}C_{\rm m}}$$

implies  $X_{\rm Lm} = X_{\rm Cm}$  and

$$Z_{\rm X}(j\omega_{\rm S}) = R_{\rm m} \left\| \left( 1/\omega_{\rm S}C_{\rm e} \right) = R_{\rm m} - j\omega_{\rm S}R_{\rm m}^2C_{\rm e} \approx R_{\rm m} \right\|$$

Parallel resonance:

$$\omega_P = \sqrt{\frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e} \right)}$$

implies  $X_{Lm} = X_{Cm} + X_{Ce}$  and

$$Z_X(j\omega_P) = \frac{1}{\omega_P^2 C_e^2 R_m} - \frac{1}{j\omega_P C_e} \approx \frac{1}{\omega_P^2 C_e^2 R_m}$$

Notice that the crystal impedance is inductive only between  $F_S$  and  $F_P$  which is a very narrow range -  $F_S$  and  $F_P$  are very close to each other because  $C_m << C_e$ .

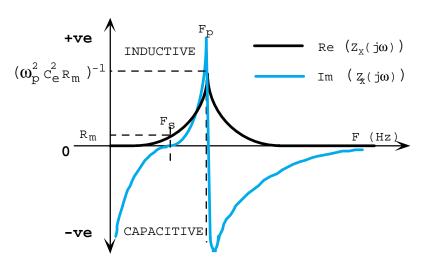

### Effect of external capacitance - series connection

In practice when the crystal is used in a circuit, it is always in the presence of some external capacitance, whether parasitic or actual capacitor, which will slightly shift either the series or parallel resonant frequency of the crystal. When  $C_{\text{ext}}$  is in series with the crystal, the series resonant frequency is shifted as shown by the following expression:

$$Z_{XTAL}(S) + \frac{1}{SC_{ext}} = \frac{1}{S} \left( \frac{1}{C_e} + \frac{1}{C_{ext}} \right) \times \left[ \frac{S^2 + \frac{R_m}{L_m} S + \frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e + C_{ext}} \right)}{S^2 + \frac{R_m}{L_m} S + \frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e} \right)} \right]$$

$$\omega_S = \sqrt{\frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e + C_{ext}} \right)} \qquad \omega_P = \sqrt{\frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e} \right)}$$

One can see that F<sub>P</sub> is not affected by C<sub>ext</sub> when C<sub>ext</sub> is connected in series with the crystal.

As

$$C_{\text{ext}}$$

varies from  $\infty$  to 0,  $\omega_{\text{S}}$  is shifted from  $\omega_{\text{S}} = \frac{1}{\sqrt{L_{\text{m}}C_{\text{m}}}}$  to  $\omega_{\text{S}} = \omega_{\text{P}} = \sqrt{\frac{1}{L_{\text{m}}}\left(\frac{1}{C_{\text{m}}} + \frac{1}{C_{\text{e}}}\right)}$

NOTE: Use of a large  $C_{\text{ext}}$  is not recommended as it increases the amplitude of the mechanical vibrations of the crystal which shifts the crystal frequency and may also break the crystal. Amplitude of voltage across crystal must be low to maintain a low power dissipation (called drive level) which is usually in the XX  $\mu$ W range.

The manufacturer will always specify or calibrate the crystal frequency with a nominal load or external capacitance. If a different external capacitance is used, the accuracy of the crystal is not guaranteed.

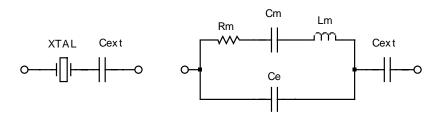

## Effect of external capacitance - parallel connection

One can see that  $F_S$  is not affected by  $C_{ext}$  when  $C_{ext}$  is connected in parallel with the crystal. As  $C_{ext}$  varies from  $\infty$  to 0,  $\omega_P$  is shifted from

$$\omega_P = \sqrt{\frac{1}{L_m C_m}} \quad to \quad \sqrt{\frac{1}{L_m} \left(\frac{1}{C_m} + \frac{1}{C_e}\right)}$$

Same range as F<sub>S</sub> for the series connection.

$$Z_{TOT} = Z_{XTAL}(S) \left[ \frac{1}{SC_{ext}} = \frac{1}{S(C_e + C_{ext})} \times \left[ \frac{S^2 + \frac{R_m}{L_m} S + \frac{1}{L_m C_m}}{S^2 + \frac{R_m}{L_m} S + \frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e + C_{ext}} \right) \right] \right]$$

## **EXAMPLE - 1** Calculation of crystal parameters

A crystal has the following parameters:  $R_m$  = 500 $\Omega$ ,  $L_m$  = 13,084179H,  $C_m$  = 0,484 x 10<sup>-15</sup> F,  $C_e$  = 0,15 pF, F=2,000 000 MHz nominal

A) Determine the series and parallel resonant frequencies of the crystal alone to 1 Hz accuracy.

$$F_{\rm S} = \frac{1}{2\pi\sqrt{L_{\rm m}C_{\rm m}}} = \text{1,999 973 MHz} \qquad F_{\rm P} = \frac{1}{2\pi}\sqrt{\frac{1}{L_{\rm m}}\left(\frac{1}{C_{\rm m}} + \frac{1}{C_{\rm e}}\right)} = \text{2,003 197 MHz}$$

B) Sketch the impedance response assuming the crystal is lossless.  $R_m = 0$ , the impedance is purely reactive.

C) What is the "tuning" range of the crystal if we add external capacitance?

The series or the parallel resonant frequency of the crystal + external capacitor can range from  $F_S$  to  $F_P$  of the crystal alone, that is from 1,999 973 MHz to 2,003 197 MHz, which is a range of 3224 Hz or 0,161 %.

D) What is the series Q factor of the crystal?

$$Q_S = \frac{X_{L_m}}{R_m} = \frac{X_{C_m}}{R_m} = \frac{2\pi \times 1999973 \times 13,084179}{500} = 328837$$

Typical Q values are usually from 10K to 100K but may also be higher.

E) What is nominal load capacitance for which the crystal frequency is specified?

$$\omega_{nom} = \sqrt{\frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e + C_{ext}} \right)} \Rightarrow \omega_{nom}^2 = \frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e + C_{ext}} \right)$$

Solving the above equation we have  $C_{ext} = 18 pF$ .

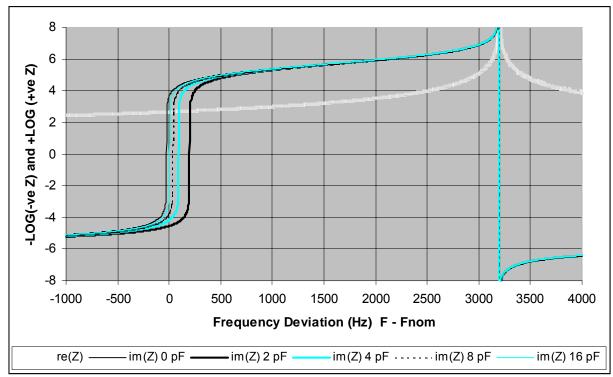

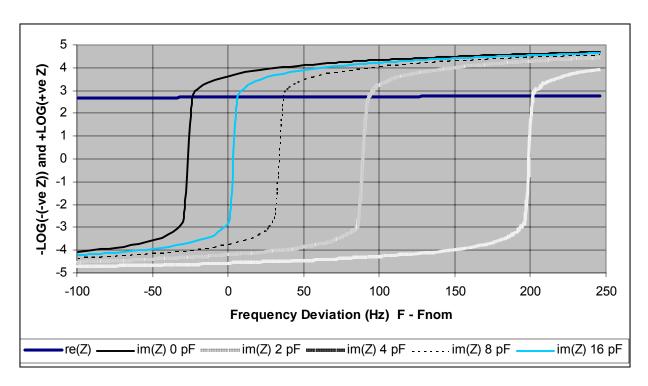

F) Determine the effect of a series  $C_{ext}$  on the real and imaginary parts of  $Z_{tot} = Z_{XTAL} + 1/SC_{ext}$ Do for  $C_{ext} = 0, 2, 4, 8$  and 16 pF - use a spread sheet or mathCAD software.

From the above graph one can see that  $F_S$  is very close to 2,000 000 MHz with  $C_{ext}$  = 16 pF (less than 10 Hz away). As  $C_{ext}$  increases above 16 pF,  $F_S$  can only shift by 27 Hz at the most. As  $C_{ext}$  goes down, the

frequency shift increases exponentially to a max value of  $F_p = \frac{1}{2\pi} \sqrt{\frac{1}{L_m} \left( \frac{1}{C_m} + \frac{1}{C_e} \right)}$

One can see that if  $F_s$  is shifted too much above  $F_{nom}$ , the crystal resistance increases exponentially and this may stop oscillation when the crystal is used in an oscillator.

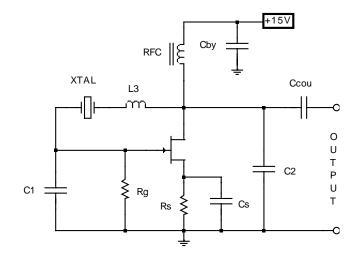

### **EXAMPLE** Design of a Pierce oscillator

Design a Pierce oscillator using the following crystal specifications:

39,000 000 MHz 3rd overtone frequency with 20 pF load capacitance.  $Q_{XTAL} > 10 000$

# Transistor data (typical) 2N5486

$$\begin{split} I_{DSS} &= 10 \text{ mA, } V_{P} = -3.5 V \\ Y_{fs} &= 5.5 \text{ mS at } V_{GS} = 0 V, \\ C_{in} &= 5 \text{ pF, } C_{out} = 2.5 \text{ pF at } V_{GS} = 0 V \end{split}$$

The Pierce oscillator shown is basically a Colpitts oscillator with a crystal. L3 and C2+ $C_{out}$  are tuned at approximately 39 MHz to prevent the crystal from oscillating at the fundamental frequency or at other harmonic frequencies. C1 +  $C_{in}$  =  $C_{LOAD}$  of the crystal for an accurate crystal frequency. To obtain a loop gain greater than unity (see Colpitts example for derivation), we must have

$$(C_1 + C_2) \langle \frac{Y_{fs}(\min) Q_{tot}(\min)}{\omega_n}$$

where C1 includes  $C_{in}$  and C2 includes  $C_{out}$ . We are going to

operate the JFET at  $V_{GS}$  0V, this means  $R_S = 0\Omega$  and  $C_S$  is taken out, where  $Y_{fs}$  is maximum - this is OK for small AC signals only because we do not want to forward bias the gate-channel junction.

$$(C_1 + C_2) \left\langle \frac{Y_{fs \text{ (min)}} Q_{tot \text{ (min)}}}{\omega_n} = \frac{5.5m \times 10\ 000}{2\pi \times 39M} = 0.224\ \mu F$$

for L(j\omega\_n) > 1

The constraint on C1 +C2 will not pose any problems. C1 =  $C_{LOAD}$  -  $C_{in}$  = 20 pF - 5 pF = 15 pF. Let us use  $L_3$  = 0,2  $\mu$ H, a value that can be wired easily on a small plastic form.

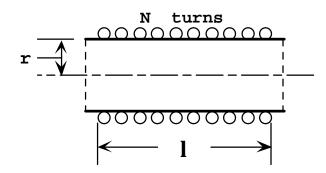

Air-Core Inductor Design

$$L = \frac{0.394 \ r^2 \ N^2}{9 \ r + 10 \ l} \qquad N = \sqrt{\frac{L \times (9 \ r + 10 \ l)}{0.394 \ r^2}}$$

Formula valid only for I > 0,67 r and a single layer of turns.

L: inductance in µH N: number of turns I: length in cm r: coil radius in cm

For maximum Q of the inductor, the length I should be equal to the coil diameter but this is not practical for most applications where we need a fair number of turns which require a longer coil. To obtain a better Q one can use a larger diameter wire which is less resistive. Now to increase the frequency range of the inductor one should leave some space between each turn of wire to reduce the stray capacitance of the coil.

## Different schemes for L = 0,2 µH with AWG#24 wire diam=0,55 mm (21,6 mils)

| r (cm)    | 0,15 | 0,2  | 0,25 | 0,15 | 0,2  | 0,25 | 0,15 | 0,2  | 0,25 |

|-----------|------|------|------|------|------|------|------|------|------|

| I (cm)    | 1    | 1    | 1    | 1,5  | 1,5  | 1,5  | 2    | 2    | 2    |

| N (turns) | 16,0 | 12,2 | 10,0 | 19,2 | 14,6 | 11,8 | 21,9 | 16,6 | 13,4 |

| SPACE(mm) | 0,08 | 0,29 | 0,50 | 0,25 | 0,51 | 0,78 | 0,38 | 0,70 | 1,01 |

The possible schemes allow for enough space between each turn for low stray capacitance. The above calculations assume coated (insulated) wire diameter.

One can also use a metal shield around the inductor to prevent mutual inductance coupling with other components and reduce EMI (ElectroMagnetic Interference). The shield will lower the inductance value somewhat from the unshielded value depending on the geometry of the shield. For instance, an inductor with a circular shield will have the following inductance:

$$L = \left(\frac{0.394 \, r^2 \, N^2}{9 \, r + 10 \, l}\right) \times \left[1 - \frac{\left(\frac{r}{r_s}\right)^2}{1 + \frac{1.55(r_s - r)}{l}}\right]$$

rs: shield radius

$$C_2 + C_{out} = \frac{1}{\mathbf{Q}_p^2 L_2} = \frac{1}{(2\pi \times 39M)^2 0.2\mu} = 83.2 \ pF \Rightarrow C_{out} = 83.2 \ p - 2.5 \ p = 80.7 \ pF$$

82 pF std

Bypass cap: make  $X_C < X_{RFC}/50$  to attenuate RF so it does not cause stray feedback on supply rail.

<u>O/P coupling cap:</u> Make  $X_C \ll R_{LOAD}$  such that it does not cause any attenuation.

Final circuit

**NOTE**: Crystal inductive reactance cancels out  $X_C$  of 15 pF and  $C_{in}$  if value close to  $C_{LOAD}$  and 0,2  $\mu$ H inductor resonates with 82 pF plus  $C_{out}$  to ensure crystal resonates on 3 rd overtone of 39 MHz. The non-linearity of the JFET will regulate the loop gain to one but the output amplitude is unpredictable.

The circuit shown below is the same basic oscillator but with an AGC loop to regulate the output voltage to a known value. The AGC voltage basically varies  $V_{\rm GS}$  of the first JFET which in turn varies  $Y_{\rm fs}$ . and thereby controls its gain for loop gain regulation.