Hi.

I get stuck while reading lecture about LDO.

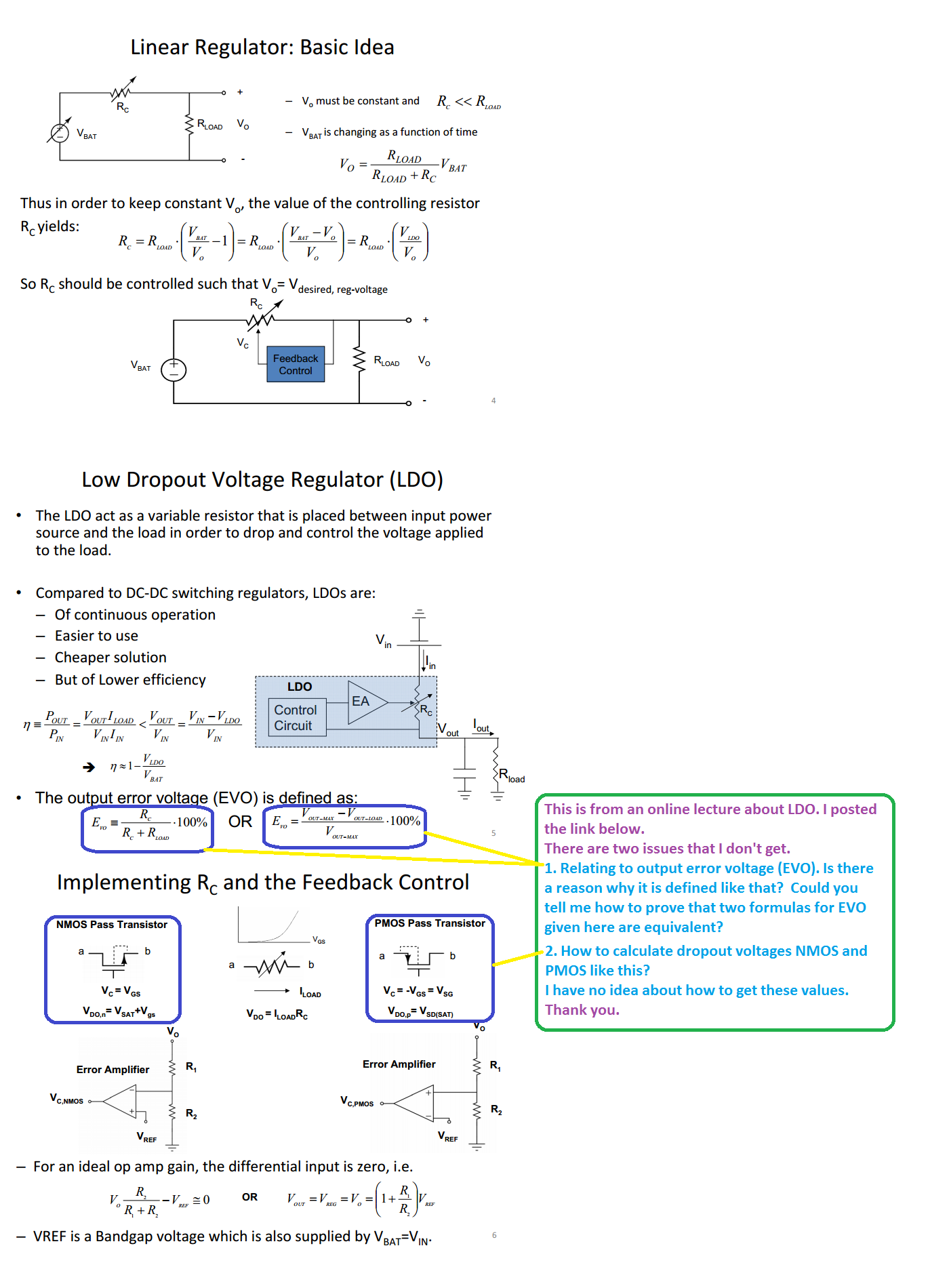

Please help me with questions in the picture below.

Here is the like to the entire lecture:

https://sites.ieee.org/scv-sscs/files/2010/02/LDO-IEEE_SSCS_Chapter.pdf

I get stuck while reading lecture about LDO.

Please help me with questions in the picture below.

Here is the like to the entire lecture:

https://sites.ieee.org/scv-sscs/files/2010/02/LDO-IEEE_SSCS_Chapter.pdf