Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

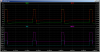

The yellow trace is the relay coil current. The gray trace is the current through the snubber diode. They are equal between 57ms and 90ms. Note that the inductance of the relay coil is what determines the rise and fall time of the coil current. I never met a "power" relay that operates in less than about 25ms. V(out) shows when the relay contacts close/open.To MikeMI: what is Ix (yellow) in your graph? You omit D2 and D3?

Hi MikeMI: impressive! What program do you use for this simulation?

I will make an inverted diagram with a pnp and n-channel i.s.o. an npn as now. As sson as ready I will post it here.

To get TTL output, I think a 4.7 or 5.1V zener with a 2k series resistor between the Q1 collector and ground will upset the C1 functioning. What would you suggest for this addition?

I suggest that a burden resistor be connected across the CT secondary. It becomes the transducer that converts primary current to a secondary voltage...Here is the upside down version, ...

I would connect your proposed CT (with a suitable burden resistor) to your layout. Use an o'scope to view the signal across the burden resistor. Post a picture if you have the ability...... I know, this seems like designing circuits without knowing all prerequisites but sometimes I get taken away by enthusiasm before knowledge

Because Mike added it. I think it can be eliminated.why R3?

Because I focused on a semi-isolated TTL output. Your suggestions is better.why not eliminate Q3 and connect zener D3 with load resistor R4 in series to Q1-collector?

The zener gives a constant output voltage over a range of currents from 0 to around 7 mA.To AnalogKid: for the TTL output, why not use a voltage divider resistor set of about 2k instead of D3, Q3 and R4?

I put the R2/R3 voltage divider there to control the peak gate voltage on the PFET. If running on 12Vdc, without R3, the peak Vgs would approach the supply voltage. That may or may not be ok depending on the PFET.Because Mike added it. I think it can be eliminated.

ok, thank you! Your suggestions will be applied.Because Mike added it. I think it can be eliminated.

Because I focused on a semi-isolated TTL output. Your suggestions is better.

The zener gives a constant output voltage over a range of currents from 0 to around 7 mA.

ak

ok, thanks MikeMI; I think of using FQP30N06L because I have it lying around.I put the R2/R3 voltage divider there to control the peak gate voltage on the PFET. If running on 12Vdc, without R3, the peak Vgs would approach the supply voltage. That may or may not be ok depending on the PFET.

Hi Mike, here is some clarification stating the actual square wave signal (the one I want measured throught the current transformer) has half periods of 58µs for 1 and 100µs for 0 meaning 1/(2 x 0.000058)=8,6KHz to 1/(2 x 0.0001)=5kHz frequency: https://www.dccwiki.com/DCC_PowerI would connect your proposed CT (with a suitable burden resistor) to your layout. Use an o'scope to view the signal across the burden resistor. Post a picture if you have the ability...

I know. Next time I will be better prepared before posting. For example https://www.electro-tech-online.com/threads/optical-4-ch-ldr-object-detection.150999/A lot less than 20 kHz (post #1) but not enough to matter.

ak

I hit an issue with this design: if I want an open collector digital output (referred to here as TTL output), I think I have to use an NPN for Q1; and thus a p-channel OSFET for Q2.